技术摘要:

封装整合多个MTJ接面的STT‑MRAM装置以其能消散由重复读/写程序产生的热量且同时屏蔽邻近装置的外部磁场。另外,可建构封装层以降低已证明会影响DR/R及Hc的顶部引线应力。我们提供一种可同时解决所有此些问题的装置设计及其制备方法。

背景技术:

STT-MRAM正在成为越来越有希望用于替换嵌入式快闪存储器及嵌入式SRAM(静态 随机存取存储器)的下一代非挥发性工作存储器(non-volatile working memory)的候选 者。然而,将此技术缩减至20nm(纳米)尺寸及更小尺寸存在挑战。此一挑战增强了较小MTJ (磁性穿隧接面)装置的热稳定性,MTJ装置是MRAM中使用的一种类型的存储单元。研究已报 导在读/写循环期间发生的MTJ接面的自加热(参见例如,2012年3月S .Chatterjee、 S.Salahuddin、S.Kumar及S.Mukhopadhyay的IEEE Transactions on Electron Device第 59卷第3期;2016年4月Y.Wang、H.Cai、L.Naviner、Y.Zhang、X.Zhao、E.Deng、J.Klein及 W .Zhao的IEEE Transaction on Electron Device第63卷第4期;W .Guo、G .Prenat、 V.Javerliac、M .Baraji、N .Mestier、C .Baraduc、B.Dieny的Journal of Physics D: Applied Physics,IOP,2010,43(21)第215001页。) 随着读/写速度及图案密度两者增加,预期自加热将成为一更大问题。一方面,自 加热可帮助降低开关电流,但另一方面,自加热亦可降低装置热稳定性及甚至装置可靠性。 STT-MRAM的另一挑战是由来自邻近装置的杂散磁场引起的开关干扰。在现有技术中(例如, 在所有以下专利中)已考量与STT-MRAM操作有关的此些及其他问题,诸如非期望应力: 美国专利20150091109(Allinger等人) 美国专利9,024,399(Guo) 美国专利7,262,069(Chung等人) 美国专利申请案2007/0058422(Phillips等人) 美国专利8,194,436(Fukami等人) 美国专利9,081,669(Tadepalli等人) 美国专利8,125,057(Bonin等人) 美国专利7,829,980(Molla等人) 美国专利申请案2006/0273418(Chung等人)。 确实期望有效地解决自加热、热稳定性、应力及开关干扰的问题。若可以一组合且 有效的方式解决此些问题,则将更加有利。尽管上述现有技术已论述此些问题,但其未以如 本公开中的全面、可行且有效的方式解决此些问题。

技术实现要素:

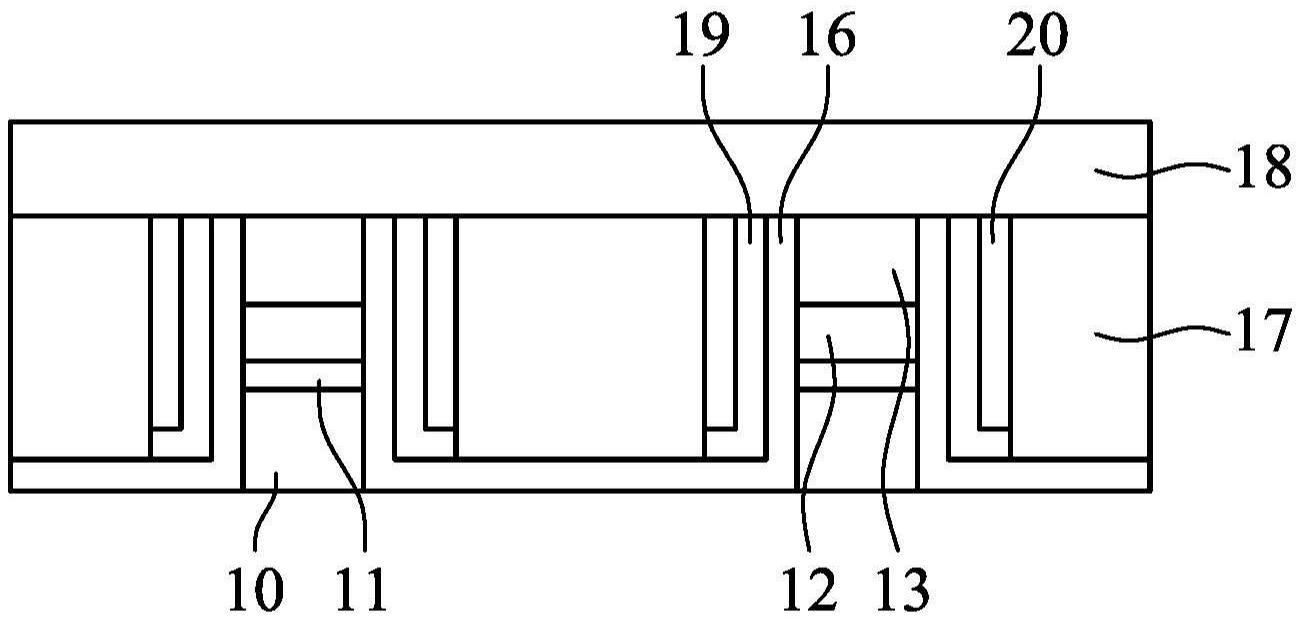

本公开的第一目的是提供一种保护STT-MRAM装置免受不利热效应(诸如起因于由 读/写操作引发的自加热的彼等热效应)的方法。 6 CN 111587493 A 说 明 书 2/5 页 本公开的第二目的是提供一种保护STT-MRAM装置免受邻近装置磁场所致的不利 开关效应的方法。 本公开的第三目的是提供一种用于在STT-MRAM装置的特定区域内降低由不利热 效应引起的应力的机构。 本公开的第四目的是使用相同的散热设计来用作为MTJ装置的应力缓冲器。 本公开的第五目的是提供能够同时产生所有上述目的的方法。 此些目的将通过设计及制备STT-MRAM装置的散热结构来实现,其将改良STT-MRAM 装置的热稳定性。此散热结构将同时用作磁性装置的磁性屏蔽器及应力缓冲器。一项内部 研究已表明,顶部引线应力可影响DR/R及Hc。图1显示此些结果。因此,我们获得相同散热设 计亦可用作为MTJ装置的应力缓冲器的经验证据,其中应力包含本征膜(intrinsic film) 拉力及压缩应力加上由位元(BIT)线与整体堆叠物之间的差异膨胀/收缩引发的应力。 本公开提供一种散热结构设计及其用于MTJ装置(诸如可整合至STT-MRAM装置中 的MTJ装置)的制备方法,使得与使用当前方法制备的MTJ装置相比,这种MTJ装置于读/写循 环期间产生的热量可更快地消散。因此,如此设计及制备的MTJ装置改良了其读/写可靠性。 附图说明 图1a至图1b显示指示顶部引线应力可如何影响DR/R及Hc的数据。 图2列出对应于图4a至图4e中所示出及当前使用的“旧”MTJ制备方案的层名称及 其等功能的表(表1)。 图3列出对应于图4a至图4e中所示出的制备方案的工艺流程步骤的表(表2)。 图4a至图4e显示本公开磁性穿隧接面(MTJ)结构及用来制备其的制备工艺的示意 图。 图5列出对应于图7a至图7f中所示出的本公开披露的制备方案的层名称及其等功 能的表(表3)。 图6列出对应于图7a至图7f中所示出的本公开披露的制备方案的工艺流程步骤的 表(表4)。 图7a至图7f显示本公开披露的磁性穿隧接面(MTJ)结构及用来制备其的制备工艺 的一组示意图。 图8a至图8d显示提供与图7a至图7f中所显示者相同性质的替代磁性穿隧接面 (MTJ)结构及用来制备其的制备工艺的一组示意图。 附图标记说明: 10:钉扎层 11:阻障层 12:自由层 13:第一硬遮罩层/磁性穿隧接面(MTJ)装置 14:第二硬遮罩层 15:光刻胶剂图案层 16:封装层 17:空间填充层间介电质膜(ILD) 7 CN 111587493 A 说 明 书 3/5 页 18:位元线 19:第二封装层/散热层 19a:磁性屏蔽层 20:第三封装层 130,140:界面