技术摘要:

本公开内容的实施方式总体涉及一种层堆叠,所述层堆叠包括电介质层,所述电介质层具有高k值,能够改善半导体显示装置电气性能。在一个实施方式中,所述层堆叠包括基板、设置在所述基板上的沟道层、和栅极绝缘层。所述栅极绝缘层包括设置在所述沟道层上的界面层和设置在 全部

背景技术:

显示装置已被广泛地用于各种电子应用,例如是电视机、监视器、移动电话、MP3播 放器、电子书阅读器、个人数字助理(PDAs)和其类似物。这些显示装置利用集成电路制造, 集成电路在单一芯片上可包括数百万个晶体管、电容器和电阻器。芯片设计的演化不断地 需要更快的电路和更大的电路密度。对具有更大的电路密度的更快的电路的需求对用于构 成这种集成电路的材料提出了对应的需求。特别是,随着集成电路部件的尺寸被减小至亚 微米尺寸(sub-micron scale),现在必须利用低电阻率导电材料和高介电常数绝缘材料, 才能从此类部件获得合适的电气性能。 对减小这些部件的比例的需求导致泄漏和短沟道效应(DIBL)的问题。为了克服泄 漏和DIBL问题,要求所形成的薄膜晶体管(TFTs)具有高电容以用于显示装置。通过改变电 介质材料和/或电介质层的尺寸,可调整电容。例如,当用具有高k值的材料代替电介质层 时,TFT的电容也将增大,如公式Cox=A(k·E0/tox)所提出。然而,将材料改变成具有高k值 的材料可导致沟道区域与电介质层之间的界面问题,从而使装置完全失效。 因此,需要具有高k值且能够改善半导体显示装置的电气性能的电介质层。

技术实现要素:

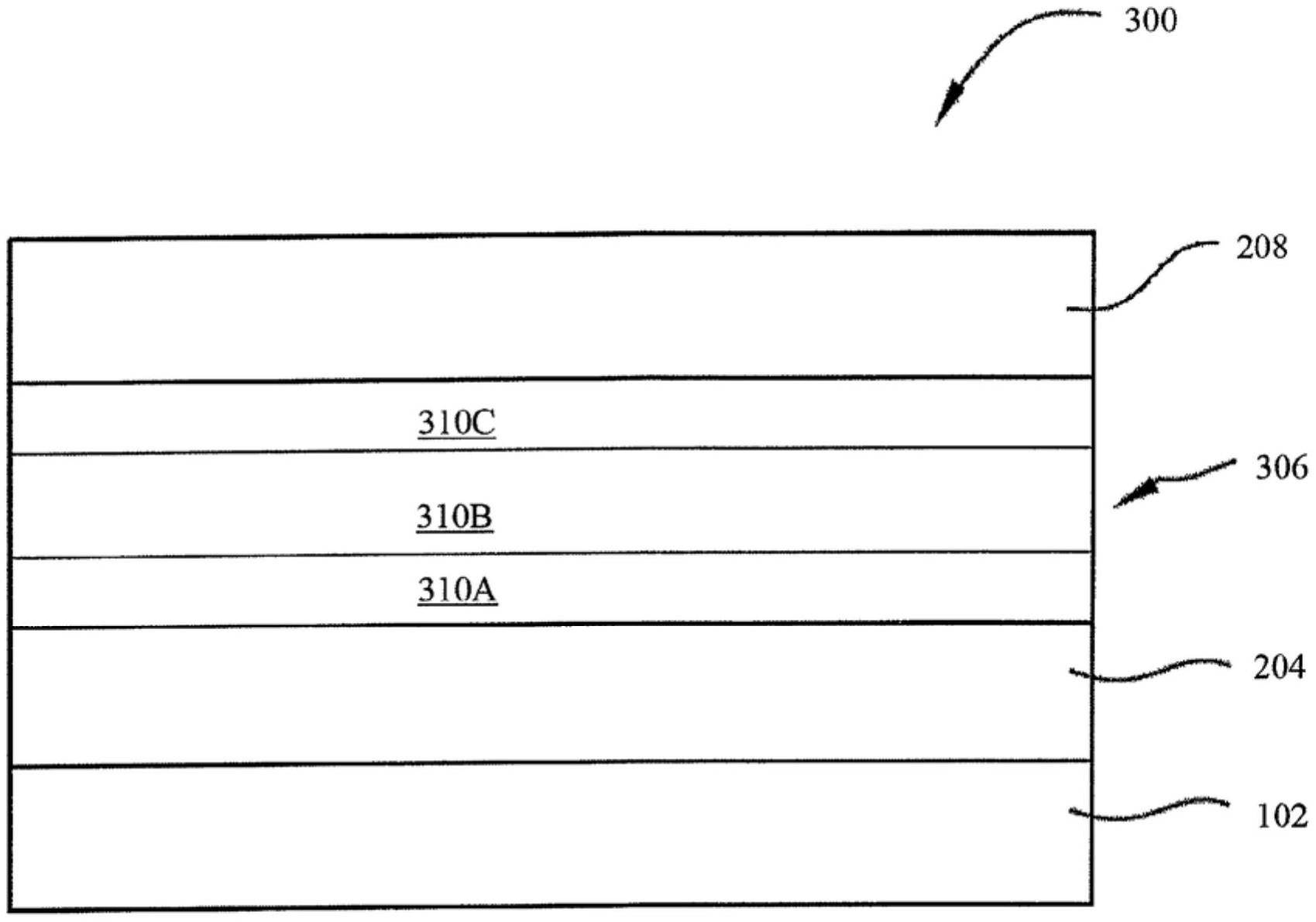

本公开内容的实施方式总体涉及一种层堆叠,该层堆叠包括电介质层,该电介质 层具有高k值,能够改善半导体显示装置的电气性能。在一个实施方式中,该层堆叠包括基 板、设置在该基板上的沟道层和栅极绝缘层。该栅极绝缘层包括设置在该沟道层上的界面 层和设置在该界面层上的二氧化锆层。该栅极绝缘层具有范围为从约20至约50的k值。 在另一个实施方式中,一种层堆叠包括基板、设置在该基板上的沟道层和设置在 该沟道层上的栅极绝缘层。该栅极绝缘层包括第一界面层、第二界面层和二氧化锆层,该二 氧化锆层位于该第一界面层与该第二界面层之间。该栅极绝缘层具有范围为从约20至约50 的k值。 在另一个实施方式中,一种层堆叠包括非晶硅层和设置在该非晶硅层上的栅极绝 缘层。该栅极绝缘层包括设置在该非晶硅层上的二氧化硅层和设置在该二氧化硅层上的二 氧化锆层。该栅极绝缘层具有范围为从约20至约50的k值。 附图说明 为了能够详细地理解本公开内容的上述特征的方式,以上简要地概述的本公开内 容的更特定的描述可通过参照实施方式来获得,实施方式中的一些示出于附图中。然而,应 注意,附图仅示出出本公开内容的典型实施方式,因而不应被视为对本公开内容的范围的 4 CN 111557051 A 说 明 书 2/5 页 限制,因为本公开内容可允许其他等同有效的实施方式。 图1是根据本公开内容的一个实施方式的可用于沉积栅极绝缘层的处理腔室的横 截面图。 图2是根据本公开内容的一个实施方式的层堆叠的横截面图。 图3是根据本公开内容的一个实施方式的层堆叠的横截面图。 为了便于理解,已尽可能地采用相同的附图标号来标示图中共同的相同组件。考 虑到,在没有进一步地描述下一个实施方式的元件和特征可以有利地并入其他实施方式 中。