技术摘要:

本发明涉及一种用于时间交织采样ADC的多相位时钟产生电路,属于时钟产生技术领域,在保证高速的前提下,实现低时钟抖动,低时间偏差和低功耗。电路包括环形压控振荡器、相位跟踪环电路和校准脉冲产生电路;环形压控振荡器与相位跟踪环电路构成PLL环路;环形压控振荡器 全部

背景技术:

模数转换器(Analog-to-Digital Converter,ADC)将连续时间和幅值的信号转换 为数字处理系统中离散时间和量化幅值的信号。ADC已广泛应用于语音图像处理器、声呐雷 达处理系统、传感网络、有限无限通讯系统、生物医疗系统、测试测量仪器等电子系统之中。 随着科技的发展,电子产品的小型化、移动化、穿戴化成为了主流,低功耗成为了电子产品 的重要指标,此外,无线通信系统的不断发展、物联网的飞速发展带来的信息爆炸式增长, 对系统的处理速度以及通信能力带来了巨大的挑战。综上,高速高精度低功耗ADC通常是整 个系统性能的瓶颈。 近些年来多路时间交织ADC作为高速高精度低功耗的研究重点,通过多路低速ADC 在时间域的交织合成一路高速ADC,突破了在相同工艺下,单路ADC速度的限制。而多路时间 交织ADC的精度、功耗也是衡量整个ADC的重要指标。在精度方面主要受限于单路ADC的性 能、还有时间交织产生的失调误差、增益误差、时间偏差等;在功耗方面主要受限于单路 ADC,参考电压的驱动电路,高速高精度多相位时钟产生电路等。目前单路ADC可以实现在低 功耗下保证良好的性能,时间交织产生的失调误差、增益误差、时间偏差可以通过前台或者 后台校准技术来解决,参考电压的驱动电路的功耗可以通过校准DAC的不完全建立误差来 降低,而高速高精度低功耗的多相位时钟产生电路目前没有较好的解决方案。目前已知的 解决思路如下: 一是如图1所示,通过外部输入高频时钟通过CML电路分频产生多相位时钟,然后 通过CML转CMOS电路将时钟电平转换成CMOS电平,再经过后续的时间偏差调整电路校准后, 最终得到多相位采样时钟。这种方案的显著缺点是通过外部输入的高速时钟性能比较差, 并且在采样时钟频率较高时,CML电路需要很大的电流才能实现高速分频,使得时钟电路功 耗成指数上升。 二是如图2所示,通过PLL产生一路基础时钟,然后通过多个延迟电路,延迟出多相 位时钟,再经过CML转CMOS电路将时钟电平转换成CMOS电平,最后经过后续的时间偏差调整 电路校准后得到多相位采样时钟。这种方案的显著缺点是高速时钟通过每一个延迟电路都 会恶化时钟的抖动(jitter) ,从而限制ADC的精度。

技术实现要素:

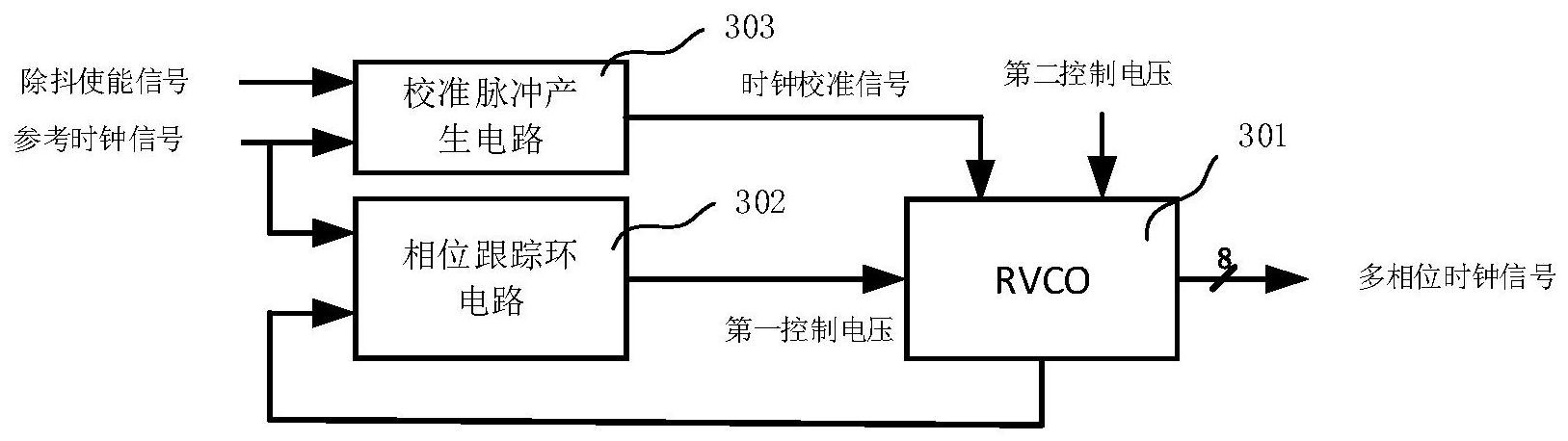

鉴于上述的分析,本发明旨在提供一种用于时间交织采样ADC的多相位时钟产生 电路,在保证高速的前提下,实现低时钟抖动,低时间偏差和低功耗。 本发明公开了一种用于时间交织采样ADC的多相位时钟产生电路,包括环形压控 振荡器、相位跟踪环电路和校准脉冲产生电路; 4 CN 111600606 A 说 明 书 2/6 页 环形压控振荡器与相位跟踪环电路构成PLL环路;所述环形压控振荡器在所述相 位跟踪环电路输出的第一控制电压的控制下输出多个相位的时钟信号;将其中一个相位的 时钟信号反馈到所述相位跟踪环电路中与输入的参考时钟信号进行鉴相,对第一控制电压 的幅度进行调整,使环形压控振荡器输出的多个相位的时钟信号频率与参考时钟频率相 等; 校准脉冲产生电路与环形压控振荡器连接,用于输出时钟校准信号到环形压控振 荡器中,调整环形压控振荡器内部时钟,消除时钟抖动对输出时钟信号的影响。 进一步地,所述环形压控振荡器还根据输入的第二控制电压,调整多个相位的时 钟信号之间的相位差。 进一步地,所述环形压控振荡器包括连接成环形的结构相同的第一、第二、第三和 第四延迟单元,其中,第四延迟单元的输出端OP、ON分别与第一延迟单元的输入端IP、IN连 接;其余顺序连接的延迟单元中前一个延迟单元的输出端OP、ON分别与下一个延迟单元的 输入端IN、IP连接; 每个所述延迟单元的输入端IP、IN的信号的相位差为180°,输出端ON、OP的信号的 相位差为180°;输出端OP的信号与输入端IN的信号的相位差为45°,输出端ON的信号与输入 端IP的信号的相位差为45°。 进一步地,所述延迟单元包括第一反相器、第二反相器、第三反相器、第四反相器, 第一常通传输门、第二常通传输门、第一可变电容器组和第二可变电容器组; 第一反相器的输出端连接第二反相器的输入端;第三反相器的输出端连接第四反 相器的输入端;第一反相器的输入端与第三反相器的输出端之间跨接第一常通传输门;第 三反相器的输入端与第一反相器的输出端之间跨接第二常通传输门;第一反相器的输出端 与第三反相器的输出端之间跨接并联的第一可变电容器组和第二可变电容器组; 第一反相器的输入端为延迟单元的输入端IN,第三反相器的输入端为延迟单元的 输入端IP;第二反相器的输出端为延迟单元的输出端OP,第四反相器的输出端为延迟单元 的输出端ON; 第一可变电容器组为压控电容组,其控制端VC接入控制电压,通过控制第一可变 电容器组的电容量来控制延迟单元输出时钟信号的频率; 第二可变电容器组为压控电容组,其控制端VT接入控制电压,通过控制第二可变 电容器组的电容量来控制延迟单元输出时钟信号的相位。 进一步地,每个所述延迟单元的控制端VC均与所述相位跟踪环电路输出的第一控 制电压连接,使每个延迟单元的输出时钟信号频率都与参考时钟信号频率相同; 第一、第二、第三和第四延迟单元的控制端VT分别连接第二控制电压VTS1、VTS2、 VTS3和VTS4,分别对各延迟单元输出的时钟信号的相位进行调节。 进一步地,所述环形压控振荡器还包括一个NMOS管,所述NMOS管的源极和漏极跨 接在任意一个延迟单元的输入端IN、IP之间,栅极连接校准脉冲产生电路的输出端。 进一步地,所述环形压控振荡器还包括四个NMOS管,分别与四个延迟单元对应,每 一个NMOS管的源极和漏极跨接在与其对应的延迟单元的输入端IN、IP之间;在四个NMOS管 中的任取一个NMOS管的栅极连接校准脉冲产生电路的输出端,其余三个NMOS管的栅极都接 地。 5 CN 111600606 A 说 明 书 3/6 页 进一步地,所述校准脉冲产生电路接入参考时钟信号,在除抖使能信号的使能下, 输出一个与参考时钟信号上升沿对齐的时钟校准信号,到所述NMOS管栅极; 当环形压控振荡器发生时钟抖动时,NMOS管跨接的延迟单元输出端OP、ON的输出 电位不相等,时钟校准脉冲信号使NMOS管导通,则有电流流过NMOS管,使输出端OP、ON之间 的电压差减少到零,环形压控振荡器输出时钟信号过零点被重新定时在了注入的时钟校准 脉冲信号的到来时刻。 进一步地,所述校准脉冲产生电路包括三输入端与门和延迟反相模块; 所述延迟反相模块的输入端接入参考时钟信号,输出端输出延迟设定时间并且反 相的参考时钟信号; 所述三输入端与门的第一输入端接入除抖使能信号;第二输入端接入参考时钟信 号,第三输入端接入延迟设定时间并且反相的参考时钟信号; 当除抖使能信号为高电平时,所述校准脉冲产生电路输出上升沿与参考时钟信号 上升沿对齐的,脉冲宽度为设定延迟时间的时钟校准信号。 进一步地,延迟反相模块包括顺序连接的三个反相器;输入信号为参考时钟信号, 输出为延迟时间为三个反相器延迟时间之和的,与参考时钟信号反相的时钟信号。 本发明的有益效果如下: 本发明采用的外部输入时钟信号频率与多相位采样时钟频率相同,不需要使用 CML分频电路,从而大幅度电路功耗。同时可以在PLL(锁相环)中直接产生低抖动、低时钟偏 差的多相位时钟,不需要额外的延迟电路,降低了硬件开销,并且实现低时钟抖动,保证ADC 的精度。 附图说明 附图仅用于示出具体实施例的目的,而并不认为是对本发明的限制,在整个附图 中,相同的参考符号表示相同的部件。 图1为基于PLL的时钟产生电路组成连接示意图; 图2为传统时钟产生电路组成连接示意图; 图3为发明实施例中的多相位时钟产生电路组成连接示意图; 图4为发明实施例中的环形压控振荡器组成连接示意图; 图5为发明实施例中的延迟单元组成连接示意图; 图6为发明实施例中的校准脉冲产生电路组成连接示意图。