技术摘要:

本发明公开了一种降低P型MOSFET源漏电极接触电阻的制备方法,属于微电子技术领域,包括从下至上依次层叠设置的硅衬底、AlN成核层、AlGaN缓冲层、低温GaN位错阻隔层、GaN沟道层、AlGaN势垒层及GaN盖帽层,本发明利用低温GaN位错阻隔层能够有效降低氮化镓外延层中的位错 全部

背景技术:

金属与半导体接触时会形成两种接触方式:肖特基接触和欧姆接触。欧姆接触是 指在接触处是一个纯电阻,而且该电阻越小越好,使得组件操作时,大部分的电压降在活动 区(Active region)而不在接触面。因此,其I-V特性是线性关系,斜率越大接触电阻越小, 接触电阻的大小直接影响器件的性能指标。一般欧姆接触主要措施是半导体表面进行高掺 杂。在P型MOSFET源漏区中,虽然使用mg H离子注入技术将mg掺杂到GaN中,但其激活能太 高,室温下其掺杂浓度即使达到1E 20cm-3,大约也只有1%的mg电离;另外,mg H离子注入会 产生空位缺陷,这些空位缺陷会成为补偿中心;且mg-H键结合形成络合物(H钝化作用),都 会导致源漏区的空穴浓度降低。

技术实现要素:

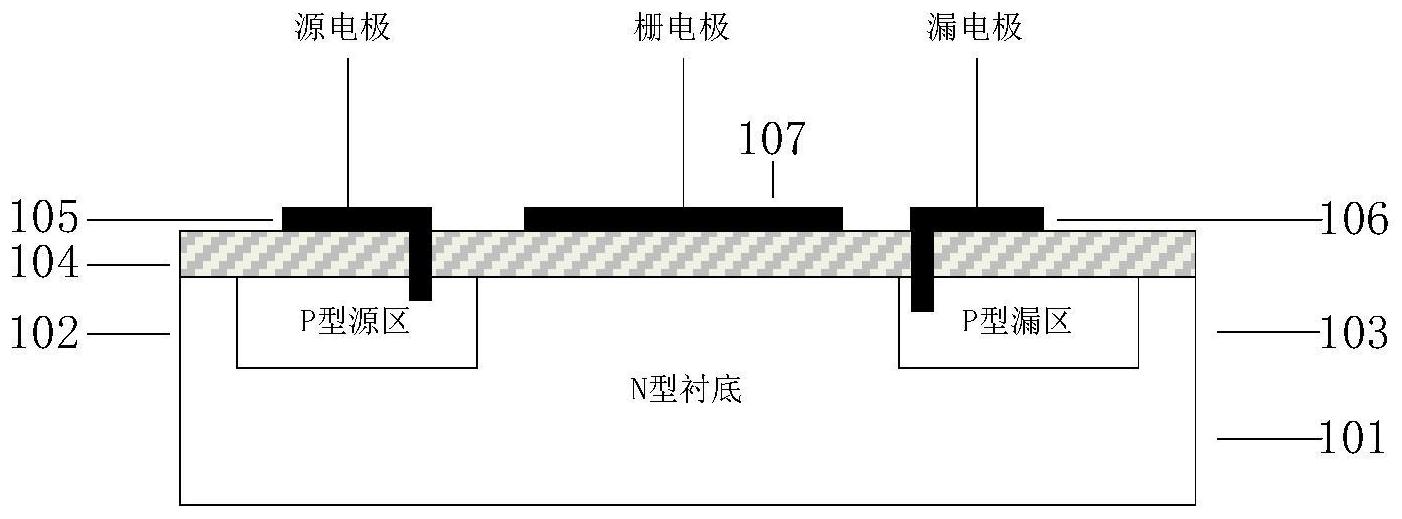

本发明的目的在于克服现有技术不足之处,其原理是,在制作完成源区及漏区后 使用激光进行退火,降低空位缺陷,打断mg-H键,增加空穴浓度,降低与金属电极的接触势 垒宽度,形成隧穿效应,达到欧姆接触。 一种降低P型MOSFET源漏电极的接触电阻,包括从下至上依次层叠设置的N型衬 底、P型源区、P型漏区、介质层、源电极、漏电极以及栅电极。 一种降低P型MOSFET源漏电极接触电阻的制备方法,包括如下步骤: (1)在一块N型衬底上通过刻蚀光罩确定P型源区、P型漏区和栅极区域; (2)在前述步骤基础上使用离子注入技术,将mg H离子注入到P型源区和P型漏区 中,形成高掺杂的P型GaN,掺杂浓度约为8E 19cm-3; (3)在前述步骤基础上使用激光对P型源区和P型漏区进行激光退火,激光波长为 525-540nm的绿光,脉冲宽度为20-200ns,功率为50W-200W; (4)在前述步骤基础上沉积介质层,材料为SiO2,厚度为100nm; (5)在前述步骤基础上采用电子束蒸镀技术进行金属沉积,依次沉积Ti/Al/Ni/Au 四种金属,四层金属层的厚度分别为20nm、1500nm、30nm和100nm,蒸镀结束后,采用金属剥 离设备将光刻胶上面的多层金属去除,形成源电极和漏电极; (6)在前述步骤基础上对上述材料进行退火处理,退火温度为890-910℃,退火时 间为25-35s。 (7)在前述步骤基础上采用电子束蒸镀技术进行金属沉积,依次沉积Ni/Au,厚度 分别10-20nm和4000-5000nm,蒸镀结束后采用金属剥离设备将光刻胶上面的多层金属去 除,形成栅电极。 3 CN 111584620 A 说 明 书 2/3 页 优选的,所述步骤(3)中激光波长为532nm,脉冲宽度为100ns,功率为200W; 优选的,所述步骤(4)中介质层的材料为SiO2,厚度为100nm。 优选的,所述AlGaN缓冲层的生长温度为1100℃,厚度为1um。 优选的,所述步骤(6)中退火温度为900℃,退火时间为30s。 优选的,所述步骤(7)中Ni/Au的厚度分别15nm和4500nm。 优选的,所述N型衬底为N型氮化镓衬底材料,尺寸为2-8inch。 与现有技术相比,本发明具有如下优点:P型GaN(P型源区和漏区)经过激光退火, 降低内部的空位缺陷,且打断mg-H键,增加空穴浓度,降低与金属电极(采用钛/铝/镍/金多 层合金,经高温退火后形成)接触势垒厚度,形成隧穿效应,从而达到欧姆接触。 附图说明 图1为本发明的结构示意图。 其中:101-N型衬底,102-P型源区,103-P型漏区,104-介质层,105-源电极,106-漏 电极,107-栅电极。 图2为按照实施例1所得实验结果。