技术摘要:

本发明提供了一种三维存储器及其制作方法。该制作方法包括以下步骤:S1,提供表面具有栅极堆叠结构的第一衬底,栅极堆叠结构包括沿远离第一衬底的方向交替的栅极结构和隔离层,栅极堆叠结构中具有贯穿至第一衬底的沟道通孔和共源极沟槽,沟道通孔中设置有存储结构;S2 全部

背景技术:

随着对集成度和存储容量的需求不断提高,3D NAND存储器应运而生。3D NAND存 储器大大节省了硅片面积,降低制造成本,增加了存储容量。 在3D NAND存储器结构中,采用垂直堆叠多层数据存储单元的方式,实现堆叠式的 3D NAND存储器结构,然而,其他的电路例如解码器(decoder)、页缓冲(page buffer)和锁 存器(latch)等,这些外围电路都是CMOS器件形成的,CMOS器件的工艺无法与3D NAND器件 集成在一起。目前工艺中,分别采用不同的工艺形成3D NAND存储器阵列和外围电路,然后 通过键合技术将两者键合在一起。 然而,目前形成的3D NAND存储器阵列中由于存储单元堆叠的层数较多,导致具有 该存储器阵列的晶圆的整体应力也随着增大,从而导致翘曲度也相应增大,晶圆所具有的 较大翘曲度导致其在与外围电路键合时难度增大。 为了解决上述技术问题,现有技术中通常在形成3D NAND存储器阵列后晶圆的另 一面沉积应力膜,以调整晶圆弓值,这会导致工艺更为复杂,且不利于器件的轻薄化。

技术实现要素:

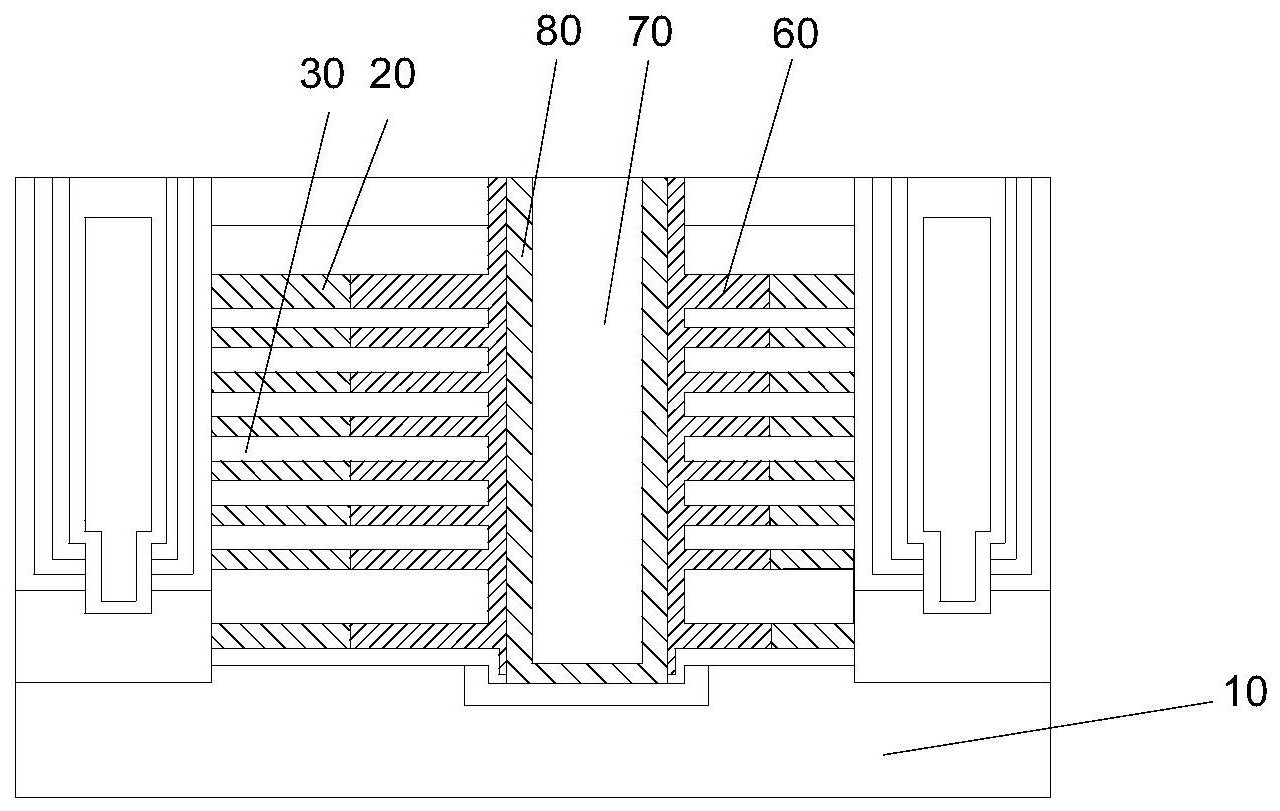

本发明的主要目的在于提供一种三维存储器及其制作方法,以解决现有技术中三 维存储器的具有存储器阵列的衬底应力较大而导致的与外围电路键合难度大的问题。 为了实现上述目的,根据本发明的一个方面,提供了一种三维存储器的制作方法, 包括以下步骤:S1,提供表面具有栅极堆叠结构的第一衬底,栅极堆叠结构包括栅极结构和 隔离层,栅极结构和隔离层沿远离第一衬底的方向交替层叠设置,栅极堆叠结构中具有贯 穿至第一衬底的沟道通孔和共源极沟槽,沟道通孔中设置有存储结构;S2,在共源极沟槽中 填充无定型硅并进行尖峰退火处理,以将部分无定型硅形成多晶硅壳层,多晶硅壳层包裹 剩余的无定型硅;S3,步骤S2处理后的结构进行热处理,剩余的无定型硅以形成多晶硅芯 层,多晶硅壳层与多晶硅芯层构成导电通道。 进一步地,尖峰退火处理的最高温度为950~1010℃。 进一步地,尖峰退火处理具有第一升温阶段和第一降温阶段,热处理具有第二升 温阶段、恒温阶段和第二降温阶段。 进一步地,第一升温阶段的升温速度大于第二升温阶段的升温速度。 进一步地,第一升温阶段的升温时间小于第二升温阶段的升温时间。 进一步地,第一降温阶段的降温速度大于第二降温阶段的降温速度。 进一步地,在共源极沟槽中填充无定型硅的步骤包括:回刻栅极结构,以形成与共 源极沟槽连通的回刻通道;在回刻通道和共源极沟槽中填充绝缘材料,刻蚀共源极沟槽中 的绝缘材料,以形成刻蚀通道;在刻蚀通道中填充无定型硅。 4 CN 111599818 A 说 明 书 2/6 页 进一步地,在步骤S3之后,得到具有存储器阵列的第一衬底,制作方法还包括以下 步骤:S4,提供具有CMOS电路的第二衬底,将栅极堆叠结构与CMOS电路键合。 进一步地,在将第一衬底与第二衬底键合的步骤之前,步骤S4还包括:在第一衬底 远离存储器阵列的一侧形成张力膜。 进一步地,张力膜的厚度为1000~5000A。 进一步地,形成张力膜的材料为SO2和/或SiN。 根据本发明的另一方面,提供了一种三维存储器,包括具有存储器阵列的第一衬 底,存储器阵列包括栅极堆叠结构,栅极堆叠结构包括栅极结构和隔离层,栅极结构和隔离 层沿远离第一衬底的方向交替层叠设置,栅极堆叠结构中形成有贯穿至第一衬底的多个沟 道通孔和共源极沟槽,存储器阵列还包括:存储结构,位于各沟道通孔中;多晶硅芯层,位于 共源极沟槽中;多晶硅壳层,位于共源极沟槽中并包裹多晶硅芯层,且多晶硅壳层的硬度大 于多晶硅芯层的硬度。 进一步地,三维存储器还包括:回刻通道,回刻通道位于隔离层之间且与栅极结构 连接;回刻通道填充有无定形硅。 进一步地,三维存储器还包括:第二衬底,第二衬底具有CMOS电路;键合部,连接存 储结构和CMOS电路。 进一步地,三维存储器还包括张力膜,张力膜位于第一衬底远离存储器阵列的一 侧。 进一步地,张力膜的厚度为1000~5000A。 进一步地,形成张力膜的材料为SO2和/或SiN。 应用本发明的技术方案,提供了一种三维存储器的制作方法,该制作方法中在第 一衬底上的栅极堆叠结构中形成存储结构后,在栅极堆叠结构中形成贯穿至第一衬底的共 源极沟槽,并将牺牲层置换为栅极结构,然后在共源极沟槽中填充无定型硅并进行尖峰退 火处理,以将部分无定型硅形成多晶硅壳层,多晶硅壳层包裹剩余的无定型硅,由于尖峰退 火在快速升温后直接进行降温冷却,从而使得无定型硅的表层部分成为多晶硅,且由于仅 表层部分的无定形硅形成多晶硅,因此在形成多晶硅壳层的过程中具有较小的收缩率,进 而能够具有较大的硬度,再对剩余的无定型硅进行热处理,以形成多晶硅芯层,在上述热处 理的过程中上述多晶硅壳层能够作为支撑层,缓解无定型硅受热收缩对衬底的影响,进而 缓解了现有技术中退火工艺导致的衬底应力增大,使得衬底不会具有翘曲度,有利于后续 与CMOS电路的键合。 附图说明 构成本发明的一部分的说明书附图用来提供对本发明的进一步理解,本发明的示 意性实施例及其说明用于解释本发明,并不构成对本发明的不当限定。在附图中: 图1示出了在本申请实施方式所提供的三维存储器的制作方法中,提供表面具有 栅极堆叠结构的第一衬底并在栅极堆叠结构的共源极沟槽中后的基体剖面结构示意图; 图2示出了一种在图1所示的共源极沟槽中填充无定型硅后的基体剖面结构示意 图; 图3示出了另一种在图1所示的共源极沟槽中填充无定型硅后的基体剖面结构示 5 CN 111599818 A 说 明 书 3/6 页 意图; 图4示出了对图3所示的无定型硅进行尖峰退火处理以形成多晶硅壳层后的基体 剖面结构示意图; 图5示出了对图4所示的结构进行热处理以将剩余的无定型硅形成多晶硅芯层后 的基体剖面结构示意图; 图6示出了在本申请实施方式所提供的一种三维存储器的局部剖面结构示意图。 其中,上述附图包括以下附图标记: 10、第一衬底;20、栅极结构;30、隔离层;40、存储结构;410、电荷阻挡层;420、电荷 俘获层;430、隧穿层;440、沟道层;50、共源极沟槽;60、绝缘材料;70、无定型硅;80、多晶硅 壳层;90、多晶硅芯层。