技术摘要:

本申请实施例公开了一种失败比特数统计方法及存储器设备,其中,所述方法包括:将第i次编程脉冲施加到存储器单元;在施加所述第i编程脉冲的过程中,执行以下操作:从第一锁存器读取第i‑1次统计数据,所述第i‑1统计数据为用于统计第i‑1编程操作的失败比特数所需的数 全部

背景技术:

快闪存储器作为例如移动电话、数字相机等便携式电子设备的存储媒介而被广泛 使用。快闪存储器通常使用允许高存储器密度、高可靠性和低功耗的单晶体管存储器单元。 通过对电荷存储结构(例如,浮栅或电荷阱)或其它物理现象(例如,相变或偏振)进行编程, 存储器单元的阈值电压的改变决定每个存储器单元的数据状态(例如,数据值)。 相关技术中,对存储器进行编程后,需要进行失败比特数统计(Fail Bit Count, FBC),而在时序上,统计失败比特数的操作是在当前编程操作和下一次编程操作之间执行 的,需要占用额外的时间。

技术实现要素:

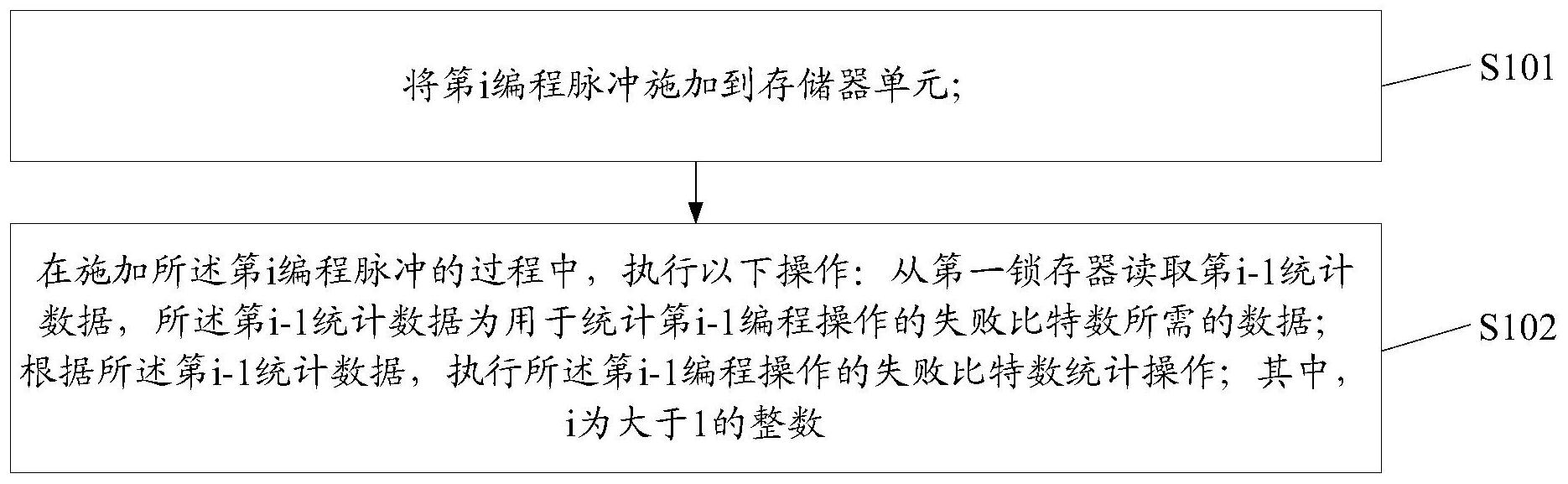

有鉴于此,本申请实施例为解决相关技术中存在的问题而提供一种失败比特数统 计方法及存储器设备。 本申请实施例的技术方案是这样实现的: 第一方面,本申请实施例提供一种失败比特数统计方法,包括: 将第i编程脉冲施加到存储器单元; 在施加所述第i编程脉冲的过程中,执行以下操作: 从第一锁存器读取第i-1统计数据,所述第i-1统计数据为用于统计第i-1编程操 作的失败比特数所需的数据; 根据所述第i-1统计数据,执行所述第i-1编程操作的失败比特数统计操作; 其中,i为大于1的整数。 在一些实施例中,在所述施加所述第i编程脉冲的过程中,所述方法还执行以下操 作: 从第二锁存器读取第i编程数据,所述第i编程数据为对所述存储器单元执行第i 编程操作所需的数据; 根据所述第i编程数据,执行所述第i编程操作。 在一些实施例中,所述方法应用于存储器中存储器单元的页面编程过程;所述第 一锁存器为所述存储器的页面缓冲器中的低电压阈值锁存器;所述第二锁存器为所述页面 缓冲器中的感测锁存器。 在一些实施例中,所述将第i编程脉冲施加到存储器单元之前,所述方法还包括: 执行第i-1编程操作的验证操作,获得所述第i-1验证结果;其中,所述第i-1验证 结果包括第i-1统计数据和第i编程数据,其中第i-1统计数据为用于统计第i-1编程操作的 失败比特数所需的数据,所述第i编程数据为用于对存储器单元执行第i编程操作所需的数 5 CN 111599400 A 说 明 书 2/11 页 据; 将所述第i编程数据存储至所述第二锁存器中。 在一些实施例中,所述方法还包括:在所述将第i编程脉冲施加到存储器单元之 前,将所述第i-1统计数据存储至所述第一锁存器中;或者, 在施加所述第i编程脉冲的过程中,在所述从第一锁存器读取第i-1统计数据之 前,将所述第i-1统计数据存储至所述第一锁存器中。 在一些实施例中,所述方法还包括:当所述将第i编程脉冲施加到存储器单元执行 完成之后,执行第i编程操作的验证操作,获得所述第i验证结果;其中,所述第i验证结果包 括第i统计数据和第i 1编程数据; 将所述第i统计数据存储至所述第一锁存器中; 将所述第i 1编程数据存储至所述第二锁存器中。 在一些实施例中,所述方法还包括: 当所述将第i编程脉冲施加到存储器单元执行完成之后,执行第i编程操作的验证 操作,获得所述第i验证结果;其中,所述第i验证结果包括第i统计数据和第i 1编程数据; 将所述第i 1编程数据存储至所述第二锁存器中; 对应地,在施加所述第i 1编程脉冲的过程中,在从所述第一锁存器读取第i统计 数据之前,还包括:将所述第i统计数据存储至所述第一锁存器中。 在一些实施例中,所述第i验证结果还包括第i编程结果,所述第i编程结果用于表 征对所述存储器单元执行的第i编程操作是否通过; 对应地,所述方法还包括: 当所述第i编程结果为不通过时,将第i编程脉冲增加特定的步进电压得到第i 1 编程脉冲; 将所述第i 1编程脉冲施加到所述存储器单元。 第二方面,本申请实施例提供一种存储器设备,包括: 存储器单元阵列,所述存储器单元阵列包括多个存储器单元; 外围电路,包括编程操作电路和第一锁存器;其中,所述编程操作电路,用于对所 述存储器单元阵列执行编程脉冲施加操作、验证操作和失败比特数统计操作;所述第一锁 存器,用于存储第i-1统计数据,所述第i-1统计数据为用于统计第i-1编程操作的失败比特 数所需的数据,i为大于1的整数; 控制逻辑电路,用于在所述编程脉冲施加操作期间控制所述外围电路在对所述存 储器单元阵列施加所述第i编程脉冲的过程中,执行以下操作:从所述第一锁存器读取所述 第i-1统计数据;根据所述第i-1统计数据,执行所述第i-1编程操作的失败比特数统计操 作。 在一些实施例中,所述外围存储器还包括第二锁存器;所述第二锁存器用于存储 第i编程数据,所述第i编程数据为对所述存储器单元执行第i编程操作所需的数据; 所述控制逻辑电路,还用于在所述编程脉冲施加操作期间控制所述外围电路在对 所述存储器单元阵列施加所述第i编程脉冲的过程中,还执行以下操作: 从所述第二锁存器读取所述第i编程数据; 根据所述第i编程数据,执行所述第i编程操作。 6 CN 111599400 A 说 明 书 3/11 页 在一些实施例中,所述外围电路包括: 页面缓冲器,用于在所述编程脉冲施加操作期间根据编程数据控制所述存储器单 元阵列的位线的电位水平,并且在所述验证操作期间通过感测所述位线的电位水平来暂时 存储所述多个存储器单元中的选中的存储器单元的感测数据; 对应地,所述第一锁存器为所述页面缓冲器中的低电压阈值锁存器;所述第二锁 存器为所述页面缓冲器中的感测锁存器。 在一些实施例中,所述控制逻辑电路,还用于:在将第i编程脉冲施加到存储器单 元之前,执行第i-1编程操作的验证操作,获得所述第i-1验证结果;其中,所述第i-1验证结 果包括所述第i-1统计数据和所述第i编程数据。 在一些实施例中,所述外围电路还包括:统计数据读取电路,用于所述控制逻辑电 路从所述第一锁存器中读取所述第i-1统计数据。 在一些实施例中,所述控制逻辑电路,还用于:当将第i编程脉冲施加到存储器单 元执行完成之后,执行第i编程操作的验证操作,获得所述第i验证结果;其中,所述第i验证 结果包括第i编程结果,所述第i编程结果用于表征对所述存储器单元执行的第i编程操作 是否通过;当所述第i编程结果为不通过时,将第i编程脉冲增加特定的步进电压得到第i 1 编程脉冲;将第i 1编程脉冲施加到所述存储器单元。 本申请实施例中,将第i编程脉冲施加到存储器单元;在施加所述第i编程脉冲的 过程中,执行以下操作:从第一锁存器读取第i-1统计数据,所述第i-1统计数据为用于统计 第i-1编程操作的失败比特数所需的数据;根据所述第i-1统计数据,执行所述第i-1编程操 作的失败比特数统计操作;其中,i为大于1的整数;如此,可以在施加下一个编程脉冲的过 程中,从第一锁存器中读取统计失败比特数量所需的数据,并进行失败比特数统计操作,这 样,在整个编程操作的迭代过程中失败比特数统计操作不占用额外的时间,从而可以节省 整个编程操作的迭代过程的执行时间,提高对存储器单元编程的效率。 附图说明 图1A为相关技术中存储器的外围电路的硬件结构示意图; 图1B为相关技术中编程过程的电压时序图; 图1C为该存储器设备的组成结构示意图; 图1D为本申请实施例提供的一种失败比特数统计方法的实现流程示意图; 图1E为本申请实施例失败比特数统计方法中编程过程的电压时序图; 图2A为本申请实施例提供的存储器设备的组成结构示意图; 图2B为本申请实施例提供的一种存储器设备的外围电路的硬件结构示意图; 图2C为本申请实施例提供的一种失败比特数统计方法的实现流程示意图; 图3为本申请实施例提供的一种失败比特数统计方法的实现流程示意图; 图4为本申请实施例提供的一种失败比特数统计方法的实现流程示意图; 图5为本申请实施例提供的一种失败比特数统计方法的实现流程示意图。