技术摘要:

提供了一种半导体器件及其制造方法。半导体器件可以包括顺序堆叠的第一子芯片和第二子芯片以及将第一子芯片和第二子芯片彼此电连接的贯通接触部。第一子芯片和第二子芯片中的每一个子芯片包括衬底和介于衬底之间的多个互连线。第二子芯片的互连线可以包括分别具有第一 全部

背景技术:

由于半导体器件的小尺寸、多功能和/或低成本的特性,它们被认为是电子行业中 的重要元件。半导体器件被分为用于存储数据的存储器件、用于处理数据的逻辑器件以及 包括存储器和逻辑元件二者的混合器件。为了满足对高速和/或低功耗电子器件的增长需 求,可能需要实现高可靠性、高性能和/或多功能的半导体器件。为了满足这些技术参数,半 导体器件的复杂性和/或集成密度正在增加。 图像传感器是将光学图像转换成电信号的器件。随着计算机和通信行业的不断发 展,在各种应用比如数码相机、便携式摄像机、个人通信系统、游戏机、安全摄像机、医疗用 微型相机和/或机器人中,对高性能图像传感器的需求不断增长。 图像传感器通常被分为电荷耦合器件(CCD)图像传感器和互补金属氧化物半导体 (CMOS)图像传感器。对于CMOS图像传感器,因为可以通过简单的操作方法来操作CMOS图像 传感器,并且可以将CMOS图像传感器的信号处理电路集成在单个芯片上,所以可以减小产 品尺寸。另外,CMOS图像传感器具有相对低的功耗,并因此可以用在电池容量有限的产品 中。

技术实现要素:

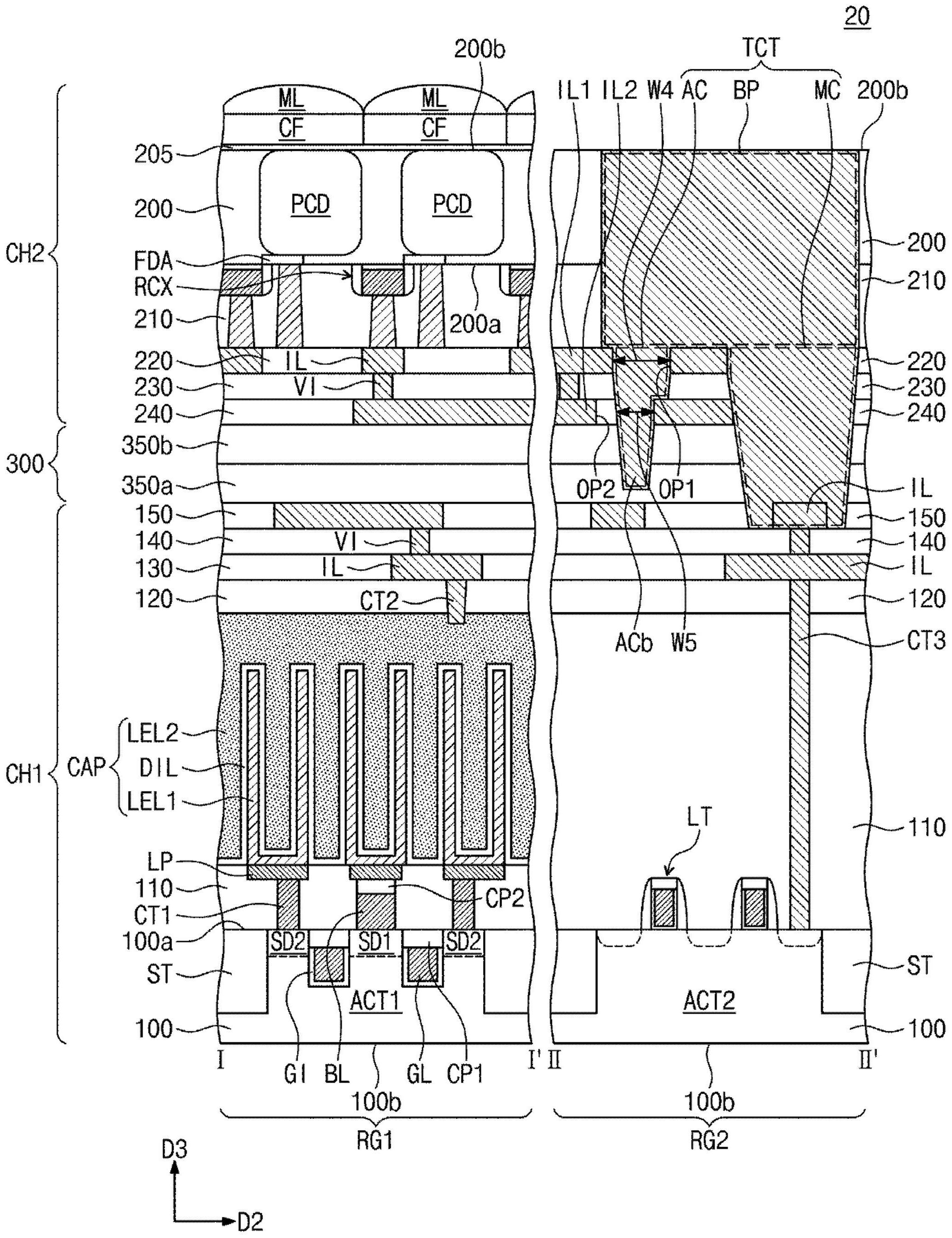

本发明构思的一些实施例提供了一种其中设置了具有高结构稳定性的贯通接触 部的半导体器件。 本发明构思的一些实施例提供了一种其中设置了具有高结构稳定性的贯通接触 部的半导体器件的制造方法。 根据本发明构思的一些实施例中,一种半导体器件可以包括:第一子芯片,包括第 一衬底和第一衬底上的第一多个互连线;第二子芯片,包括第二衬底和第二衬底上的第二 多个互连线。第二子芯片堆叠在第一子芯片上,第一子芯片的第一多个互连线和第二子芯 片的第二多个互连线位于第一衬底与第二衬底之间,并且贯通接触部从第二衬底朝第一子 芯片延伸以将第一子芯片和第二子芯片彼此电连接。第二子芯片的第二多个互连线可以包 括具有第一开口的第一互连线和具有第二开口的第二互连线。第二开口的中心可以相对于 第一开口的中心在平行于第一衬底和第二衬底的方向上水平偏移。贯通接触部可以包括在 第一开口和第二开口中朝第一子芯片延伸的辅助接触部。相对于第一衬底,辅助接触部的 6 CN 111584464 A 说 明 书 2/12 页 底表面的高度可以高于第一子芯片的第一多个互连线中的最上互连线的顶表面的高度。 根据本发明构思的一些实施例中,一种半导体器件可以包括:第一子芯片,包括第 一衬底和第一衬底上的第一多个互连线;第二子芯片,包括第二衬底和第二衬底上的第二 多个互连线。第二子芯片堆叠在第一子芯片上。半导体器件包括穿透第二子芯片并将第一 子芯片和第二子芯片彼此电连接的贯通接触部。第二子芯片的第二多个互连线可以包括具 有第一开口的第一互连线和具有第二开口的第二互连线。第二开口的中心可以相对于第一 开口的中心水平偏移。贯通接触部可以包括在第一开口和第二开口中朝第一子芯片延伸的 辅助接触部以及电连接到第一子芯片的第一多个互连线中的最上互连线的主接触部。相对 于第一衬底,辅助接触部的底表面的高度可以高于主接触部的底表面的高度。 根据本发明构思的一些实施例中,一种半导体器件可以包括第一衬底、第一衬底 上的下互连线和下互连线上的上互连线以及从上互连线竖直延伸到下互连线以将上互连 线和下互连线彼此电连接的贯通接触部。上互连线可以包括具有第一开口的第一互连线和 第一互连线上具有第二开口的第二互连线。第二开口的中心可以相对于第一开口的中心在 平行于第一衬底的方向上水平偏移。贯通接触部可以包括在第二开口和第一开口中朝第一 衬底延伸的辅助接触部以及电连接到下互连线的主接触部。相对于第一衬底,辅助接触部 的底表面的高度可以高于主接触部的底表面的高度。 根据本发明构思的一些实施例中,一种制造半导体器件的方法可以包括:形成包 括第一衬底和第一衬底上的第一多个互连线的第一子芯片;形成包括第二衬底和第二衬底 上的第二多个互连线的第二子芯片;将第一子芯片和第二子芯片彼此面对地堆叠;形成贯 通接触孔以穿透第二子芯片并暴露第一子芯片的第一多个互连线中的最上互连线;以及形 成贯通接触部以填充贯通接触孔。第二子芯片的形成可以包括:形成第一互连线,第一互连 线是第二多个互连线中的一个互连线并具有第一开口;以及在第一互连线上形成第二互连 线以具有第二开口,其中第二开口相对于第一开口水平偏移。贯通接触孔的形成可以包括 形成延伸穿过第一开口和第二开口的辅助接触孔。相对于第一衬底,辅助接触孔的底表面 的高度可以高于第一子芯片的最上互连线的顶表面的高度。 附图说明 根据以下结合附图的简要描述,将更清楚地理解示例实施例。附图表示本文所述 的非限制性示例实施例。 图1A、图2A、图3A和图4A是示出了根据本发明构思的一些实施例的形成半导体器 件的贯通接触部的方法的平面图。 图1B、图2B、图3B和图4B分别是沿图1A、图2A、图3A和图4A的线I-I’截取的截面图。 图5是示出了根据本发明构思的一些实施例的像素阵列中包括的单元像素的示例 的电路图。 图6是示出了其中安装了根据本发明构思的一些实施例的半导体器件的半导体封 装的截面图。 图7是示出了根据本发明构思的一些实施例的半导体器件的平面图。 图8是沿图7的线I-I’和II-II’截取的截面图。 图9至图13是沿图7的线I-I’和II-II’截取的截面图,用以示出根据本发明构思的 7 CN 111584464 A 说 明 书 3/12 页 一些实施例的制造半导体器件的方法。 图14是示出了根据本发明构思的一些实施例的半导体器件的一定区域的截面图。 应当注意,这些附图旨在说明在某些示例实施例中使用的方法、结构和/或材料的 一般特性,并补充下面提供的书面描述。但是,这些附图没有按比例绘制且可能没有精确反 映任何给定实施例的精确结构或性能特性,并且不应被解释为限定或限制示例实施例所包 含的值或特性的范围。例如,为了清楚起见,模块、层、区域和/或结构元件的相对厚度和定 位可以缩小或放大。在各附图中使用相似或相同的附图标记旨在表示存在相似或相同的元 件或特征。