技术摘要:

本发明属于电子类课程虚实技术领域,公开了一种电类课程虚实一体化实验平台电路优化方法及系统,在上位机通过仿真软件进行实验电路的连线与搭建,通过网线连接到硬件服务器;当在仿真软件中搭建电路完毕后,在软件中进行编译,在检查无误编译完毕后生成FPGA可识别的项 全部

背景技术:

传统的电子类课程实验分为硬件实现和软件仿真两类。硬件实现主要是各大厂商 根据实验课程要求,开发出各类实验箱、实验台供学生接线,操作,验证。它的优点是电路都 是由真实元件搭建的实际模型,与今后工作中需要搭建的电路完全一致,不会出现理论仿 真通过但是实际电路出错的情况。同时做实验的过程中会出现很多真实的故障,排除故障 的过程中能够提高学生解决问题的能力。缺点是实验箱损坏率较高,投资较大,维护起来非 常不方便。 软件仿真主要是近年来各种厂商推出的虚拟仿真软件以及各种专业的仿真软件。 它的优点是灵活方便,投资少,几乎没有维护费用,做实验方便快捷,可以轻易的实现远程 实验。缺点是仿真结果有时候不能完全替代硬件实验搭建,很多时候仿真结果正确但是到 实际电路的搭建可能会出很多问题。而且很多软件仿真软件过于简化实验流程,学生只需 要按照说明书用鼠标点击连线即可出来实验结果,如果不按照程序连线就无法出来结果, 比较死板,限制了学生的创新思维。很多时候电路的搭建并不只有一种方案,实验的目的应 该是给学生充分的自由空间让学生学会在实验现象中充分理解实验原理,通过不断的尝试 总结出实验规律以及对理论的验证。 目前市场上出现一种新的方案是虚实一体或者叫软硬结合的实验平台搭建方案, 既有软件仿真方便快捷的优点,同时又有真实的电路与之对应,同时具备了软件和硬件实 验的优点。他的方案是厂商针对各电子类的课程开发出一系列的软件仿真软件,如数字电 路、模拟电路、单片机、通信原理等核心课程都有类似的厂商在做。然后硬件端采用的不是 传统实验箱的形式,而是用专门的网管平台加一组实验硬件服务器的方式,实验硬件服务 器采用FPGA加相关外围电路搭建。用户在上位机用仿真软件搭建好实验电路,通过网管平 台下载到实验硬件服务器中,由上位机软件搭建的电路来决定FPGA内部电路的连线。由于 实验数据均由真实的硬件电路连线,测量值也是从硬件服务器中采集到的真实数据,因此 可以对真实的电路进行完美的仿真。同时硬件服务器采用集中存放,学生也可以通过远程 实验的方式访问到硬件服务器资源。然而,这种方式最大的缺点就是成本太高,FGPA搭建的 硬件服务器价格不菲,而且一个学生端就要一片FPGA搭建的硬件电路与之对应,几十个人 一个班的硬件成本非常高,一个班级的硬件服务器高达40到60万元,这严重影响了此类实 验平台的普及。 综上所述,现有技术存在的问题是:现有电子类课程虚实一体(软硬结合)实验平 台成本太高,FGPA搭建的硬件服务器价格不菲,而且一个学生端就要一片FPGA搭建的硬件 电路与之对应,几十个人一个班的硬件成本非常高,一个班级的硬件服务器高达40到60万 元,这严重影响了此类实验平台的普及;同时,现有课程虚实一体化实验平台电路优化方法 5 CN 111613112 A 说 明 书 2/7 页 对硬件校时误差大;电路测试效率低。

技术实现要素:

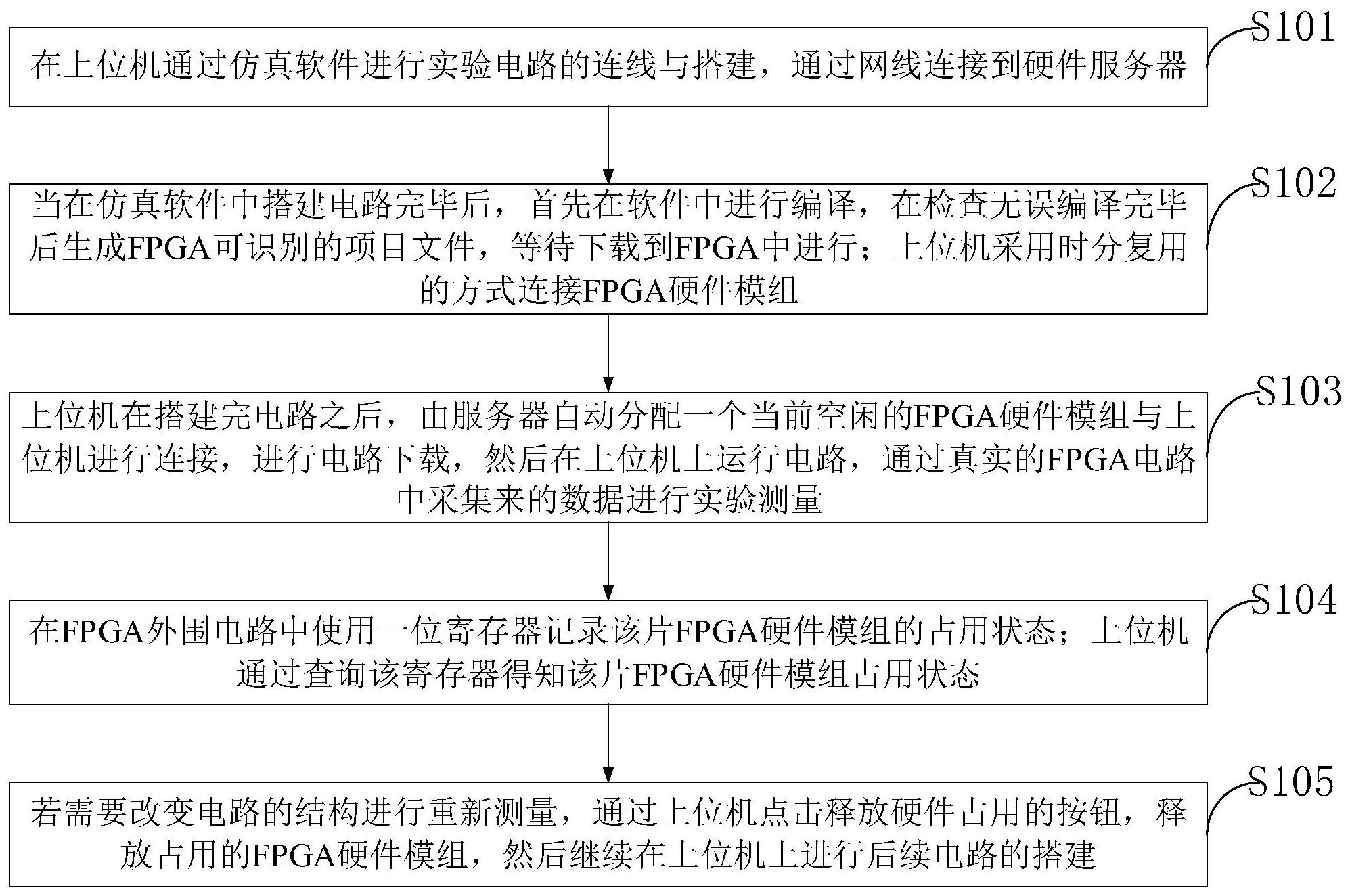

针对现有技术存在的问题,本发明提供了一种课程虚实一体化实验平台电路优化 方法及系统。 本发明是这样实现的,一种课程虚实一体化实验平台电路优化方法,包括以下步 骤: 步骤一,在上位机通过仿真软件进行实验电路的连线与搭建,通过网线连接到硬 件服务器; 步骤二,当在仿真软件中搭建电路完毕后,首先在软件中进行编译,在检查无误编 译完毕后生成FPGA可识别的项目文件,等待下载到FPGA中进行; 上位机采用时分复用的方式连接FPGA硬件模组; 步骤三,上位机在搭建完电路之后,由服务器自动分配一个当前空闲的FPGA硬件 模组与上位机进行连接,进行电路下载,然后在上位机上运行电路,通过真实的FPGA电路中 采集来的数据进行实验测量; 步骤四,在FPGA外围电路中使用一位寄存器记录该片FPGA硬件模组的占用状态; 上位机通过查询该寄存器得知该片FPGA硬件模组占用状态; 步骤五,若需要改变电路的结构进行重新测量,通过上位机点击释放硬件占用的 按钮,释放占用的FPGA硬件模组,然后继续在上位机上进行后续电路的搭建。 进一步,步骤三上位机与FPGA硬件模组通过硬件服务器进行连接,包括: (1)上位机(学生做仿真实验的PC机),通过RJ45网线通过交换机与服务器进行连 接; (2)FPGA硬件模组与服务器采用串口直连或者串口采集卡的方式连接,每块FPGA 实验板在服务器中都有一个对应的串口号。 步骤四在FPGA外围电路中使用一位寄存器记录该片FPGA硬件模组的占用状态,包 括但不限于使用查询串口占用状态、使用一位硬件寄存器、在软件中采用一个布尔型变量 实现。 进一步,步骤三实验测量中,通过校时模块进行校时,包括: (1)进行FPGA芯片布局并且得到芯片各单元布局后的坐标;根据FPGA芯片的布线 模式,获取和该模式对应的预存布线编码信息;根据各单元布局后的坐标确定该单元对应 的编码,然后根据所述布线编码信息进行各单元的布线剪枝; (2)通过布线后的FPGA芯片对从校时源获取的原始时间数据进行提取和解析,获 取校时时间信息; (3)根据所述校时时间信息和参考时间信息,利用预设的校时算法计算获取校时 信号,并利用数据总线将所述校时信号发送至校时装置;其中,所述参考时间信息为根据系 统时钟对应生成的时间信息。 进一步,所述通过布线后的FPGA芯片对从校时源获取的原始时间数据进行提取和 解析,获取校时时间信息,包括: (1.1)利用预设物理接口从所述校时源获取所述原始时间数据对应的电平信号; 6 CN 111613112 A 说 明 书 3/7 页 (1 .2)将所述电平信号转化为所述原始时间数据,并从所述原始时间数据中提取 校时原始时间数据;其中,所述校时原始时间数据为所述原始时间数据中进行校时所需的 原始时间数据;对所述校时原始时间数据进行解析,获取所述校时时间信息; 所述校时源具体为IRIG-B码源。 进一步,所述根据所述校时时间信息和参考时间信息,利用预设的校时算法计算 获取校时信号,并利用数据总线将所述校时信号发送至校时装置,包括: 根据所述校时时间信息和参考时间信息,利用所述校时算法和预设的守时算法计 算获取所述校时信号和守时信号; 利用所述数据总线将所述校时信号发送至所述校时装置,并将所述守时信号发送 至守时装置。 进一步,所述步骤三实验测量中,通过电路测试模块进行测试,包括: 1)通过测试程序提取待测电路模型;确定所述待测电路中,待测试的引脚、配置点 和路径中的至少一种信息;将待测电路配置为至少一个测试电路; 2)通过电路放大器放大测试电路信号; 3)根据确定的fault model故障模型,确定输入激励的序列; 4)确定各配置的测试电路的覆盖情况; 所述将所述待测电路配置为至少一个测试电路包括: 使用交叉配置设计,配置所述测试电路。 所述使用交叉配置设计,配置所述测试电路包括: 配置两个测试电路,分别为config_0和config_1,且config_0配置中LUT5A和 LUT5B的查找表初始值INITA和INITB,与config_1配置中的INITA和INITB相反。 进一步,所述根据确定的faultmodel故障模型,确定输入激励的序列中,所述故障 模型包括单固定故障模型。 所述单固定故障模型包括:将电平固定为1,或者固定为0。 本发明的另一目的在于提供一种课程虚实一体化实验平台电路优化系统,包括: 参数配置模块,与主控模块连接,用于通过配置程序对电子类课程虚实一体实验 平台上的硬件进行配置工作参数; 主控模块,与参数配置模块、电路搭建模块、网络通信模块、资源分配模块、状态记 录模块、下载模块、释放模块、存储模块、校时模块、电路测试模块、显示模块连接,用于通过 上位机控制各个模块正常工作; 电路搭建模块,与主控模块连接,用于通过电路仿真软件的对实验电路的进行连 线与搭建; 网络通信模块,与主控模块连接,用于通过网线将每台上位机(PC)连接到硬件服 务器; 资源分配模块,与主控模块连接,用于通过时分复用技术使上位机分别占用服务 器硬件; 状态记录模块,与主控模块连接,用于通过寄存器来记录该片FPGA硬件电路的占 用状态; 下载模块,与主控模块连接,用于通过下载程序下载实验电路; 7 CN 111613112 A 说 明 书 4/7 页 释放模块,与主控模块连接,用于通过PC端释放按钮释放硬件占用,该电路给其他 组学生使用; 存储模块,与主控模块连接,用于通过服务器存储搭建实验电路; 校时模块,与主控模块连接,用于通过校时程序对FPGA硬件电路进行校时; 电路测试模块,与主控模块连接,用于通过测试程序对FPGA硬件电路进行测试。 进一步,所述课程虚实一体化实验平台电路优化系统进一步包括: 显示模块,与主控模块连接,用于通过显示器显示实验电路、测试结果 本发明的优点及积极效果为:本发明由于电子类实验学生大部分时间都是在做线 路连接,接通电源观察实验现象只占少部分,因此提高硬件实验电路的复用性能够极大的 降低硬件成本。而FPGA的特点正好就是可以快速的改变电路的内部连接方式,可以在几秒 钟之内快速搭建好实验电路。一般一个班可以2-4组学生共用一套实验硬件资源,因此可以 帮助用户节约2-4倍的投入;以及本发明通过校时模块采用如IRIG-B码源的校准源作为时 钟源,避免了NTP软件校时方式中的网络延迟,以及标准NTP协议本身存在的时间误差;利用 FPGA并行处理的特点并采用校时算法进行时钟校准,避免了串行运算方式造成的时间误 差,使时间精度可达到微秒级,解决了时间误差过大的问题,提高了时钟校准的时间精度; 同时,通过电路测试模块提取待测电路模型;将待测电路配置为至少一个测试电路;根据确 定的故障模型,确定输入激励的序列;确定各配置的测试电路的覆盖情况。从而根据待测电 路模型确定了测试电路并基于故障模型输入激励,得到故障覆盖情况,成功的实现了对 FPGA电路的测试,提升了测试效率。 附图说明 图1是本发明实施例提供的课程虚实一体化实验平台电路优化方法流程图。 图2是本发明实施例提供的课程虚实一体化实验平台电路优化系统结构框图。 图中:1、参数配置模块;2、主控模块;3、电路搭建模块;4、网络通信模块;5、资源分 配模块;6、状态记录模块;7、下载模块;8、释放模块;9、存储模块;10、校时模块;11、电路测 试模块;12、显示模块。 图3是本发明实施例提供的校时模块校时方法流程图。 图4是本发明实施例提供的通过布线后的FPGA芯片对从校时源获取的原始时间数 据进行提取和解析,获取校时时间信息方法流程图。 图5是本发明实施例提供的电路测试模块测试方法流程图。