技术摘要:

本发明提供了一种同步计数器,该同步计数器包括:逻辑电路、至少两个数选电路、至少两个D触发器,至少两个数选电路与至少两个D触发器一一对应;逻辑电路的信号输入端与每个D触发器的输出端连接,逻辑电路的第一信号输出端与每个数选电路的第一输入端连接,逻辑电路的第 全部

背景技术:

计数器电路是集成电路设计的基本电路之一,按照时钟脉冲输入方式的不同,可 分为同步计数器和异步计数器。采用同步计数器设计的电路稳定性好,目前很多集成电路 设计中都使用了同步计数器电路进行设计。 然而,随着集成电路的普及与应用,对集成电路中同步计数器的性能也提出了更 高的要求,因此,如何提供实现更高性能的同步计数器成为本领域人员亟待解决的问题。

技术实现要素:

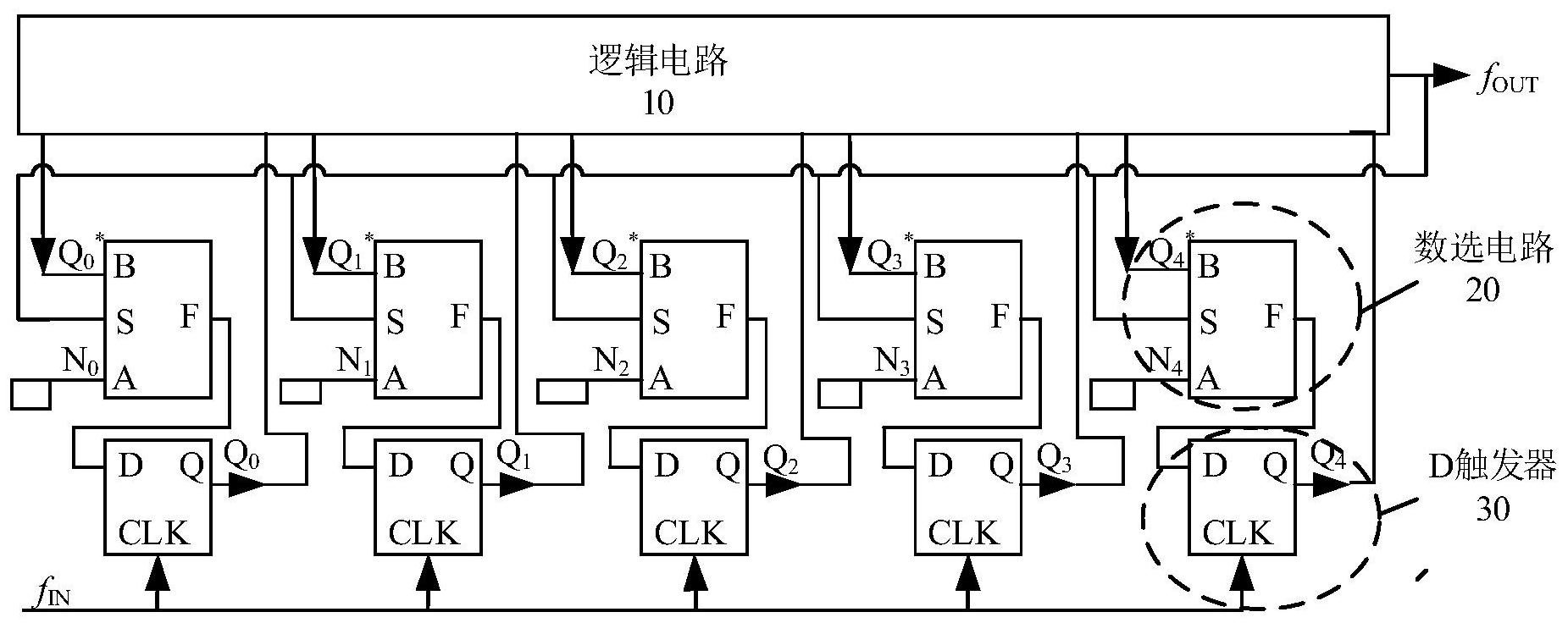

本发明的目的在于提供一种同步计数器,该同步计数器供电电压更低。 为实现上述目的,本发明采用的技术方案是,提供一种同步计数器,包括: 逻辑电路、至少两个数选电路、至少两个D触发器,所述至少两个数选电路与所述 至少两个D触发器一一对应; 所述逻辑电路的信号输入端与每个D触发器的输出端连接,所述逻辑电路的第一 信号输出端与每个数选电路的第一输入端连接,所述逻辑电路的第二信号输出端与所述每 个数选电路的地址选择输入端连接; 对于相互对应的数选电路和D触发器,所述数选电路的输出端与所述D触发器的信 号输入端连接; 每个数选电路的第二输入端用于接收同步计数器的预设电平信号,每个D触发器 的时钟输入端为同步计数器的输入端,所述逻辑电路的第二信号输出端为同步计数器的输 出端。 可选地,每个数选电路包括第一偏置电阻、第二偏置电阻、第三偏置电阻、第一数 选晶体管、第二数选晶体管、第三数选晶体管、第四数选晶体管、第五数选晶体管、第六数选 晶体管以及第七数选晶体管; 所述第一偏置电阻的第一端与所述第二偏置电阻的第一端接电源电压; 所述第一偏置电阻的第二端与所述第一数选晶体管的集电极、所述第四数选晶体 管的集电极连接,所述第二偏置电阻的第二端与所述第二数选晶体管的集电极、所述第三 数选晶体管的集电极连接; 所述第一数选晶体管的发射极与所述第二数选晶体管的发射极、所述第五数选晶 体管的集电极连接,所述第三数选晶体管的发射极与所述第四数选晶体管的发射极、所述 第六数选晶体管的集电极连接; 所述第五数选晶体管的发射极与所述第六数选晶体管的发射极、所述第七数选晶 体管的集电极连接; 所述第七数选晶体管的基极接直流偏置电压,所述第七数选晶体管的发射极与所 5 CN 111600598 A 说 明 书 2/9 页 述第三偏置电阻的第一端连接,所述第三偏置电阻的第二端接地; 所述第一数选晶体管的基极为数选电路的第二输入端,用于接收同步计数器的预 设电平信号,所述第二数选晶体管的基极用于接收第一电平信号;其中,第一电平信号为所 述同步计数器的预设电平信号的反相信号; 所述第三数选晶体管的基极为数选电路的第一输入端,用于接收逻辑电路的第一 控制信号,所述第四数选晶体管的基极用于接收第二电平信号;其中,所述第二电平信号为 所述逻辑电路的第一控制信号的反相信号; 所述第五数选晶体管的基极为数选电路的地址选择输入端,用于接收逻辑电路的 第二控制信号,所述第六数选晶体管的基极用于接收第三电平信号;其中,所述第三电平信 号为所述逻辑电路的第二控制信号的反相信号; 所述第二数选晶体管的集电极为数选电路的输出端。 可选地,所述第一数选晶体管、第二数选晶体管、第三数选晶体管、第四数选晶体 管、第五数选晶体管、第六数选晶体管以及第七数选晶体管为双极型晶体管。 可选地,所述D触发器包括第一锁存器和第二锁存器,所述第一锁存器和所述第二 锁存器电路结构相同且端口相互对应; 所述第一锁存器的第一偏置端和所述第二锁存器的第一偏置端共接电源电压,所 述第一锁存器的第二偏置端和所述第二锁存器的第二偏置端共接直流偏置电压; 所述第一锁存器的第一输入端为D触发器的信号输入端,用于接收数选电路的输 入信号,所述第一锁存器的第二输入端用于接收所述数选电路的输入信号的反相信号; 所述第二锁存器的第二输出端为D触发器的输出端,用于向逻辑电路输出状态信 号,所述第二锁存器的第一输出端用于输出所述状态信号的反相信号; 所述第一锁存器的第三输入端为D触发器的时钟输入端,用于接收时钟信号,所述 第一锁存器的第四输入端用于接收所述时钟信号的反相信号; 所述第一锁存器的第一输出端与所述第二锁存器的第二输入端连接,所述第一锁 存器的第二输出端与所述第二锁存器的第一输入端连接,所述第一锁存器的第三输入端与 所述第二锁存器的第四输入端连接,所述第一锁存器的第四输入端与所述第二锁存器的第 三输入端连接。 可选地,所述第一锁存器包括第一电阻、第二电阻、第三电阻、第四电阻、第五电 阻,第一晶体管、第二晶体管、第三晶体管、第四晶体管、第五晶体管、第六晶体管、第七晶体 管、第八晶体管、第九晶体管、第十晶体管以及第十一晶体管; 所述第一电阻的第一端、第二电阻的第一端、第八晶体管的集电极、第九晶体管的 集电极共接电源电压; 所述第一电阻的第二端与第一晶体管的集电极、第三晶体管的集电极、第四晶体 管的基极、第九晶体管的基极连接,所述第二电阻的第二端与第二晶体管的集电极、第三晶 体管的基极、第四晶体管的集电极、第八晶体管的基极连接; 所述第一晶体管的基极为第一锁存器的第一输入端,所述第二晶体管的基极为第 一锁存器的第二输入端; 所述第一晶体管的发射极与所述第二晶体管的发射极、第五晶体管的集电极连 接,所述第三晶体管的发射极与所述第四晶体管的发射极、所述第六晶体管的集电极连接; 6 CN 111600598 A 说 明 书 3/9 页 所述第五晶体管的基极为第一锁存器的第三输入端,所述第六晶体管的基极为第 一锁存器的第四输入端; 第五晶体管的发射极与第六晶体管的发射极、第七晶体管的集电极连接; 所述第七晶体管的基极、第十晶体管的基极、第十一晶体管的基极共接直流偏置 电压; 所述第七晶体管的发射极与第三电阻的第一端连接,第三电阻的第二端接地;所 述第八晶体管的发射极为第一锁存器的第一输出端,所述第八晶体管的发射极与第十晶体 管的集电极连接,所述第十晶体管的发射极与第四电阻的第一端连接,第四电阻的第二端 接地;所述第九晶体管的发射极为第一锁存器的第二输出端,所述第九晶体管的发射极与 第十一晶体管的集电极连接,第十一晶体管的发射极与第五电阻的第一端连接,第五电阻 的第二端接地。 可选地,所述第二锁存器包括第六电阻、第七电阻、第八电阻、第九电阻、第十电 阻,第十二晶体管、第十三晶体管、第十四晶体管、第十五晶体管、第十六晶体管、第十七晶 体管、第十八晶体管、第十九晶体管、第二十晶体管、第二十一晶体管以及第二十二晶体管; 所述第六电阻的第一端、第七电阻的第一端、第十九晶体管的集电极、第二十晶体 管的集电极共接电源电压; 所述第六电阻的第二端与第十二晶体管的集电极、第十四晶体管的集电极、第十 五晶体管的基极、第二十晶体管的基极连接,所述第七电阻的第二端与第十三晶体管的集 电极、第十四晶体管的基极、第十五晶体管的集电极、第十九晶体管的基极连接; 所述第十二晶体管的基极为第二锁存器的第一输入端,所述第十三晶体管的基极 为第二锁存器的第二输入端; 所述第十二晶体管的发射极与所述第十三晶体管的发射极、第十六晶体管的集电 极连接,所述第十四晶体管的发射极与所述第十五晶体管的发射极、所述第十七晶体管的 集电极连接; 所述第十六晶体管的基极为第二锁存器的第三输入端,所述第十七晶体管的基极 为第二锁存器的第四输入端; 第十六晶体管的发射极与第十七晶体管的发射极、第十八晶体管的集电极连接; 所述第十八晶体管的基极、第二十一晶体管的基极、第二十二晶体管的基极共接 直流偏置电压; 所述第十八晶体管的发射极与第八电阻的第一端连接,第八电阻的第二端接地; 所述第十九晶体管的发射极为第二锁存器的第一输出端,所述第十九晶体管的发射极与第 二十一晶体管的集电极连接,所述第二十一晶体管的发射极与第九电阻的第一端连接,第 九电阻的第二端接地;所述第二十晶体管的发射极为第二锁存器的第二输出端,所述第二 十晶体管的发射极与第二十二晶体管的集电极连接,第二十二晶体管的发射极与第十电阻 的第一端连接,第十电阻的第二端接地。 可选地,所述D触发器中的晶体管为双极型晶体管。 本发明提供的同步计数器的有益效果在于:本发明通过D触发器和数选电路实现 置位和计数功能,有效减少了D触发器中晶体管的电路级数,降低了D触发器的供电电压,进 而降低了同步计数器的供电电压。 7 CN 111600598 A 说 明 书 4/9 页 附图说明 为了更清楚地说明本发明实施例中的技术方案,下面将对实施例或现有技术描述 中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些 实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附 图获得其他的附图。 图1为本发明一实施例提供的同步计数器的结构示意图; 图2为本发明一实施例提供的数选电路的结构示意图; 图3为本发明一实施例提供的D触发器的结构示意图。