技术摘要:

本公开提供一种多气隙全阻性盲孔型探测器的制作方法,包括:步骤S1:制备基材材料,包括读出电极基材,通孔单元基材,气隙垫片,平板电极基材,漂移电极基材;步骤S2:利用步骤S1所制备的基材材料制备读出电极,平板电极,漂移电极,以及通孔单元;步骤S3:在读出电极 全部

背景技术:

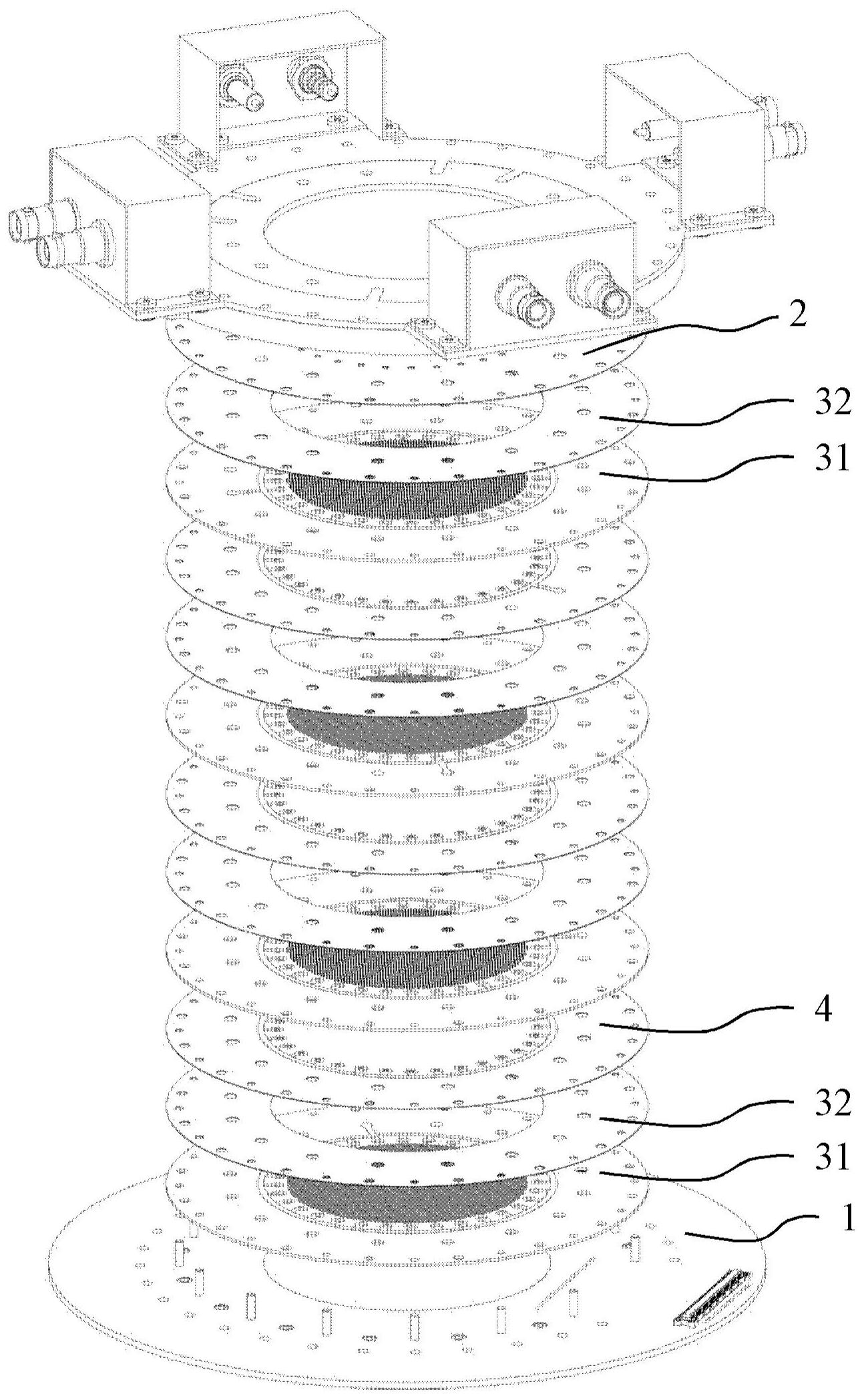

气体探测器由于其低廉的造价、较高的位置分辨以及时间分辨、很强的抗辐照能 力等性能特点而广泛应用于当前的核与粒子物理实验当中。精确的时间测量与位置测量相 结合,是核与粒子物理实验当中实现粒子鉴别最常用的方法。因此同时具有较高精度定时 以及高精度定位性能的气体探测器在核与粒子物理实验中具有极高的应用前景。目前主流 的气体探测器是能够实现高位置分辨和高计数率能力的微孔型、微网型等微结构气体探测 器,以及能够实现高时间分辨能力的多气隙平板型探测器。微结构气体探测器得益于半导 体探测器上的精细加工技术,能够实现好于100μm的位置分辨能力。但是由于微结构气体探 测器往往具有较宽的气隙作为入射粒子电离的漂移区,这就使得入射粒子在探测器的漂移 区内电离的时间统计涨落很大,单个探测器的时间分辨只能达到几个纳秒左右,无法实现 高时间分辨的性能。多气隙平板型探测器的典型代表是多气隙电阻板室,通过增加探测器 的层数,减小每一层探测器气隙厚度,从而有效降低带电粒子在气隙里面电离的时间统计 涨落,实现高达数十皮秒的时间分辨性能。但是由于多气隙电阻板室往往需要使用电阻率 很高的玻璃作为介质材料,以至于它的计数率性能较低,无法满足高计数率环境下的应用。 随着阻性镀膜技术在气体探测器领域的进一步发展,阻性电极技术已经成为下一 代微结构气体探测器的重点研究方向。阻性电极能够抑制探测器的打火放电现象,从而使 得探测器获得更高的增益,并且保证探测器能够更长时间的稳定工作。此外,阻性电极对感 应信号透明的特性,使得同时具有高位置分辨、高计数率与高时间分辨的微结构气体探测 器的制备成为了可能。通过用阻性电极取代微结构气体探测器原来的金属电极,减小漂移 区的气隙厚度,并采用多层微结构气体探测器结构,是制造出同时具有高计数率,高位置分 辨和高时间分辨探测器的一个可行方案。阻性电极对感应信号透明的特性使得每一层探测 器都能在读出电极上产生感应信号,因此可以通过漂移区气隙的减小和多层结构的使用来 有效压低带电粒子在气隙里面电离的时间统计涨落,使得探测器具有较好的时间分辨性 能。由于其工作主体仍然为微结构气体探测器,因此探测器能够有效的保留高计数率能力 和高位置分辨能力。 结合微结构气体探测器与多气隙电阻板室探测器二者的特点,欧洲核子中心 (CERN)的研究人员提出了一种快时间响应微结构气体探测器(Fast Timing MPGD,FTM)的 概念。这种探测器的工作原理是基于盲孔型GEM探测器,制备多层结构,从而同时实现高计 数率、高时间分辨、高位置分辨性能。他们制作出来的四层FTM探测器的结构如图1所示,使 用Pre-preg将双面镀有DLC的APICAL-1薄膜粘贴到读出电极PCB上,然后在APICAL-1薄膜上 腐蚀出成六角排列的均匀井型盲孔,作为第一层探测器的雪崩放大区。在第一层探测器雪 崩放大区上表面制备高度为250微米的支柱,在支柱上放置一张双面镀有DLC的APICAL-2薄 3 CN 111596341 A 说 明 书 2/7 页 膜,其下表面DLC作为第一层探测器的阻性漂移电极,上表面的DLC作为第二层探测器雪崩 放大区的井型底。紧接着在APICAL-2薄膜上放置一张单面镀有DLC的APICAL-3薄膜,使得镀 有DLC的一面远离APICAL-2薄膜。在APICL-3薄膜上腐蚀出成六角排列的孔,作为第二层探 测器的雪崩放大区。依次可以制备出第三、四层探测器结构。最后在第四层探测器结构的支 柱上放置一张单面镀有DLC的APICAL-4薄膜,使得镀有DLC的一面靠近第四层探测器雪崩放 大区,作为第四层探测器的漂移电极。 根据现有技术制备出来的探测器技术方案主要存在以下几个缺点:第一,由于其 关键部件是基于厚度为50μm的APICAL基材加工制作的,这种材料相当柔软,无法实现自支 撑。为了保证探测器内部的各个气隙保持较好的均匀性,需要在每个气隙使用支柱来支撑 放大单元和漂移电极,因此会给探测器的安装制作带来很大的难度。第二,当最小电离粒子 穿过探测器时,会在每一层探测器的漂移区内发生原初电离,产生原初电子。原初电子再漂 移到雪崩放大区进行雪崩放大。由感应信号的Ramo定理可知,由于阻性电极的存在,每一层 探测器发生雪崩放大时都能在读出电极PCB上感应出信号,且感应信号的幅度正比于H/D。 其中H是电子雪崩区的厚度,为50μm,D为探测器的总厚度。总的感应信号幅度为各层探测器 在读出电极PCB上单独感应信号的总和。为了保证探测器的探测效率,探测器每层的漂移区 厚度一般要大于250μm,这样使得PCB上的感应信号强度较弱。目前,按照现有技术加工出来 的探测器的感应信号幅度非常小,以至于读出电子学无法区分信号和本底噪声,因此现有 技术根本无法投入实际应用。 公开内容 (一)要解决的技术问题 基于上述问题,本公开提供了一种多气隙全阻性盲孔型探测器的制作方法,以缓 解现有技术中微结构气体探测器制作困难,感应信号幅度非常小,以至于读出电子学无法 区分信号和本底噪声,无法投入实际应用等技术问题。 (二)技术方案 本公开提供一种多气隙全阻性盲孔型探测器的制作方法,包括: 步骤S1:制备基材材料,包括读出电极基材,通孔单元基材,气隙垫片,平板电极基 材,漂移电极基材; 步骤S2:利用步骤S1所制备的基材材料制备读出电极,平板电极,漂移电极,以及 通孔单元; 步骤S3:在读出电极上依次交替安装通孔单元区和平板电极,直至安装至第N层通 孔单元区,N≥2,得到全阻性盲孔型放大区;以及 步骤S4:在步骤S3所制备的全阻性盲孔型放大区上方安装漂移电极和窗,完成多 气隙全阻性盲孔型探测器的制作。 在本公开实施例中,步骤S2包括: 子步骤S21:在读出电极基材上表面制备DLC薄膜得到读出电极; 子步骤S22:在平板电极基材的上下表面制备DLC薄膜得到平板电极; 子步骤S23:在漂移电极基材的下表面制备DLC薄膜得到漂移电极;以及 子步骤S24:在通孔单元基材的上表面制备DLC薄膜后制作小孔阵列,得到通孔单 元。 4 CN 111596341 A 说 明 书 3/7 页 在本公开实施例中,读出电极的上表面DLC的厚度在40nm~1μm之间,面电阻率在 10MΩ/□~2GΩ/□之间。 在本公开实施例中,漂移电极的下表面的DLC厚度在40nm~1μm之间,面电阻率在 50MΩ/□~10GΩ/□。 在本公开实施例中,平板电极的上下表面的DLC厚度在40nm~1μm之间,面电阻率 在50MΩ/□~10GΩ/□。 在本公开实施例中,通孔单元的上表面DLC厚度在40nm~1μm之间;面电阻率在50M Ω/□~10GΩ/□。 在本公开实施例中,通孔单元中小孔阵列中小孔的孔径在0.2mm~0.8mm之间,小 孔之间的间距在0.4mm~1.6mm之间。 在本公开实施例中,步骤S3,包括: 子步骤S31:在读出电极上安装定位针; 子步骤S32:通过定位针在读出电极上安装第一层通孔单元区; 子步骤S33:在第一层通孔单元区上安装第一层平板电极;以及 子步骤S34:在第一层平板电极上继续安装第二层通孔单元区以及第二层平板电 极,直至安装至第N层通孔单元区,完成全阻性盲孔型放大区的制备。 在本公开实施例中,通孔单元基材为双层板,厚度在0.15mm~0.8mm之间。 在本公开实施例中,气隙垫片厚度在0.2mm~1mm之间。 (三)有益效果 从上述技术方案可以看出,本公开多气隙全阻性盲孔型探测器的制作方法至少具 有以下有益效果其中之一或其中一部分: (1)在有效减小每一层漂移区气隙厚度的情况下,能够使探测器在保持高增益,高 计数率,高位置分辨的前提下有效压低入射粒子在探测器里电离时间的涨落,实现高时间 分辨性能; (2)每一层探测器在读出板上均能产生感应信号; (3)增大了雪崩区的厚度,既提高了探测器的增益,又提高了探测器的感应信号幅 度,使得感应信号强度极大增强; (4)PCB基材硬度大,能够有效的进行自支撑等优势,能够极大的简化探测器的设 计与安装制作。 附图说明 图1为现有技术中四层FTM探测器的剖面结构示意图。 图2为本公开实施例多气隙全阻性盲孔型探测器的局部剖面结构示意图。 图3为本公开实施例多气隙全阻性盲孔型探测器的立体结构分解图。 图4为本公开实施例多气隙全阻性盲孔型探测器的制作方法的流程示意图。 【附图中本公开实施例主要元件符号说明】 1-读出电极; 2-漂移电极; 3-通孔单元区; 5 CN 111596341 A 说 明 书 4/7 页 31-通孔单元; 32-气隙垫片; 4-平板电极。

技术实现要素:

本公开提供了一种多气隙全阻性盲孔型探测器的制作方法,使得制作出来的探测 器具有足够大的增益,而且能够同时实现高计数率、高位置分辨、高时间分辨性能;此外本 公开的方法能大幅度简化探测器的加工制作工艺,降低探测器的制作成本。因此本公开的 基于多气隙全阻性盲孔型探测器制作方法能够有效克服现有技术方案的缺陷,为微结构气 体探测器在新一代对撞机实验中的应用提供技术支持。 在本公开实施例中,结合图2和图3所示,探测器的结构从下往上依次为读出电极 1,全阻性盲孔型放大结构区,以及漂移电极2。 所述全阻性盲孔型放大区包括多层通孔单元区3,以及位于上下相邻通孔单元区3 之间的平板电极4。每层通孔单元区3包括一通孔单元31以及位于其上的气隙垫片32。所述 平板电极4的上下表面均设置有DLC薄膜。所述通孔单元31上表面为DLC薄膜,并设置有密排 的小孔阵列。 每个通孔单元31跟其上方的平板电极4形成漂移区,其中通孔单元31上方平板电 极4下表面的DLC与通孔单元31上表面的DLC之间的电压差为漂移区工作电压。气隙垫片垫 用来提供漂移区的气隙。 每个通孔单元31跟其下方的平板电极4形成具有盲孔型的放大单元,其中通孔单 元31上表面的DLC与其下方平板电极4上表面的DLC之间的电压差为具有盲孔的放大单元工 作电压。 这样每层通孔单元31,和位于该通孔单元31上的平板电极4下表面的DLC薄膜,以 及位于该通孔单元31下的平板电极4上表面的DLC薄膜,就构成了一层独立的全阻性盲孔型 放大结构。其中,第一层通孔单元31由于靠近读出电极PCB,因此不需要独立的平板电极4来 形成盲孔,可以直接坐落在读出电极PCB上表面的DLC上来形成具有盲孔的放大单元。由于 需要一个金属电极来和读出电极一起提供产生感应信号所必须的权场,因此位于顶层最上 方的漂移电极2,其中间层有一层铜电极;此外由于最上层(图示第N层)通孔单元31的漂移 电极位于所有层的上方,因此只需漂移电极2下表面有DLC。 为使本公开的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照 附图,对本公开进一步详细说明。 在本公开实施例中,提供一种多气隙全阻性盲孔型探测器的制作方法,结合图2至 图3所示,所述制作方法,包括: 步骤S1:制备基材材料,包括读出电极基材,通孔单元基材,气隙垫片,平板电极基 材,漂移电极基材; 使用通用PCB工艺制备出读出电极,通孔单元基材,气隙垫片,平板电极基材,漂移 电极基材。读出电极PCB为多层板,读出电极的形状根据应用需求可以采用条状或者Pad状, 电极位于PCB的中间层。通孔单元基材为双层板,厚度在0.15mm~0.8mm之间,用于制作通孔 单元。气隙垫片PCB为0层板,即PCB板上面没有任何金属存在,仅作为提供特定的气隙厚度 6 CN 111596341 A 说 明 书 5/7 页 使用,气隙垫片厚度在0.2mm~1mm之间。平板电极基材PCB为双层板,厚度在0.15mm~1mm之 间。漂移电极基材PCB为多层板,铜电极可以位于PCB的中间层,厚度在0.15mm~1mm之间。 读出电极的有效面积为5cm×5cm,根据应用需求可以采用条状或者Pad状读出,在 该实施例中优选二维条状读出,条间距为400μm。通孔单元基材的厚度优选0.4mm。气隙垫片 优选0.2mm。平板电极基材PCB厚度优选0.2mm。漂移电极基材厚度优选0.2mm,其中铜电极位 于PCB的中间层。 步骤S2:利用步骤S1所制备的基材材料制备读出电极1,平板电极4,漂移电极2,以 及通孔单元31; 步骤S2包括: 子步骤S21:在读出电极基材上表面制备DLC薄膜得到读出电极1; 子步骤S22:在板电极基材的上下表面制备DLC薄膜得到平板电极4; 子步骤S23:在漂移电极基材的下表面制备DLC薄膜得到漂移电极2; 子步骤S24:在通孔单元基材的上表面制备DLC薄膜后制作小孔阵列,得到通孔单 元31。 通过磁控溅射法在读出电极基材的上表面、通孔单元基材的上表面、平板电极基 材的上下表面,漂移电极基材的下表面沉积阻性DLC薄膜。DLC薄膜的厚度在40nm到1μm间, 其面电阻率根据不同应用需求而定,可以通过修改磁控溅射制备过程中的参数,如腔体真 空度、靶电流、掺杂或沉积时间中的至少一项,来得到具有不同面电阻率的DLC。读出电极1 的上表面DLC的厚度在40nm~1μm之间,优选值为400nm,面电阻率在10MΩ/□~2GΩ/□之 间,优选值为140MΩ/□。通孔单元基材的上表面DLC厚度在40nm~1μm之间,优选值为 400nm,面电阻率在50MΩ/□~10GΩ/□,优选值为1GΩ/□。平板电极基材的上下表面、漂 移电极基材的下表面的DLC厚度在40nm~1μm之间,优选值为400nm,面电阻率在50MΩ/□~ 10GΩ/□,优选值为2GΩ/□。 将镀好DLC的通孔单元基材送回PCB工厂,在沉积有DLC的区域内部使用机械钻孔 方式制作六角密排的小孔阵列,小孔的孔径根据应用需求在0.2mm~0.8mm之间,优选为 0.5mm,小孔之间的间距在0.4mm~1.6mm之间,优选为1mm。 步骤S3:在读出电极1上依次交替安装通孔单元区3和平板电极4,直至安装至第N (N≥2)层通孔单元区3,得到全阻性盲孔型放大区; 将以上几步得到的所有部件放在酒精中进行超声清洗10分钟~20分钟,然后使用 无尘布擦干表面,并将所有部件放置于烘箱中烘干,烘箱温度设置为70度。 所述步骤S3,包括: 子步骤S31:在读出电极1上安装定位针; 将读出电极1的读出板固定好,然后在读出板定位孔上安装定位针,如图3所示。 子步骤S32:通过定位针在读出电极1上安装第一层通孔单元区3; 通过定位针将第一层通孔单元31安装在读出板上方,在第一层通孔单元31边缘处 安装第一层气隙垫片32后得到第一层通孔单元区3。然后通过定位针在第一层放大单元上 边缘处安装第一层气隙垫片32,给第一层放大区提供漂移区气隙,完成第一层通孔单元区3 的制备。 根据应用需求气隙垫片可以安装一张或者多张堆叠,具体根据气隙垫片32厚度以 7 CN 111596341 A 说 明 书 6/7 页 及应用要求的气隙厚度来决定;在本实施案例中,优选的气隙垫片32为5张,形成的气隙厚 度为1mm。 子步骤S33:在第一层通孔单元区3上安装第一层平板电极4; 通过定位针在第一层通孔单元区3的气隙垫片32上安装第一层平板电极4; 子步骤S34:在第一层平板电极4上继续安装第二层通孔单元区3以及第二层平板 电极4,直至安装至第N层通孔单元区3,完成全阻性盲孔型放大区的制备; 在本公开实施例中,全阻性盲孔型放大区包括四层通孔单元区3以及三层平板电 极,完成其余三层通孔单元区3的安装,直到最顶层通孔单元区3的气隙垫片32安装完成,得 到全阻性盲孔型放大区。 步骤S4:在步骤S3所制备的全阻性盲孔型放大区上制备漂移电极2,完成多气隙全 阻性盲孔型探测器的制作。 在最上层的通孔单元31的气隙垫片32上方安装漂移电极2;然后安装探测器的气 框,窗,高压接头等其他常规部件(最上层的通孔单元31上方的所有部件),完成多气隙全阻 性盲孔型探测器的制作,如图3所示。 至此,已经结合附图对本公开实施例进行了详细描述。需要说明的是,在附图或说 明书正文中,未绘示或描述的实现方式,均为所属技术领域中普通技术人员所知的形式,并 未进行详细说明。此外,上述对各元件和方法的定义并不仅限于实施例中提到的各种具体 结构、形状或方式,本领域普通技术人员可对其进行简单地更改或替换。 依据以上描述,本领域技术人员应当对本公开多气隙全阻性盲孔型探测器的制作 方法有了清楚的认识。 综上所述,本公开提供了一种多气隙全阻性盲孔型探测器的制作方法,通过结合 厚型电子倍增器与多气隙电阻板室的优势,充分利用厚型电子倍增器的优点,在有效减小 漂移区气隙厚度的情况下,采用阻性电极技术以及多层结构,能够使探测器在保持高增益, 高计数率,高位置分辨的前提下有效压低入射粒子在探测器里电离时间的涨落,实现高时 间分辨性能。本技术使用了全阻性电极方案,将探测器内部位于漂移电极2和读出电极1之 间的电极全部采用类金刚石碳基薄膜阻性电极,使得每一层探测器在读出板上均能产生感 应信号。本技术使用盲孔型的THGEM作为雪崩放大单元,相比于CERN提出的FTM技术方案,本 技术方案基于PCB板基材,增大了雪崩区的厚度,既提高了探测器的增益,又提高了探测器 的感应信号幅度,使得感应信号强度极大增强,抗打火能力强。此外由于PCB基材硬度大,能 够有效的进行自支撑等优势,能够极大的简化探测器的设计与安装制作。同时保持高增益, 高计数率,高位置分辨的前提下能够同时实现较高的时间分辨。 还需要说明的是,实施例中提到的方向用语,例如“上”、“下”、“前”、“后”、“左”、 “右”等,仅是参考附图的方向,并非用来限制本公开的保护范围。贯穿附图,相同的元素由 相同或相近的附图标记来表示。在可能导致对本公开的理解造成混淆时,将省略常规结构 或构造。 并且图中各部件的形状和尺寸不反映真实大小和比例,而仅示意本公开实施例的 内容。另外,在权利要求中,不应将位于括号之间的任何参考符号构造成对权利要求的限 制。 除非有所知名为相反之意,本说明书及所附权利要求中的数值参数是近似值,能 8 CN 111596341 A 说 明 书 7/7 页 够根据通过本公开的内容所得的所需特性改变。具体而言,所有使用于说明书及权利要求 中表示组成的含量、反应条件等等的数字,应理解为在所有情况中是受到「约」的用语所修 饰。一般情况下,其表达的含义是指包含由特定数量在一些实施例中±10%的变化、在一些 实施例中±5%的变化、在一些实施例中±1%的变化、在一些实施例中±0.5%的变化。 再者,单词“包含”不排除存在未列在权利要求中的元件或步骤。位于元件之前的 单词“一”或“一个”不排除存在多个这样的元件。 说明书与权利要求中所使用的序数例如“第一”、“第二”、“第三”等的用词,以修饰 相应的元件,其本身并不意味着该元件有任何的序数,也不代表某一元件与另一元件的顺 序、或是制造方法上的顺序,该些序数的使用仅用来使具有某命名的一元件得以和另一具 有相同命名的元件能做出清楚区分。 此外,除非特别描述或必须依序发生的步骤,上述步骤的顺序并无限制于以上所 列,且可根据所需设计而变化或重新安排。并且上述实施例可基于设计及可靠度的考虑,彼 此混合搭配使用或与其他实施例混合搭配使用,即不同实施例中的技术特征可以自由组合 形成更多的实施例。 本领域那些技术人员可以理解,可以对实施例中的设备中的模块进行自适应性地 改变并且把它们设置在与该实施例不同的一个或多个设备中。可以把实施例中的模块或单 元或组件组合成一个模块或单元或组件,以及此外可以把它们分成多个子模块或子单元或 子组件。除了这样的特征和/或过程或者单元中的至少一些是相互排斥之外,可以采用任何 组合对本说明书(包括伴随的权利要求、摘要和附图)中公开的所有特征以及如此公开的任 何方法或者设备的所有过程或单元进行组合。除非另外明确陈述,本说明书(包括伴随的权 利要求、摘要和附图)中公开的每个特征可以由提供相同、等同或相似目的的替代特征来代 替。并且,在列举了若干装置的单元权利要求中,这些装置中的若干个可以是通过同一个硬 件项来具体体现。 类似地,应当理解,为了精简本公开并帮助理解各个公开方面中的一个或多个,在 上面对本公开的示例性实施例的描述中,本公开的各个特征有时被一起分组到单个实施 例、图、或者对其的描述中。然而,并不应将该公开的方法解释成反映如下意图:即所要求保 护的本公开要求比在每个权利要求中所明确记载的特征更多的特征。更确切地说,如下面 的权利要求书所反映的那样,公开方面在于少于前面公开的单个实施例的所有特征。因此, 遵循