技术摘要:

本发明公开了一种局部带宽增强的转接板封装结构,包括:基板;第一介质层,所述第一介质层设置在所述基板的上面;芯片,所述芯片的正面朝上埋入设置在所述第一介质层中,所述芯片具有第一焊盘和相对第一焊盘尺寸更大的第二焊盘;第二介质层,所述第二介质层设置成覆盖 全部

背景技术:

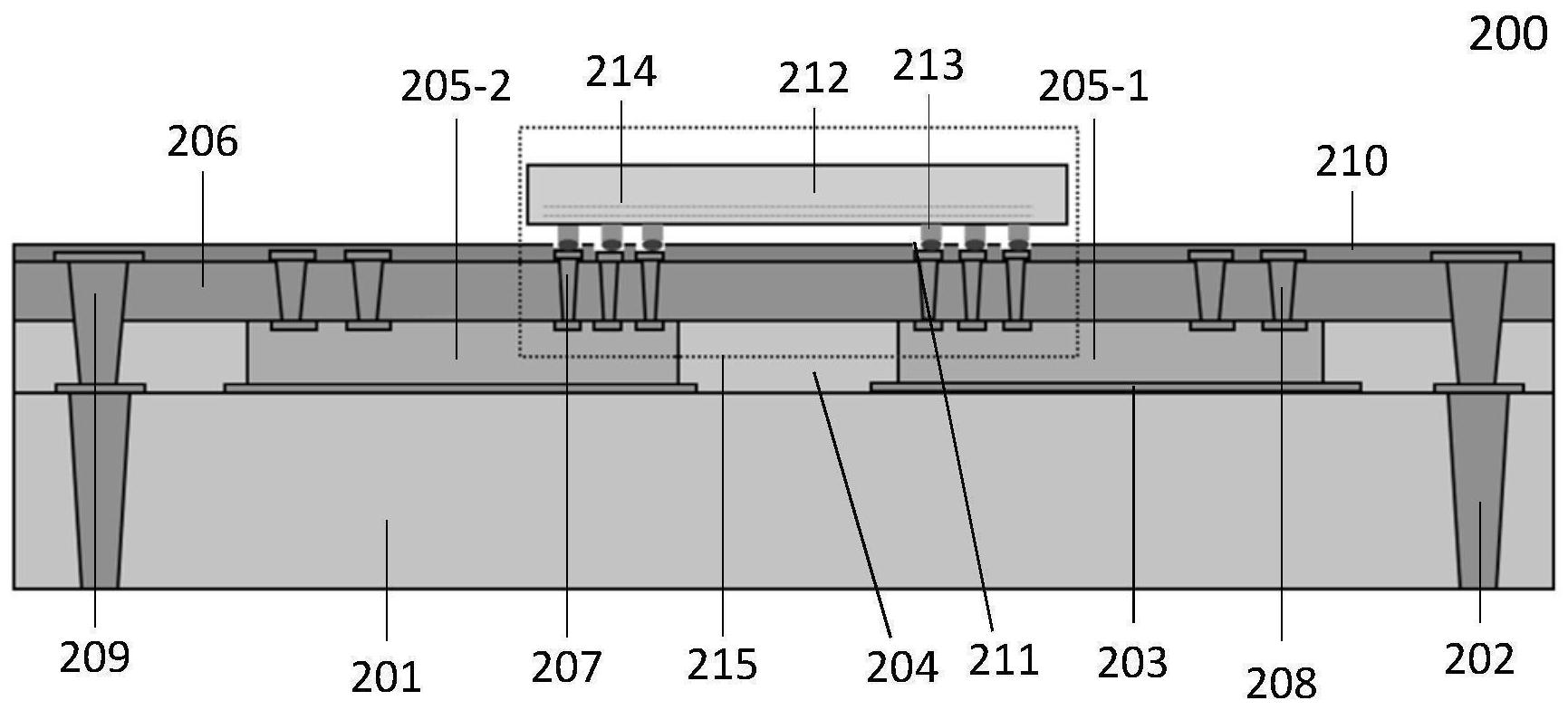

随着芯片向小型化、高性能方向发展,高密度、多芯片封装技术成为重要的解决方 案。在目前高密度封装结构中,一般通过带有TSV(Through SiliconVia)的硅转接板 (Interposer)来实现多个异质芯片间的高带宽通信以及芯片与基板间的高密度互联。转接 板目前已经成为纳米级集成电路与毫米级宏观基板之间电信号连接最有效的手段之一,它 通常是指芯片与封装基板之间的互连和引脚再分布的功能层。转接板通过再分布层(RDLs) 可以将密集的I/O引线进行再分布,通过在转接板内部形成TSV来实现垂直贯通,从而实现 芯片与芯片间高带宽通信以及芯片与基板间的高密度互连。然而,硅转接板由于需要制作 TSV,工艺较为复杂,成本较高,且形成高深宽比的TSV良率较低,这也是TSV技术大规模推广 的主要阻碍因素。所以,如何在不通过利用带有TSV的硅转接板的情况下,实现多个异质芯 片间的高速高带宽通信是目前研究的一个重点方向。 英特尔公司(Intel)的EMIB技术(Embedded Multi-Die InterconnectBridge),采 用无TSV的转接板实现多个异质芯片间的高速互联。如图1所示是EMIB的结构示意图,通过 将Si桥埋入有机基板,压合基板介质材料,然后介质层开孔、孔金属化引出至基板表面,最 后将多个芯片与基板键合,从而实现芯片间的高速互联通信。其中,英特尔公司目前可做到 在有机基板介质层上开孔孔径小于40微米,间距小于60微米(图中Cu Pillar Ball),从而 局部可实现高密度的互联(500-1000IO/mm/layer),所以在有机基板上是可以做这种局部 高密度的孔径和焊盘的。 但是,英特尔公司(Intel)的EMIB工艺是将转接板埋入基板,将转接板上的焊盘引 出至基板表面后和芯片键合。那么在基板表面就存在了两种不同尺寸和类型的焊盘(窄节 距和宽节距,如图1右下所示的焊盘),对应的在芯片表面(如图1右上所示)也会有两种不同 类型的Bumping,窄节距Bumping一般为Cu pillar Ball的形式,而宽节距Bumping一般用 Solder Ball的形式。带有不同类型Bumping的芯片和基板焊盘键合过程中,相同的压力下 芯片左右两侧Bumping的形变和受力状态是不同的,容易导致芯片与基板键合失效,也容易 损伤芯片上的器件。 针对现有技术无TSV的转接板实现多个异质芯片间的高速互联技术存在的芯片同 时存在两种类型焊球,焊接时存在形变和受力差别导致芯片与基板键合失效,容易损伤芯 片上的器件等问题,本发明提出一种局部带宽增强的转接板封装结构及制作方法,通过在 基板中埋入芯片,然后再进行无TSV转接板的压合,至少部分的克服了上述现有技术存在的 问题。 4 CN 111554676 A 说 明 书 2/7 页

技术实现要素:

针对现有技术无TSV的转接板实现多个异质芯片间的高速互联技术存在的芯片同 时存在两种类型焊球,焊接时存在形变和受力差别导致芯片与基板键合失效,容易损伤芯 片上的器件等问题,根据本发明的一个实施例,提供一种局部带宽增强的转接板封装结构, 包括: 基板; 第一介质层,所述第一介质层设置在所述基板的上面; 芯片,所述芯片的正面朝上埋入设置在所述第一介质层中,所述芯片具有第一焊 盘和相对第一焊盘尺寸更大的第二焊盘; 第二介质层,所述第二介质层设置成覆盖所述第一介质层和所述芯片; 第一金属通孔,所述第一金属通孔贯穿所述第二介质层,电连接至所述芯片的第 一焊盘; 第二金属通孔,所述第二金属通孔贯穿所述第二介质层,电连接至所述芯片的第 二焊盘; 阻焊层,所述阻焊层覆盖所述第二介质层和所述第二金属通孔,并漏出所述第一 金属通孔的外接焊盘;以及 转接板,所述转接板倒装焊接至所述第一金属通孔的外接焊盘上。 在本发明的一个实施例中,所述基板还包括基板金属化过孔、基板金属层,所述芯 片设置在所述基板金属层上方。 在本发明的一个实施例中,局部带宽增强的转接板封装结构还包括第三金属通 孔,所述第三金属通孔贯穿所述第二介质层和所述第一介质层,电连接至所述基板的所述 金属化过孔。 在本发明的一个实施例中,所述第一介质层和或所述第二介质层的材料为光敏性 质的介质材料。 在本发明的一个实施例中,所述芯片的数量为N,其中N≥2。 在本发明的一个实施例中,所述第一金属通孔的直径不大于40微米。 在本发明的一个实施例中,所述转接板具有至少一层重新布局布线层和高密度焊 接结构,所述高密度焊接结构的尺寸与所述第一金属通孔的尺寸匹配。 在本发明的一个实施例中,所述转接板上的高密度焊接结构为铜柱(Copper Pillar)和位于铜柱头部的焊锡层构成。 根据本发明的另一个实施例中,提供一种局部带宽增强的转接板封装结构的制作 方法,包括: 在带金属过孔和表面金属层的基板上形成第一介质层; 在第一介质层中形成芯片埋入腔; 在芯片埋入腔内贴片埋入芯片,所述芯片具有第一焊盘和相对第一焊盘尺寸更大 的第二焊盘; 在芯片和第一介质层上形成第二介质层; 贯穿第二介质层中形成连通芯片第一焊盘的第一通孔408和连通芯片第二焊盘的 第二通孔,贯穿第二介质层和第一介质层中形成基板通孔; 5 CN 111554676 A 说 明 书 3/7 页 对第一通孔、第二通孔、基板通孔进行金属化导电填充,形成第一金属通孔、第二 金属通孔和第三金属通孔; 在第二介质层上表面和第一金属通孔、第二金属通孔、第三金属通孔顶部焊盘上 形成阻焊层,并在第一金属通孔位置形成阻焊层开口,漏出高密度焊盘;以及 将转接板倒装焊接至高密度焊盘,形成高密度互连区域。 在本发明的另一个实施例中,埋入所述芯片的数量为M,其中M≥2,所述转接板具 有至少一层重新布局布线层和高密度焊接结构,所述高密度焊接结构的尺寸与所述高密度 焊盘的尺寸匹配。 本发明提供一种局部带宽增强的转接板封装结构及制作方法,需要进行互联封装 的芯片具有大小、密度不同的两种类型的焊盘,其中第一焊盘为高密度、小尺寸焊盘,第二 焊盘为一般基板盲孔尺寸焊盘,首先将芯片埋入基板,然后通过介质层对埋入芯片的基板 进行重构,接下来进行芯片高密度焊盘引出,最后将带重新布局布线层的转接板与芯片进 行键合连接形成局部带宽增强的转接板封装结构。基于本发明提供的该种局部带宽增强的 转接板封装结构及制作方法具有如下优点:1)通过外置转接板(硅片、玻璃等)完成异质芯 片间在局部区域的互联,实现局部带宽增强,不影响封装体其他部分结构;2)转接板上无 TSV、TGV,只需在其表面形成至少一层的重布线(RDLs,Redistributionlayers)、接触焊盘 (Contact Pad)和高密度焊接结构,工艺简单,成本较低;3)由于转接板只和芯片之间在局 部区域实现互联,故芯片面积可以远大于转接板的面积,对于缩小整个封装体面积具有重 要意义;4)芯片埋入到基板中能降低芯片键合过程中受损的可能性。 附图说明 为了进一步阐明本发明的各实施例的以上和其它优点和特征,将参考附图来呈现 本发明的各实施例的更具体的描述。可以理解,这些附图只描绘本发明的典型实施例,因此 将不被认为是对其范围的限制。在附图中,为了清楚明了,相同或相应的部件将用相同或类 似的标记表示。 图1示出现有技术的一种无TSV的转接板实现多个异质芯片间的高速互联芯片封 装结构的示意图。 图2示出根据本发明的一个实施例形成的一种局部带宽增强的转接板封装结构 200的剖面示意图。 图3示出根据本发明的一个实施例形成的一种局部带宽增强的转接板封装结构 200的俯视图。 图4A至图4H示出根据本发明的一个实施例形成该局部带宽增强的转接板封装结 构200的过程剖面示意图。 图5示出根据本发明的一个实施例形成该局部带宽增强的转接板封装结构200的 方法的流程图500。