技术摘要:

本发明提供了一种电磁干扰低的功率器件终端结构,所述终端结构包括:从下至上依次层叠设置的金属化漏极、第一导电类型半导体衬底和第一导电类型半导体外延层,以及第二导电类型半导体主结、第二导电类型半导体等位环、第一导电类型截止环、第二导电类型半导体场限环、 全部

背景技术:

通常,功率器件的典型应用环境是开关电源,为满足开关电源小型化需求,其本身 的开关频率和功率密度不断提高,模块化和功能集成可以提高电子元器件的功率密度,但 也会产生越来越复杂的内部电磁境。功率器件在快速开关转换状态下,其电压和电流在短 时间内急剧变化,产生高的dv/dt和di/dt,成为一个很强的电磁干扰源。 在电磁干扰(EMI)抑制技术方面,一是从电路传导途径方面来减弱高频高幅值的 电磁干扰,例如通过EMI滤波器的设计,可有效抑制共模干扰和差模干扰,但只能局限于滤 除某一频段内的高频杂波。二是从器件设计方面改善寄生电容,但容易增大器件开关损耗 或增加器件工艺步骤。

技术实现要素:

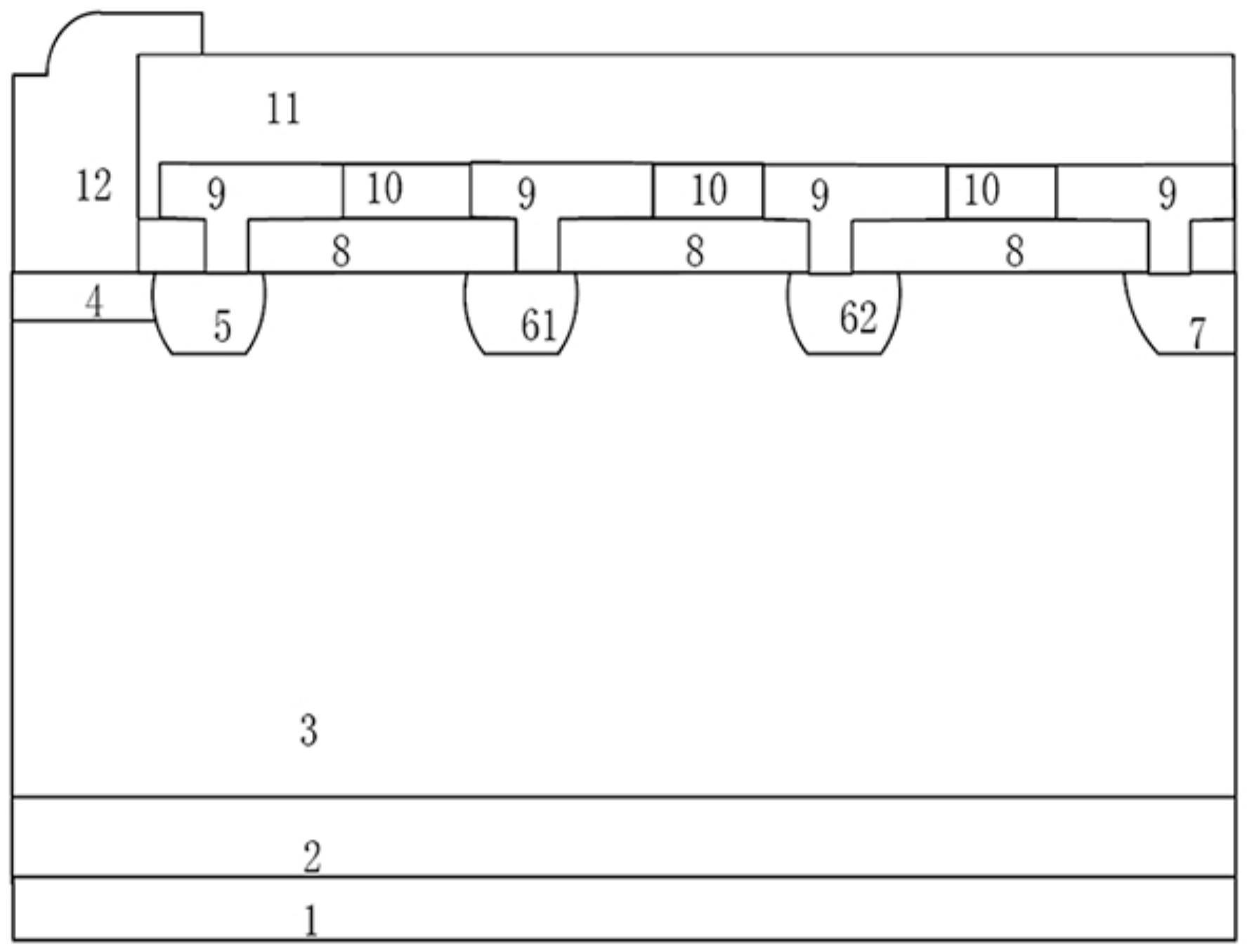

本发明的目的在于解决现有技术存在的上述不足中的至少一项。 为了实现上述目的,本发明的目的之一在于提供一种能够降低电磁干扰的功率器 件终端结构。 为了实现上述目的,本发明提供了一种电磁干扰低的功率器件终端结构,所述电 磁干扰低的功率器件终端结构包括:从下至上依次层叠设置的金属化漏极、第一导电类型 半导体衬底和第一导电类型半导体外延层,以及第二导电类型半导体主结、第二导电类型 半导体等位环、第一导电类型截止环、第二导电类型半导体场限环、第一介质层、第二介质 层、第三介质层、导电场板和金属化源极,其中,第二导电类型半导体主结、第二导电类型半 导体等位环和第一导电类型截止环设置在所述第一导电类型半导体外延层上部,且所述第 二导电类型半导体主结与位于其正上方的金属化源极直接接触,所述第二导电类型半导体 等位环与所述第二导电类型半导体主结相接触,所述第一导电类型截止环位于远离第二导 电类型半导体主结的远端一侧;所述第二导电类型半导体场限环嵌入地设置在第一导电类 型半导体外延层上部且位于所述第二导电类型半导体等位环与第一导电类型截止环之间; 多个彼此相隔的第一介质层设置在第一导电类型半导体外延层上,且暴露出第二导电类型 半导体等位环、第二导电类型半导体场限环和第一导电类型截止环,且每个第一介质层上 表面上相应设置有一个第二介质层,同时所述多个彼此相隔的第一介质层中每两个相邻的 第一介质层之间设置有一个导电场板;第三介质层覆盖所有第二介质层的上表面和所有导 电场板的上表面。 在本发明的一个示例性实施例中,所述金属化源极可设置在第二导电类型半导体 主结上。 在本发明的一个示例性实施例中,所述第二导电类型半导体场限环的数量可以为 一个或彼此相隔的两个以上。 3 CN 111554677 A 说 明 书 2/5 页 在本发明的一个示例性实施例中,所述第一导电类型半导体衬底的掺杂程度可大 于第一导电类型半导体外延层。 在本发明的一个示例性实施例中,所述导电场板可以为T型。此外,所述导电场板 为T型多晶硅场板。 在本发明的一个示例性实施例中,所述第二介质层的介电常数可高于二氧化硅。 与现有技术相比,本发明的有益效果包括:能够在场限环和场板之间引入HK介质 层,由半导体场限环、HK介质层和场板构成MIS电容结构,并与相邻的多晶硅电阻串联,从而 在源极和漏极高电位之间形成了RC吸收网络,能够有效抑制功率器件在快速开关中产生的 dv/dt和di/dt,缓解EMI噪声。 附图说明 图1示出了本发明电磁干扰低的功率器件终端结构的一个示例性实施例的结构示 意图; 图2示出了本发明电磁干扰低的功率器件终端结构的一个示例性实施例的RC网络 等效电路图; 图3~图6分别示出了本发明电磁干扰低的功率器件终端结构的一个示例性实施 例的制造工艺的流程示意图。 附图标记说明如下: 金属化漏极1,第一导电类型半导体衬底2,第一导电类型半导体外延层3,第二导 电类型半导体主结4,第二导电类型半导体等位环5,第二导电类型半导体场限环61和62,第 一导电类型截止环7,第一介质层8,导电场板9,第二介质层10,第三介质层11和金属化源极 12。