技术摘要:

本发明实施例公开了一种PCIe设备的兼容处理方法、装置、设备及存储介质。所述方法包括:依据PCIe根设备支持的地址位宽与目标PCIe端设备支持的地址位宽,确定分配给所述目标PCIe端设备的目标地址位宽和目标Bar空间;依据分配的目标地址位宽和目标Bar空间进行PCIe兼容配 全部

背景技术:

PCIe是一种高速串行计算机扩展总线标准,属于高速串行点对点双通道高带宽传 输。在实际应用中,PCIe设备之间通过PCIe链路连接,但由于不同地址位宽的RC设备与EP设 备不兼容,会导致RC设备与EP设备无法正常通信并完成相应业务功能。而,如果不使用PCIe 链路传输而使用其他的通用接口,不仅会造成硬件成本高,而且其他的通用接口的传输速 度比较慢,影响数据传输速度。因此,需要迫切解决上述不兼容问题。

技术实现要素:

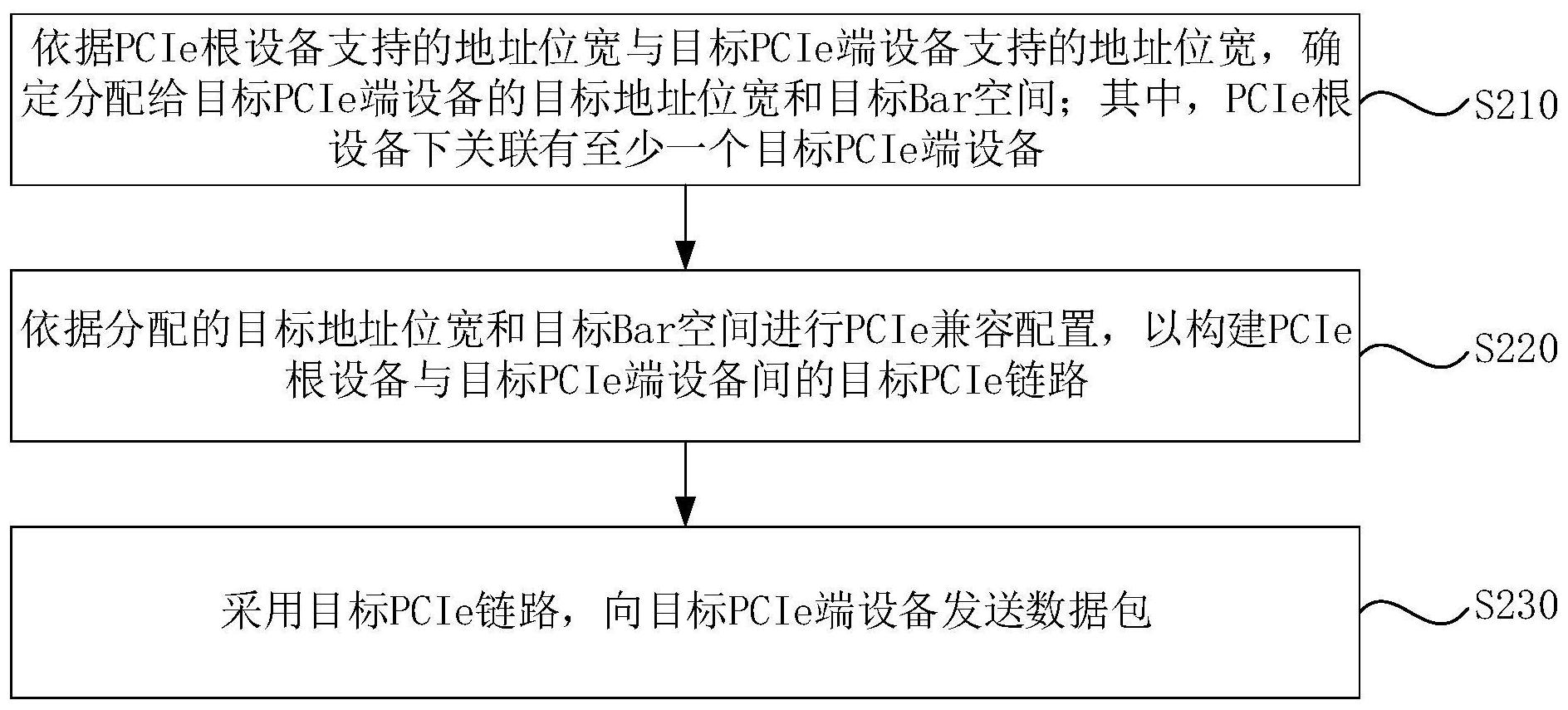

鉴于上述问题,本发明实施例中提供了一种PCIe设备的兼容处理方法、装置、设备 及存储介质,以实现RC设备与EP设备之间的通信兼容。 第一方面,本发明实施例中提供了一种PCIe设备的兼容处理方法,由PCIe根设备 执行,所述PCIe根设备下关联有至少一个目标PCIe端设备,包括: 依据PCIe根设备支持的地址位宽与目标PCIe端设备支持的地址位宽,确定分配给 所述目标PCIe端设备的目标地址位宽和目标Bar空间; 依据分配的目标地址位宽和目标Bar空间进行PCIe兼容配置,以构建所述PCIe根 设备与所述目标PCIe端设备间的目标PCIe链路; 采用目标PCIe链路,向所述目标PCIe端设备发送数据包。 第二方面,本发明实施例中还提供了一种PCIe设备的兼容处理装置,配置于PCIe 根设备,所述PCIe根设备下关联有至少一个目标PCIe端设备,包括: 目标分配模块,用于依据PCIe根设备支持的地址位宽与目标PCIe端设备支持的地 址位宽,确定分配给所述目标PCIe端设备的目标地址位宽和目标Bar空间; 兼容配置模块,用于依据分配的目标地址位宽和目标Bar空间进行PCIe兼容配置, 以构建所述PCIe根设备与所述目标PCIe端设备间的目标PCIe链路; 数据包发送模块,用于采用目标PCIe链路,向所述目标PCIe端设备发送数据包。 第三方面,本发明实施例中还提供了一种电子设备,包括: 一个或多个处理器; 存储装置,用于存储一个或多个程序; 所述一个或多个程序被所述一个或多个处理器执行,使得所述一个或多个处理器 实现如本发明实施例中任意所述的PCIe设备的兼容处理方法。 第四方面,本发明实施例中还提供了一种计算机可读存储介质,其上存储有计算 机程序,该程序被处理器执行时实现如本发明实施例中任意所述的PCIe设备的兼容处理方 法。 4 CN 111581139 A 说 明 书 2/10 页 本发明实施例中提供了一种PCIe设备的兼容处理方法,可依据PCIe根设备支持的 地址位宽与目标PCIe端设备支持的地址位宽,向目标PCIe端设备分配合适的目标地址位宽 和目标Bar空间,然后依据目标地址位宽和目标Bar空间进行PCIe兼容配置,以构建目标 PCIe链路。采用本申请方案,在PCIe设备初始化时,可对PCIe总线中的PCIe根设备与目标 PCIe端设备进行兼容处理,以构建兼容的PCIe链路,保证不同地址位宽的RC根设备和EP端 设备之间进行正常通信,以便后续可实现对EP端设备的升级、读取设备寄存器等功能。 上述