技术摘要:

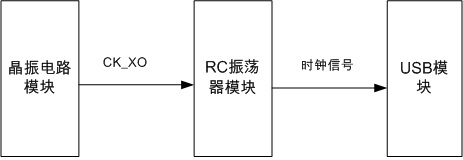

本发明公开了一种USB时钟产生电路,包括晶振电路模块、为USB模块提供时钟信号的RC振荡器模块,RC振荡器模块连接于晶振电路模块并接收晶振电路模块提供的基准时钟;RC振荡器模块包括RCO子电路、同步脉冲发生子电路、计数器子电路、开关控制子电路和时钟合成子电路;RCO 全部

背景技术:

目前,在SOC(System-on-a-Chip,片上系统)中,为数字电路提供时钟通常有两类 做法: 一、用晶体振荡器产生基准时钟,经过内部的PLL(Phase Locked Loop,锁相环)倍频, 产生所需的时钟频率,如图1所示。该方法的优点是:频率精准度高;缺点是:晶振启动较慢, 通常为1ms以上,导致数字电路启动也需要等待较长时间。 二、采用RC振荡器,经过校准处理,得到较为精确的时钟提供给数字电路,如图2所 示。该方法的优点是起振快,电路简单成本低。缺点是:频率精准度较差。对于MCU应用,此方 式通常是可以满足需求的。 而USB full speed(全速USB)需要的时钟频率是12MHz的整数倍,通常是48MHz,被 数字电路用来对输入数据进行采样。为了防止长时间时钟偏移过大造成采样错位,USB的时 钟需要达到正负2500ppm的精度。 如果SOC需要支持USB full speed,采用方法一虽然可行,但会增加成本。又或者 限定晶振的频率,24M或48M,省去额外的锁相环,用简单的二倍频电路产生48 MHz时钟,但 这样又限制了产品的灵活性(且晶振频率越高价格越贵)。采用方法二没有上述缺点,但需 要在工艺/温度偏差下做到频率准度在正负2500ppm以内,需要付出额外的电路设计努力和 电路面积。还有方法三,即在数字域加入额外的处理,以降低对USB时钟精度的要求,但这样 同样会增加成本和设计难度。

技术实现要素:

本发明的主要目的在于提供一种USB时钟产生电路,旨在保证时钟精度的同时、降 低电路成本。 为实现上述目的,本发明提供一种USB时钟产生电路,包括晶振电路模块,所述电 路还包括为USB模块提供时钟信号的RC振荡器模块,所述RC振荡器模块连接于所述晶振电 路模块并接收所述晶振电路模块提供的基准时钟;所述RC振荡器模块包括RCO子电路、同步 脉冲发生子电路、计数器子电路、开关控制子电路和时钟合成子电路;所述RCO子电路输出 第一控制信号;所述同步脉冲发生子电路连接于所述晶振电路模块接收所述基准时钟,并 输出第二控制信号;所述计数器子电路连接于所述RCO子电路和所述同步脉冲发生子电路 并接收所述第一控制信号和所述第二控制信号,所述计数器子电路根据所述第一控制信号 和所述第二控制信号进行计数,并根据计数值输出第三控制信号;所述开关控制子电路接 收所述第二控制信号和所述第三控制信号,以分别控制所述开关控制子电路的接通/关断; 所述时钟合成子电路接收所述第一控制信号和所述第二控制信号,经OR运算后输出所述 USB模块所需的时钟信号。 4 CN 111597133 A 说 明 书 2/6 页 优选地,所述RCO子电路包括第一电流源、第一比较器、第一电容、第一场效应管和 第一反相器; 所述第一电流源为所述RCO子电路提供电流源,所述第一比较器连接于所述第一电流 源、并将所述第一电流源与阈值电压进行比较,所述第一比较器的输出端输出第一控制信 号;所述第一电容的一端连接于所述第一电流源、另一端接地;所述第一场效应管的漏极连 接于所述第一电流源和第一电容的一端、栅极连接于第一反相器的输出端、漏极接地;所述 第一比较器的输出端连接于所述开关控制子电路,所述开关控制子电路还连接于所述第一 反相器的输入端。 优选地,所述开关控制子电路包括第一或非门单元,所述第一或非门单元的输入 端分别接收所述第一控制信号、所述第二控制信号和所述第三控制信号,所述第一或非门 单元的输出端连接于所述第一反相器的输入端。 优选地,所述同步脉冲发生子电路包括第三反相器、延时单元、与非门单元和第四 反相器; 所述第三反相器的输入端连接于所述晶振电路模块并接收所述基准时钟,所述第三反 相器的输出端连接于所述延时单元的输入端; 所述与非门单元的输入端连接于所述延时单元的输出端和所述晶振电路模块,所述与 非门单元的输出端连接于所述第四反相器的输入端,所述第四反相器的输出端输出第二控 制信号。 优选地,所述RCO子电路包括第一电流源、第一比较器、第一电容、第一场效应管、 第一反相器和第二反相器; 所述第一电流源为所述RCO子电路提供电流源,所述第一比较器连接于所述第一电流 源、并将所述第一电流源与阈值电压进行比较,所述第一比较器的输出端经所述第一反相 器和所述第二反相器输出第一控制信号;所述第一电容的一端连接于所述第一电流源、另 一端接地;所述第一场效应管的漏极连接于所述第一电流源和所述第一电容的一端、栅极 连接于第二反相器的输出端、漏极接地;所述第一比较器的输出端连接于所述第一反相器 的输入端,所述第一反相器的输出端连接于所述第二反相器的输入端。 优选地,所述开关控制子电路包括连接于所述同步脉冲发生子电路并接收第二控 制信号的第一开关,还包括连接于所述计数器子电路并接收第三控制信号的第二开关,所 述第一开关连接于所述第二开关,所述第二开关还连接于所述第一电容的一端。 优选地,所述同步脉冲发生子电路包括第二比较器、与非门单元、第四反相器、第 二场效应管和第二电容; 所述第二比较器连接于所述第二电流源、并将所述第二电流源与阈值电压进行比较, 并输出比较结果至所述与非门单元;所述与非门单元的输入端分别连接于所述第二比较器 的输出端和所述晶振电路模块,所述与非门单元输出端连接于第四反相器的输入端;所述 第四反相器的输出端输出第二控制信号; 所述第二电容的一端连接于第二电流源、另一端接地;所述第二场效应管的栅极连接 于所述晶振电路模块、漏极连接于第二电容的一端和所述第二电流源、源极接地。 优选地,所述计数器子电路的CK输入端连接于所述RCO子电路并接收所述第一控 制信号,用以对所述第一控制信号的上升沿进行计数;所述计数器子电路的RST输入端连接 5 CN 111597133 A 说 明 书 3/6 页 于所述同步脉冲发生子电路并接收所述第二控制信号,用以在所述第二控制信号高电平时 对计数值进行清零;所述计数器子电路输出端输出第三控制信号。 优选地,所述时钟合成子电路包括第二或非门单元、第五反相器和二分频子电路; 所述第二或非门单元的第一输入端连接于所述RCO子电路并接收所述第一控制信号,第二 输入端连接于所述同步脉冲发生子电路并接收所述第二控制信号;所述第二或非门单元的 输出端连接于所述第五反相器的输入端,所述第五反相器的输出端连接于所述二分频子电 路,以输出时钟信号。 本发明技术方案通过晶振电路模块提供基准时钟,增加同步脉冲发生子电路、计 数器子电路、开关控制子电路和时钟合成子电路,以使基准时钟对RCO子电路进行同步,即 使在RCO子电路的精度较低的情况,也能保证全速USB时钟的应用需求。 附图说明 图1为现有技术中的时钟产生电路; 图2为现有技术中另一种时钟产生电路; 图3为本发明USB时钟产生电路的原理示意图; 图4为本发明USB时钟产生电路中RC振荡器模块的原理示意图;‘’ 图5为本发明第一实施例中RC振荡器模块的电路结构示意图; 图6为本发明第二实施例中RC振荡器模块的电路结构示意图。 本发明目的的实现、功能特点及优点将结合实施例,参照附图做进一步说明。