技术摘要:

一种二极管结构的制造方法,包含形成第一堆叠在基板上的硅层上。形成相对的多个第一侧壁间隔物,沿着且覆盖第一堆叠的两侧壁。选择性蚀刻硅层至第一预定深度,从而形成第二堆叠,剩余的硅层包含硅底板。形成相对的多个第二侧壁间隔物,沿着且覆盖第二堆叠的两侧壁。选 全部

背景技术:

二极管为一种熟悉的半导体元件,通常使用于电子应用中,例如电源电路或电压 转换器。一般而言,二极管的结构至少包含第一半导体层、第二半导体层以及位于上述二者 之间的其他层。第一半导体层及第二半导体层常掺有三价或五价元素掺质以维持电性,例 如P型或N型掺质。 一般而言,使用沉积法直接形成P型或N型半导体层,然而,在不同沉积层之间会形 成界面,例如P-I-N(第一半导体层-本质硅层-第二半导体层)的界面,此种界面容易引起杂 质原子(离子)偏聚,再者,界面上原子排列混乱,存在着许多空位、位错和键变形等缺陷。因 此,界面上的缺陷将影响二极管的性能。为了解决此问题,此亦将增加二极管的制作过程的 复杂性。 因此,目前需要一种可以在二极管结构中减少两相邻半导体层之间界面上的缺陷 的形成的制造方法。

技术实现要素:

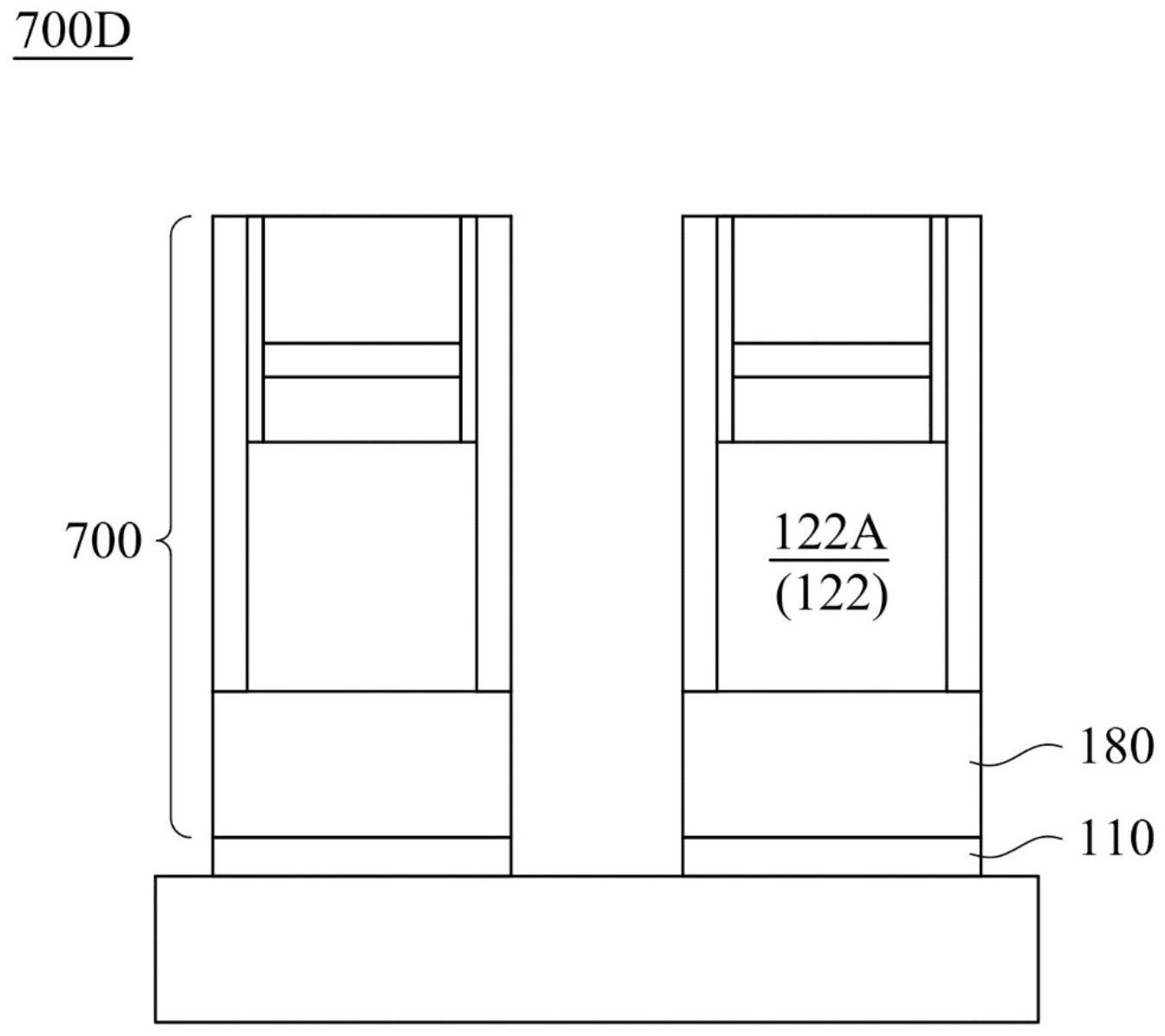

根据本发明的多个实施例,提供一种二极管结构的制造方法包含:形成第一堆叠 在基板上的硅层上,其中第一堆叠自硅层按递升次序包含第一半导体层、上电极层及相变 化材料层;形成相对的多个第一侧壁间隔物,沿着且覆盖第一堆叠的两侧壁,其中相变化材 料层的顶表面曝露出;以第一侧壁间隔物及相变化材料层做为遮罩,选择性蚀刻硅层至第 一预定深度,从而形成第二堆叠,其中剩余的硅层包含硅底板,第二堆叠包含:自硅底板凸 起的第一硅部、以及第一堆叠;形成相对的多个第二侧壁间隔物,沿着且覆盖第二堆叠的两 侧壁,其中顶表面曝露出;以第二侧壁间隔物及相变化材料层做为遮罩,选择性蚀刻硅底 板,从而形成第三堆叠在基板上,其中第三堆叠包含:位于第一硅部下方的第二硅部、以及 第二堆叠;以及以第二侧壁间隔物为罩幕,进行侧向电浆离子植入,以在第二硅部中形成掺 杂区,其中掺杂区与第一半导体层的电性不同。 根据本发明的一些实施例,第一硅部的多个侧壁分别与第一侧壁间隔物的多个侧 壁在垂直方向上对齐。 根据本发明的一些实施例,第二硅部的多个侧壁分别与第二侧壁间隔物的多个侧 壁在垂直方向上对齐。 根据本发明的一些实施例,形成第一堆叠在基板上的硅层上包含:形成母硅层在 基板上;执行离子植入制程于母硅层的顶面,以在母硅层的顶面至深度之间形成第一半导 体层,且余留的母硅层是为硅层;形成上电极层于第一半导体层上;形成相变化材料层于上 电极层上;以及图案化第一半导体层、上电极层及相变化材料层为第一堆叠。 4 CN 111599678 A 说 明 书 2/8 页 根据本发明的一些实施例,所述的制造方法还包含:在形成该第一堆叠之前,先形 成下电极在基板上,以致下电极位于基板与硅层之间。 根据本发明的一些实施例,所述的制造方法还包含:进行侧向电浆离子植入之后, 移除未被第三堆叠覆盖的下电极。 根据本发明的一些实施例,第一侧壁间隔物的顶表面曝露出。 根据本发明的一些实施例,相变化材料层可为包含相变化材料层的单层或复层。 根据本发明的一些实施例,第一半导体层具有剂量介于10E16 atom/cm2至10E20 atom/cm2之间。 根据本发明的一些实施例,掺杂区具有剂量介于10E16 atom/cm2至10E20 atom/ cm2之间。 根据本发明的一些实施例,第一侧壁间隔物及第二侧壁间隔物的厚度各在1nm至 5nm的范围内。 根据本发明的多个实施例,提供一种二极管结构的制造方法包含:形成第一堆叠 在基板上的硅层上,其中第一堆叠自硅层按递升次序包含上电极层及相变化材料层;以相 变化材料层做为遮罩,选择性蚀刻硅层至第一预定深度,其中剩余的硅层包含第一硅底板、 及自第一硅底板凸起的第一硅部;进行离子植入制程,以在第一硅部中形成第一掺杂区;形 成相对的多个第一侧壁间隔物,沿着且覆盖第一堆叠的两侧壁、第一硅部的两侧壁;以第一 侧壁间隔物及相变化材料层做为遮罩,选择性蚀刻第一硅底板至第二预定深度,从而形成 第二堆叠,其中剩余的第一硅底板包含第二硅底板,第二堆叠包含:自第二硅底板凸起的第 二硅部、第一硅部以及第一堆叠;形成相对的多个第二侧壁间隔物,沿着且覆盖第二堆叠的 两侧壁;以第二侧壁间隔物及相变化材料层做为遮罩,选择性蚀刻第二硅底板,从而形成第 三堆叠在基板上,其中第三堆叠包含:位于第二硅部下方的第三硅部、以及第二堆叠;以及 以第二侧壁间隔物为罩幕,进行侧向电浆离子植入,以在第三硅部中形成第二掺杂区,其中 第一掺杂区与第二掺杂区的电性不同。 根据本发明的一些实施例,第二硅部的多个侧壁分别与第一侧壁间隔物的多个侧 壁在垂直方向上对齐。 根据本发明的一些实施例,第三硅部的多个侧壁分别与第二侧壁间隔物的多个侧 壁在垂直方向上对齐。 根据本发明的一些实施例,所述的制造方法还包含:在形成第一堆叠在基板上的 硅层上之前,形成下电极在基板与硅层之间。 根据本发明的一些实施例,所述的制造方法还包含:在形成第一堆叠之前,先形成 下电极在基板上,以致下电极位于基板与硅层之间。 根据本发明的一些实施例,第一侧壁间隔物的顶表面曝露出。 根据本发明的一些实施例,相变化材料层可为包含相变化材料层的单层或复层。 根据本发明的一些实施例,第一掺杂区具有剂量介于10E16 atom/cm2至10E20 atom/cm2之间。 根据本发明的一些实施例,第二掺杂区具有剂量介于10E16 atom/cm2至10E20 atom/cm2之间。 根据本发明的一些实施例,第一侧壁间隔物及第二侧壁间隔物的厚度各在1nm至 5 CN 111599678 A 说 明 书 3/8 页 5nm的范围内。 附图说明 为使本发明的上述和其他目的、特征、优点与实施例能更明显易懂,请详阅以下的 详细叙述并搭配对应的附图。 图1绘示根据本发明一些实施例的二极管结构的制造方法流程图; 图2-图10绘示根据本发明一些实施例的二极管结构的制造方法的各阶段的剖面 图; 图11绘示根据本发明一些实施例的二极管结构的制造方法流程图; 图12-图20绘示根据本发明一些实施例的二极管结构的制造方法的各阶段的剖面 图。 【符号说明】 100,300:基板 110,310:下电极 120:母硅层 120T,322BT:顶面 121:第一半导体层 122,322:硅层 122B:硅底板 122C 322A2:第二硅部 122AS,122CS,220S 320B,322AS,322S2,322S3,340B,900B:侧壁 150,350:上电极层 160,360:相变化材料层 160T,320T:顶表面 180:掺杂区 210,320:第一侧壁间隔物 220,340:第二侧壁间隔物 250,450:侧向电浆离子植入 321:第一掺杂区 322A:第一硅部 322B:第一硅底板 322B2:第二硅底板 322N,322T:顶部 380:第二掺杂区 500,800:第一堆叠 600,900:第二堆叠 700,1000:第三堆叠 700D,1000D:二极管结构 D1:第一预定深度 6 CN 111599678 A 说 明 书 4/8 页 D2:第二预定深度 M100 M200:方法 S102,S104,S106,S108,S110,S112:操作 S202,S204,S206,S208,S210,S212,S214,S216:操作 H1:深度