技术摘要:

本发明公开一种金属氧化物半导体晶体管,其包括基板。基板具有延伸于第一方向的多个沟槽在该基板的顶部。栅极结构线是在该基板上延伸于与该第一方向交叉的第二方向,且跨过该多个沟槽。第一掺杂线是在该基板中位于该栅极结构线的第一侧,跨过该多个沟槽。第二掺杂线是 全部

背景技术:

随着集成电路的功能的提升,其所包含的电路的一部分会操作在相对高电压的范 围,而增加集成电路的整体功能。操作于高电压的金属氧化物半导体晶体管虽然也是由栅 极、源极与漏极所构成,但是结构上是不同,以使例如在高电压的操作下,晶体管开启后通 过通道区域的电流可以增加。 金属氧化物半导体晶体管的栅极用于控制在基底的通道区域的导通状态。当金属 氧化物半导体晶体管例如在高电压的应用时,多晶硅栅极与基板所构成的通道区域的面积 会影响到金属氧化物半导体晶体管的性能。 以高电压晶体管的结构为例,在源极与漏极之间的栅极是的线状结构,用以增加 有效的栅极宽度。栅极在基板上会构成通道区域,使电流流过通道区域。栅极有效宽度实际 上是对应通道有效宽度。于此如一般的定义,源极与漏极之间是长度方向,其产生通道长 度,而栅极有效宽度是指在与通道长度的方向垂直的方向上的延伸长度。栅极有效宽度 (Weff)较大时,晶体管在开启时的电流(Ion)也随着加大。 对于金属氧化物半导体晶体管的结构设计,特别是对于操作在高电压下的晶体 管,其需要考虑如何增加栅极有效宽度,以提升晶体管的操作效能。

技术实现要素:

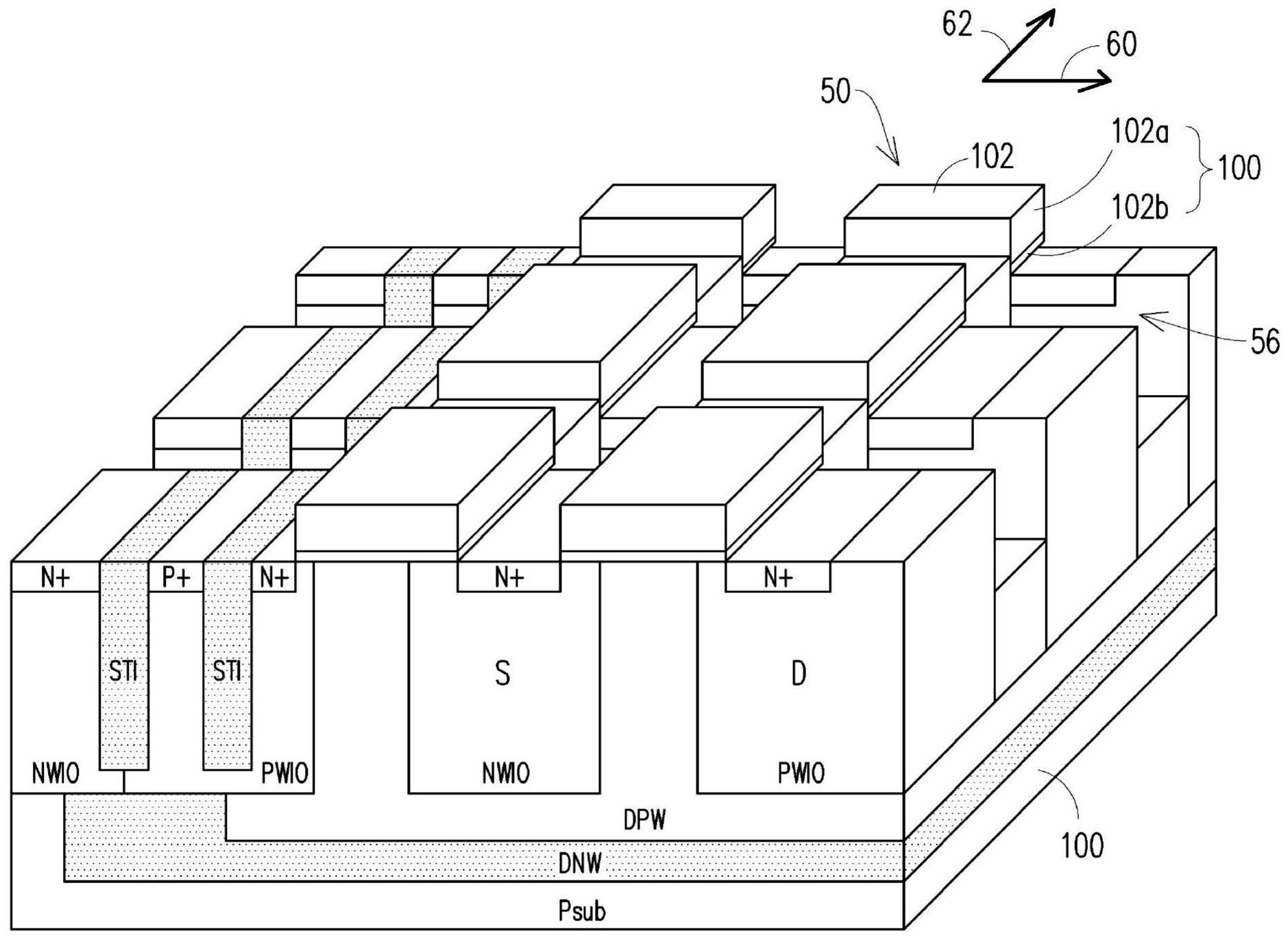

本发明的目的在于提出一种金属氧化物半导体晶体管,其栅极结构在宽度的方向 具有凹陷到基板的结构,以提升栅极的有效宽度。 为达上述目的,本发明提供一种金属氧化物半导体晶体管,包括基板。基板具有延 伸于第一方向的多个沟槽,位于该基板的顶部。栅极结构线是在该基板上延伸于与该第一 方向交叉的第二方向,且跨过该多个沟槽。第一掺杂线是在该基板中位于该栅极结构线的 第一侧,跨过该多个沟槽。第二掺杂线是在该基板中位于该栅极结构线的第二侧,跨过该多 个沟槽。 在一实施例中,对于所述的金属氧化物半导体晶体管,该第一方向垂直于该第二 方向。 在一实施例中,对于所述的金属氧化物半导体晶体管,该多个沟槽的深度是在100 埃到700埃的范围。 在一实施例中,对于所述的金属氧化物半导体晶体管,该多个沟槽的深度是在300 埃到400埃的范围。 在一实施例中,对于所述的金属氧化物半导体晶体管,该多个沟槽的宽度相等于 相邻两个该沟槽之间的距离。 4 CN 111599860 A 说 明 书 2/6 页 在一实施例中,对于所述的金属氧化物半导体晶体管,该多个沟槽的宽度是250nm 或是更多。 在一实施例中,对于所述的金属氧化物半导体晶体管,该基板包含深P型阱区,其 中该第一掺杂线与该第二掺杂线形成在该深P型阱区中。 在一实施例中,对于所述的金属氧化物半导体晶体管,该第一掺杂线是P型且该第 二掺杂线是N型。 在一实施例中,对于所述的金属氧化物半导体晶体管,该栅极结构线包括:栅极绝 缘层,在该基板上;以及栅极线层,在该栅极绝缘层上。 在一实施例中,对于所述的金属氧化物半导体晶体管,该栅极线层是多晶硅层。 本发明也提供一种制造金属氧化物半导体晶体管的方法,其特征在于,包括提供 基板,该基板具有延伸于第一方向的多个沟槽,位于该基板的顶部。在该基板上栅极结构线 形成,延伸于与该第一方向交叉的第二方向,且跨过该多个沟槽。对该基板进行注入,以在 该基板中形成第一掺杂线与第二掺杂线,延伸于与该第一方向交叉的第二方向,且跨过该 多个沟槽。在该基板上形成栅极结构线,延伸于与该第二方向,且跨过该多个沟槽,其中该 第一掺杂线是在该栅极结构线的第一侧且该第二掺杂线是在该栅极结构线的第二侧。 在一实施例中,对于所述的制造金属氧化物半导体晶体管的方法,该第一方向垂 直于该第二方向。 在一实施例中,对于所述的制造金属氧化物半导体晶体管的方法,该多个沟槽的 深度是在100埃到700埃的范围。 在一实施例中,对于所述的制造金属氧化物半导体晶体管的方法,该多个沟槽的 深度是在300埃到400埃的范围。 在一实施例中,对于所述的制造金属氧化物半导体晶体管的方法,该多个沟槽的 宽度相等于相邻两个该沟槽之间的距离。 在一实施例中,对于所述的制造金属氧化物半导体晶体管的方法,该多个沟槽的 宽度是250nm或是更多。 在一实施例中,对于所述的制造金属氧化物半导体晶体管的方法,对该基板进行 注入的该步骤还包括形成深P型阱区在该基板中,该第一掺杂线与该第二掺杂线形成在该 深P型阱区中。 在一实施例中,对于所述的制造金属氧化物半导体晶体管的方法,该第一掺杂线 是P型且该第二掺杂线是N型。 在一实施例中,对于所述的制造金属氧化物半导体晶体管的方法,形成该栅极结 构线的该步骤包括在该基板上形成栅极绝缘层,跨过该多隔沟槽以及在该栅极绝缘层上形 成栅极线层。 在一实施例中,对于所述的制造金属氧化物半导体晶体管的方法,该栅极线层是 多晶硅层。 附图说明 包含附图以便进一步理解本发明,且附图并入本说明书中并构成本说明书的一部 分。附图说明本发明的实施例,并与描述一起用于解释本发明的原理。 5 CN 111599860 A 说 明 书 3/6 页 图1为本发明一实施例,金属氧化物半导体晶体管的三维结构示意图; 图2为本发明一实施例,金属氧化物半导体晶体管的上视结构示意图; 图3为本发明一实施例,金属氧化物半导体晶体管在图1的切割线I-I的剖面结构 示意图; 图4为本发明一实施例,金属氧化物半导体晶体管在图1的切割线II-II的剖面结 构示意图; 图5A~图5O为本发明一实施例,制造金属氧化物半导体晶体管的方法的剖面结构 示意图。 附图标号说明 50:晶体管 52:隔离结构 54:接触区域 56:沟槽 60:第一方向 62:第二方向 100:基板 102:栅极结构线 102a:栅极线层 102b:栅极绝缘层 200:基板 202:隔离结构 204:垫氧化层 206:氮化物层 208:光致抗蚀剂层 210、212、214:开口 216:沟槽 218:垫氧化层 220:栅极绝缘层 222:栅极层 224:栅极线结构