技术摘要:

一种半导体结构及其形成方法,形成方法包括:提供用于形成MOS晶体管的基底,包括第一区域和第二区域,基底包括衬底以及位于衬底上分立的鳍部,第一区域的相邻鳍部和衬底之间围成第一凹槽,第二区域的相邻鳍部和衬底之间围成第二凹槽,第二凹槽的深度小于第一凹槽的深度 全部

背景技术:

在半导体制造中,随着超大规模集成电路的发展趋势,集成电路特征尺寸持续减 小,为了适应更小的特征尺寸,金属-氧化物-半导体场效应晶体管(Metal-Oxide- Semiconductor Field-Effect Transistor,MOSFET)的沟道长度也相应不断缩短。然而,随 着器件沟道长度的缩短,器件源极与漏极间的距离也随之缩短,因此栅极结构对沟道的控 制能力随之变差,栅极电压夹断(pinch off)沟道的难度也越来越大,使得亚阈值漏电 (subthreshold leakage)现象,即所谓的短沟道效应(SCE:short-channel effects)更容 易发生。 因此,为了减小短沟道效应的影响,半导体工艺逐渐开始从平面MOSFET向具有更 高功效的三维立体式的晶体管过渡,如鳍式场效应晶体管(FinFET)。FinFET中,栅极结构至 少可以从两侧对超薄体(鳍部)进行控制,与平面MOSFET相比,栅极结构对沟道的控制能力 更强,能够很好的抑制短沟道效应;且FinFET相对于其他器件,与现有集成电路制造具有更 好的兼容性。

技术实现要素:

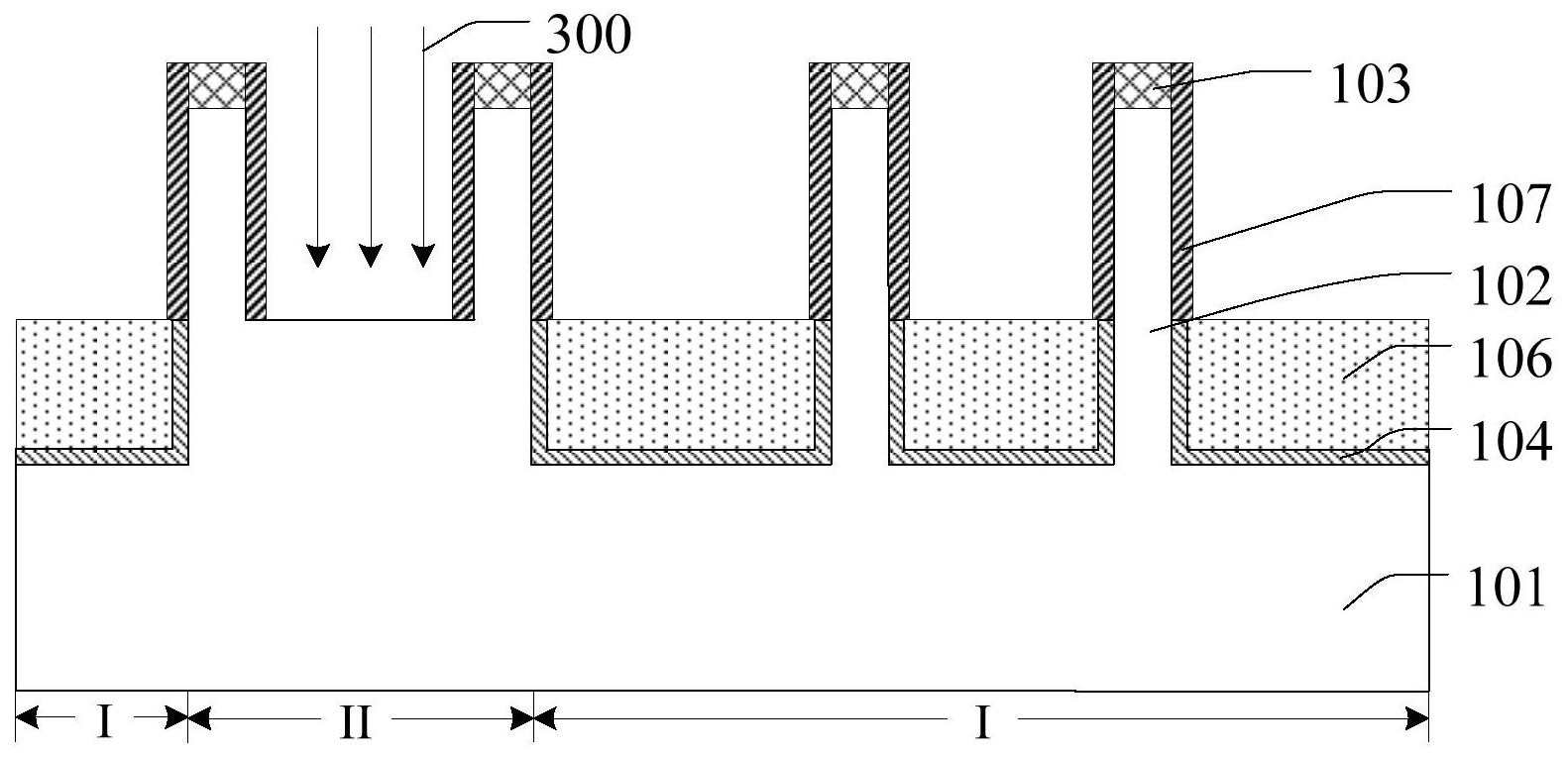

本发明实施例解决的问题是提供一种半导体结构及其形成方法,优化半导体结构 的电学性能。 为解决上述问题,本发明实施例提供一种半导体结构的形成方法,包括:提供用于 形成MOS晶体管的基底,包括第一区域和第二区域,所述基底包括衬底以及位于所述衬底上 分立的鳍部,所述第一区域的相邻鳍部和衬底之间围成第一凹槽,所述第二区域的相邻鳍 部和衬底之间围成第二凹槽,所述第二凹槽的深度小于所述第一凹槽的深度;在所述鳍部 露出的衬底上形成第一隔离层,所述第一隔离层露出所述第二凹槽底部;形成所述第一隔 离层后,对所述第二凹槽底部进行离子掺杂处理,所述掺杂离子类型与MOS晶体管的导电类 型相反;进行所述离子掺杂处理之后,在所述第一隔离层上形成第二隔离层,所述第二隔离 层还位于所述第二凹槽内且覆盖所述鳍部的部分侧壁。 可选的,形成所述第一隔离层后,对所述第二凹槽底部进行离子掺杂处理之前,还 包括:在所述第一隔离层露出的鳍部侧壁上形成侧壁层。 可选的,形成所述侧壁层的步骤包括:形成保形覆盖所述鳍部顶部和侧壁、以及所 述第一隔离层顶部的侧壁材料层;去除位于所述鳍部顶部和第一隔离层顶部的侧壁材料 层,保留鳍部侧壁上的侧壁材料层作为所述侧壁层。 可选的,采用原子层沉积工艺形成所述侧壁材料层。 可选的,采用无掩膜干法刻蚀工艺去除位于所述鳍部顶部和第一隔离层顶部的侧 壁材料层。 4 CN 111554635 A 说 明 书 2/10 页 可选的,所述侧壁层的材料为介电材料。 可选的,所述侧壁层的材料为氮化硅、氮氧化硅、或氧化硅。 可选的,形成所述侧壁层的步骤中,沿垂直于所述鳍部侧壁的方向,所述侧壁层的 厚度为20埃米至50埃米。 可选的,形成所述第二隔离层的步骤包括:在所述鳍部露出的第一隔离层上形成 隔离材料层,所述隔离材料层覆盖所述鳍部顶部且位于所述第二凹槽内;平坦化所述隔离 材料层顶部;平坦化所述隔离材料层顶部后,去除部分厚度的所述隔离材料层,保留剩余隔 离材料层作为所述第二隔离层。 可选的,形成所述第二隔离层的步骤中,所述第二隔离层顶部至第二凹槽底部的 距离为100埃米至300埃米。 可选的,形成所述第一隔离层的步骤中,所述第一隔离层的厚度为300埃米至500 埃米。 可选的,所述基底用于形成NMOS晶体管,所述离子掺杂处理的掺杂离子类型为P 型;或者,所述基底用于形成PMOS晶体管,所述离子掺杂处理的掺杂离子类型为N型。 相应的,本发明实施例还提供一种半导体结构,包括:基底,用于形成MOS晶体管, 包括衬底以及分立于所述衬底上的鳍部,所述基底包括第一区域和第二区域,所述第一区 域的相邻鳍部和衬底之间围成第一凹槽,所述第二区域的相邻鳍部和衬底之间围成第二凹 槽,所述第二凹槽的深度小于所述第一凹槽的深度,所述第二凹槽底部的衬底内具有掺杂 离子,所述掺杂离子的类型与MOS晶体管的导电类型相反;第一隔离层,位于所述鳍部露出 的衬底上,所述第一隔离层露出第二凹槽底部;第二隔离层,位于所述第一隔离层上,所述 第二隔离层还位于第二凹槽内且覆盖所述鳍部的部分侧壁。 可选的,所述半导体结构还包括:侧壁层,位于所述鳍部和第二隔离层之间。 可选的,所述侧壁层的材料为介电材料。 可选的,所述侧壁层的材料为氮化硅、氮氧化硅、或氧化硅。 可选的,沿垂直于所述鳍部侧壁的方向,所述侧壁层的厚度为20埃米至50埃米。 可选的,所述第二隔离层顶部至第一凹槽底部的距离为100埃米至300埃米。 可选的,所述第一隔离层的厚度为300埃米至500埃米。 可选的,所述MOS晶体管为NMOS晶体管,所述掺杂离子的类型为P型;或者,所述MOS 晶体管为PMOS晶体管,所述掺杂的离子类型为N型。 与现有技术相比,本发明实施例的技术方案具有以下优点: 本发明实施例中在所述鳍部露出的衬底上形成第一隔离层,所述第一隔离层露出 所述第二凹槽底部,后续对所述第二凹槽底部进行离子掺杂处理的步骤中,通过所述第一 隔离层,即可实现对所述第一区域衬底的保护作用,从而有利于避免将离子掺杂到第一区 域的衬底内;与形成填充于第一区域相邻鳍部之间并露出第二凹槽底部的掩膜层的方式对 第一区域衬底进行保护的方案相比,本发明实施例中,后续不需进行去除第一隔离层的步 骤,避免进行去除第一区域相邻鳍部之间掩膜层的步骤,这不仅简化了工艺流程,还避免了 出现掩膜层难以被完全去除的问题,从而避免了残留的掩膜层材料对半导体结构的电学性 能产生不良影响;此外,形成所述第一隔离层的步骤不需用到光罩,有利于降低工艺成本。 5 CN 111554635 A 说 明 书 3/10 页 附图说明 图1至图3是一种半导体结构的形成方法中各步骤对应的结构示意图; 图4至图11是本发明半导体结构的形成方法一实施例中各步骤对应的结构示意 图。