技术摘要:

一种查找数据最高有效比特位的电路装置,包括N级数据选择器,用于根据选择信号确定出数据位宽的低位部分是否向后续的电路中进行传输;N级或门,用于对每一部分数据位宽的高位部分进行位或运算。本发明还公开了一种查找数据最高有效比特位的方法,本发明应用在数据最高 全部

背景技术:

在对定点数据进行归一化处理时,需要放大或缩小一定的比例来实现,放大或缩 小通过移位来实现。由于最高有效位的位置在不同数据中是不固定的,因此在确定其具体 位置并不容易。比如,在定义了小数位宽和整数位宽都是8比特的16位定点数据为xxxx_ xxxx_xxxx_xxxx,如以下三个数据(低位移出的比特位忽略): 0001_0011_0100_0011=0000_0001_0011_0100*24--------式1 0000_0111_0101_0010=0000_0001_1101_0100*22--------式2 0000_0000_0001_0010=0000_0001_0010_0000*2-4----------式3 其最高有效位分别是Data[12],Data[10]和Data[4],进行归一化时分别需要右移 的位数为4,2和-4。位于最高有效位后面的逻辑“1”,即较低位的逻辑“1”是不影响数据移位 的位数的,不进行处理计算。 采用时序电路实现如图1所示,以32位的二进制数据为例,则MSB (Mos t Significant Bit)(即b31)最先输入到检测电路,LSB(Least Significant Bit)(即b0)最 后输入,每个时钟移动一位,并有相应的循环加法器cnt进行计数,b31输入到电路和cnt值 为0为同一时钟周期,当遇到第一个逻辑“1”时(即最高有效位)时锁住相应的计数值,该计 数值出现在lock信号有效的下一个周期,将此值记为P,P值即为最高有效位所处二进制数 据中的位置。 当P[4:0]=5’b00000时,则需要S的值来判断是否有M当中是否有“1”存在,即S= 1’b1时,说明最高位1为M[0],若S=1’b0,则说明M=32’h00000000,即M所有的比特位都不 为“1”。 时序电路当中要得出P[4:0]周期数最快为1个,最慢为31个,因此整个电路的工作 效率为31个时钟周期处理一个32比特的数据。以次类推,若要处理64位的数据则需要63个 周期,128位数据则需要127个周期,效率非常低。若记WIDTH(M)为数据M的位宽,Tclk为时钟 周期,数据最高有效位所处位置值的输出周期数为Ncycle,则结果输出所需时间为D0=Tclk* Ncycle=Tclk*(WIDTH(M)-1)-----------------------式4 结果的输出所需要的周期数与位宽成线性关系,效率很低。 采用组合逻辑进行有效位位置检测的电路结构如图2所示,以M[31]为最高优先 级。当M[31]=“1”时,输出P=5’d31,当M[31]=“0”而M[30]=“1”,输出P=5’d30,依次类推 到M[1]。当P=5’b0时,则需要S的值来判断是否有M当中是否有“1”存在,即S=1’b1时,说明 最高位1为M[0],若S=1’b0,则说明M=32’h00000000,即所有比特位都不为“1”。 P值的输出需要数据通过逐级传输,通过的数据选择器共有31级,假定单级的延时 为d1,因此最长路径的延时为 3 CN 111597770 A 说 明 书 2/5 页 D1=d1*31----------------------式5 因此当数据的位宽为WIDTH(M)位时,则最长延时为 D1=d1*(WIDTH(M)-1)----------------------式6 该组合逻辑电路的延时与数据的位宽成线性关系,数据位宽加倍时将会导致电路 工作的频率减半,严重影响电路的工作效率。 在图1所示电路对应的式4中,可以得知延时D0=Tclk*WIDTH(M),电路的处理需要 经过若干个时钟周期,结果的输出所需要的周期数个数与位宽成线性关系,因而电路延时 非常严重,对于需要在单个周期内得出数据结果是不可能的。 在图2的组合逻辑电路中,延时D1=d1*(WIDTH(M)-1),其关键路径的延时和位宽 之间也成线性关系,对于16位的数据则需要15个选择器的级联传输,而32位数据更需要多 达31个选择器的级联。在不使用流水线技术的前提下,其组合逻辑长延时路径的特点将导 致整个电路的工作频率大幅度降低。 对于采用图1和图2方式进行处理的电路,都面临着长延时的问题,导致电路的工 作效率低下,尤其是第二种组合逻辑方式实现的电路,虽然缩短到了一个时钟周期内完成 输出,但由于关键路径长,有很长的传输延时,会极大影响时钟的频率,影响整个电路的工 作效率。

技术实现要素:

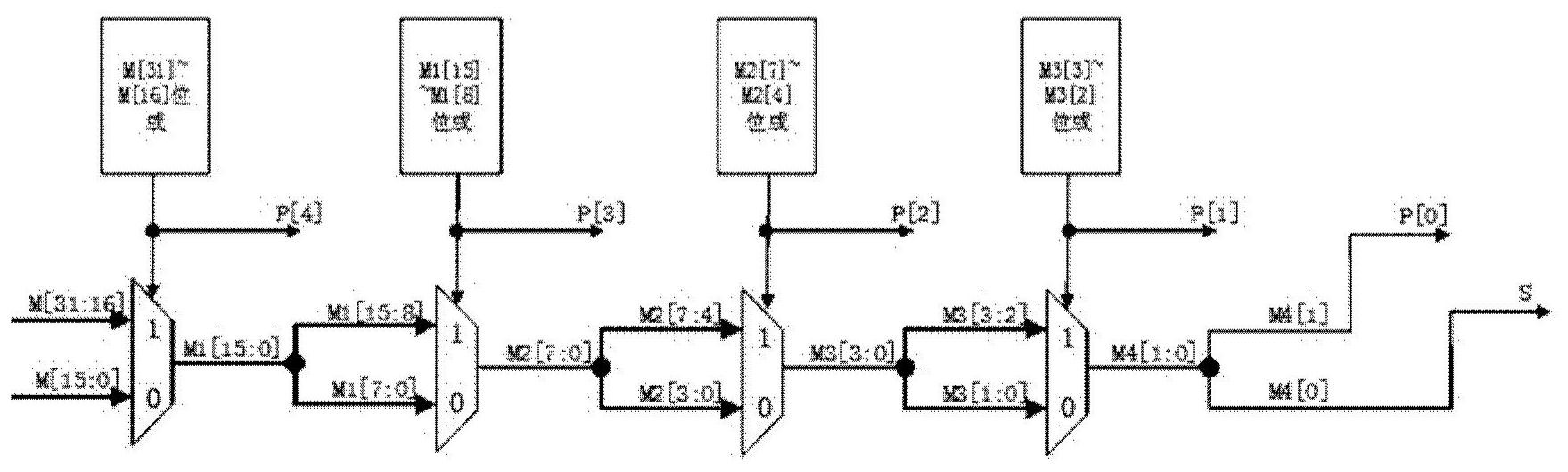

有鉴于此,本发明的主要目的在于提供一种快速查找数据最高有效比特位的电路 装置及查找方法,以期至少部分地解决上述技术问题中的至少之一。 为了实现上述目的,作为本发明的一方面,提供了一种快速查找数据最高有效比 特位的电路装置,包括: N级数据选择器,用于根据选择信号确定出数据位宽的低位部分是否向后续的电 路中进行传输; N级或门,用于对每一部分数据位宽的高位部分进行位或运算。 其中,所述电路的关键路径的时延为: D2=(d1 d2)*N; 其中,d1为数据选择器的延时,d2为或门的延时,N为选择器的级数。 作为本发明的另一方面,还提供了一种快速查找数据最高有效比特位的查找方 法,包括以下步骤: 将数据M分成两部分,若M的位宽不是2的幂次方,则高位补齐使其位宽扩展为2的 幂次方。以M位宽为32位为例,则高位部分为M[31:16],低位部分为M[15:0],高位部分经过 位或运算后生成信号P[4],P[4]作为M[31:16]和M[15:0]的选择信号; 当M[31:16]中含有“1”时,P[4]的值为“1”,则M1的值为M[31:16],此时最高有效位 就在M[31:16]之间,此时M[15:0]的值将不再传输到后续电路中进行处理;当M[31:16]中不 含“1”时,P[4]的值为“0”,则M1的值为M[15:0]; 当M1[15:8]中含有“1”时,P[3]的值为“1”,则M2的值为M1[15:8],此时最高有效位 就在M1[15:8]之间,此时M1[7:0]的值将不再传输到后续电路中进行处理;当M1[15:8]中不 含“1”时,P[3]的值为“0”,则M2的值为M1[7:0]; 4 CN 111597770 A 说 明 书 3/5 页 当M2[7:4]中含有“1”时,P[2]的值为“1”,则M3的值为M2[7:4],此时最高有效位就 在M2[7:4]之间,此时M2[3:0]的值将不再传输到后续电路中进行处理;当M2[7:4]中不含 “1”时,P[2]的值为“0”,则M3的值为M2[3:0]; 当M3[3:2]中含有“1”时,P[1]的值为“1”,则M4的值为M3[3:2],此时最高有效位就 在M3[3:2]之间,此时M3[1:0]的值将不再传输到后续电路中进行处理;当M3[3:2]中不含 “1”时,P[1]的值为“0”,则M4的值为M3[1:0]; P[0]的值为M4[1],S值为M4[0]; 在上述过程中,P[4:0]的值即为最高位1出现的位置,即P[4:0]的值为W,则表示最 高有效位为M[W]。 其中,所述查找方法对于数据位宽不等于2的幂次方的情况,只需要将其高位补齐 到最接近的2的幂次方数值即可适用。 其中,当所述P[4:0]=5’b00000时,则需要S的值来判断是否有M当中是否有1存 在,即S=I’b1时,说明最高位1为M[0],若S=I’b0,则说明M=32’h00000000,所有比特位都 为0。 基于上述技术方案可知,本发明的快速查找数据最高有效比特位的电路装置及查 找方法相对于现有技术至少具有如下有益效果中的一部分: 本发明应用在数据最高有效位检测时,电路结构简单,复杂度低,使用的逻辑门电 路较少,能有效减小电路在芯片实现时占用的面积,降低生产成本;本发明可大幅度减小信 号传输的延时,加快电路的时钟频率,提高系统的工作效率。将数据从中间分割进行检测, 此二分法的检测思路可以指数级提高检测的效率,本应用于类似的检测电路当中。 附图说明 图1为现有技术中的利用时序逻辑电路实现查找数据最高有效比特位的电路示意 图; 图2为现有技术中的利用组合逻辑进行有效位位置检测的电路结构示意图; 图3为本发明实施例的电路装置结构示意图。