技术摘要:

本发明提供一种基于复合介质栅结构的成像阵列及其曝光、读取方法。成像阵列包括具有复合介质栅结构的像素单元,每个像素单元的源极和漏极对称,若干数目的单元相互串联构成一行,同一行的相邻单元之间共用漏极或源极,若干行单元的漏极或源极再分别通过N型注入区与其它 全部

背景技术:

图像传感器在当今社会应用非常广泛,如移动手机、数码相机、各种摄像机以及国 防探测领域。当前发展的主要成像探测器是CCD和CMOS-APS两种类型,CCD基本结构是一列 列MOS电容串联,通过电容上面电压脉冲时序控制半导体表面势阱产生和变化,进而实现光 生电荷信号的存储和转移读出;CMOS-APS每个像素采用二极管和多个晶体管组成,读取曝 光前后的变化情况得到光信号。CMOS-APS由于某些优点近年来逐渐成为市场的主导,CCD生 产对工艺要求极高,成品率和成本不够理想。目前CCD与CMOS都力图进一步缩小像素尺寸提 高分辨率,CCD因为受到边缘电场等效应使得像素尺寸很难进一步缩小。而CMOS-APS每个像 素由多个晶体管与一个感光二极管构成,使得每个像素的感光区域只占据像素本身很小的 表面积,灵敏度和分辨率相对较小。另外CMOS-APS每个像素包含多个晶体管来完成引址选 通等操作(一般的像素单元包含三个晶体管),这决定了其像素尺寸缩小受到很大的限制。 为了获得具有简单结构、成熟工艺、更高分辨率的成像器件,现有专利 US6784933B1提出采用一个非挥发浮栅存储晶体管与两个选择晶体管作为像素单元的结 构,该结构不仅结构简单而且可以与标准工艺兼容,但这种结构的一个像素中至少包含了 三个晶体管。为了大程度地缩小像素尺寸,专利WO2010094233提出采用一个浮栅晶体管作 为像素单元的结构,以有效提高成像密度,进而在专利CN103165628A中提出了该像素单元 结构的一种可靠的曝光成像方法。为了实现阵列器件的读出,CMOS-APS通常采用X-Y交叉引 址,而这种阵列架构需要的引线较多,像素排列不够紧凑,在专利US6784933B1中,浮栅晶体 管像素采用了NOR架构,每相邻像素之间需要一个电极引线,同样增加了像素尺寸。

技术实现要素:

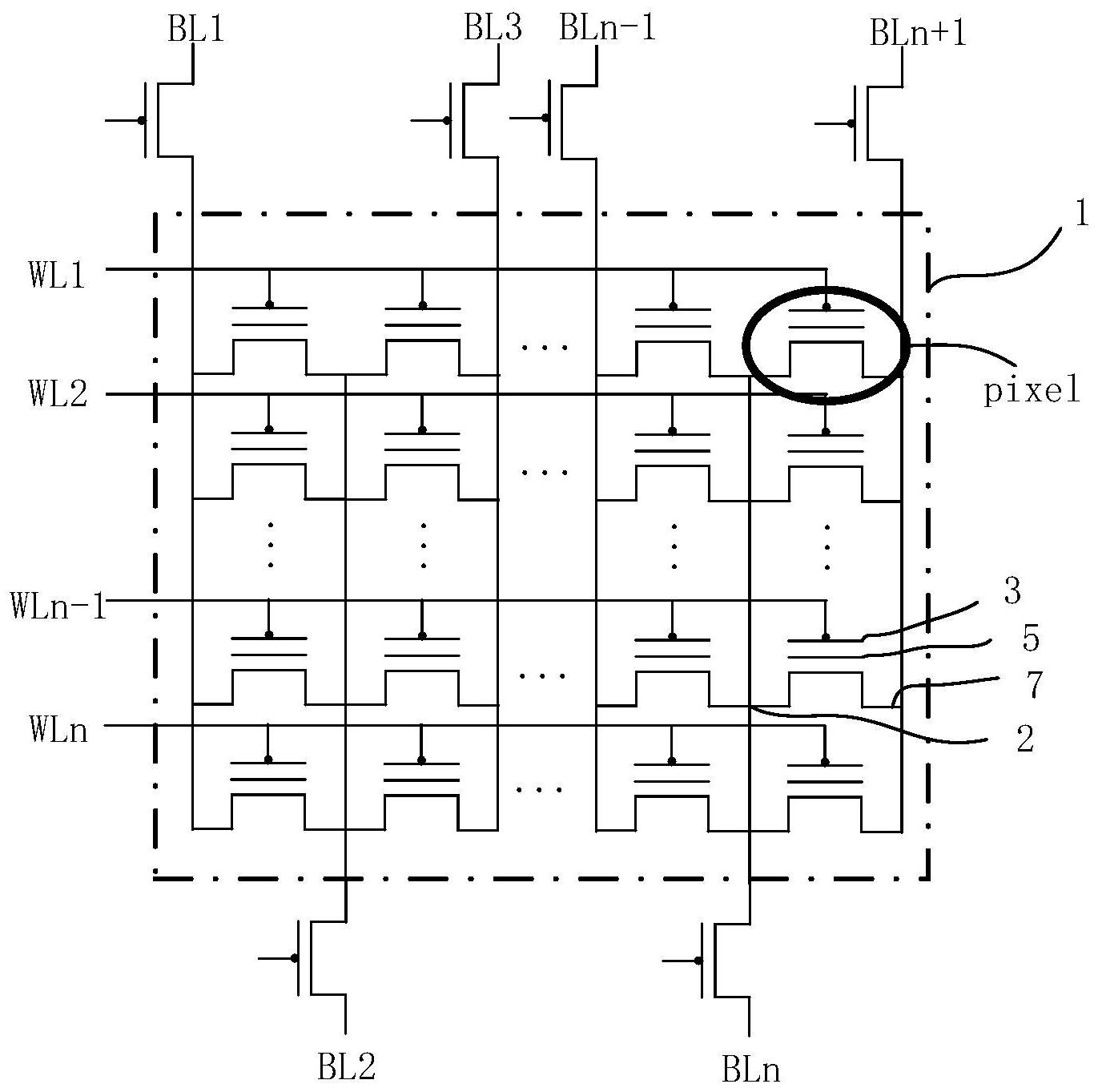

本发明的目的是:基于复合介质栅结构的像素单元,提出一种Virtual Ground (VG)型结构的成像阵列,可以有效地进一步减小像素周期尺寸,提高成像分辨率。本发明的 另一个目的是提供该成像阵列的曝光和读取方法。 本发明成像阵列采用的技术方案是: 基于复合介质栅结构的成像阵列,由多个像素单元组成,像素单元采用复合介质 栅结构,每个像素单元的源极和漏极对称设置,若干数目的像素单元相互串联构成一行,同 一行的相邻像素单元之间共用漏极或源极,若干行像素单元的漏极或源极再分别通过N型 注入区与其它行对应位置的漏极或源极纵向连接构成若干列;在同一列中,将间隔若干行 的N型注入区使用欧姆接触连接到一列金属层位线,使得同一列的像素单元相互并联;在一 列金属层位线的一端设有选择开关晶体管,奇数列和偶数列的开关晶体管位于不同端;每 一行像素单元的控制栅极横向延伸连接为一个整体,并且在同一行中,将间隔若干列的像 3 CN 111554700 A 说 明 书 2/4 页 素单元的控制栅极使用欧姆接触连接到一行金属层字线。 进一步地,所述成像阵列的衬底为一个共用的通过注入形成的p型衬底。 进一步地,同一列的像素单元相互并联所隔的行数为8~64行。 进一步地,在衬底加一负偏压脉冲Vb;在曝光过程中所有选择开关晶体管栅接电 压Von,保证开启;选择开关晶体管不与阵列相连的另一端加一正向电压脉冲Vp;控制栅极 加零正向偏压脉冲Vg。 本发明基于复合介质栅结构的成像阵列的曝光方法,具体为:在衬底加一负偏压 脉冲Vb;在曝光过程中奇数列或偶数列所连的选择开关晶体管栅接电压Von,保证开启;偶 数列或奇数列所连的选择开关晶体管栅接电压Voff,保证关断;奇数列或偶数列的选择开 关晶体管不与阵列相连的另一端加一正向电压脉冲Vp;控制栅极加零正向偏压脉冲Vg。 本发明另一种基于复合介质栅结构的成像阵列的读取方法,具体为:将衬底接地, 要读取的像素单元所在行的字线上加正偏压Vgr;将与要读取的像素单元直接相连接的两 条位线上的两个选择管的栅极加正压Von打开,并将两个选择管不与阵列相连的两个端一 个接地一个加一正电压Vd;其余所有选择管栅加电压Voff关断;读取所选择像素单元相连 的位线中的电流大小,通过电流大小来确定光信号的大小。 本发明的有益效果是: (1)像素单元采用复合介质栅结构,一个晶体管作为一个像素结构非常简单,有利 于提高分辨率。 (2)根据像素结构和成像特点,使横向相邻像素共用一个源区或漏区,源区或漏区 通过n 注入区纵向相连,每隔若干(8~64)行将n 注入区通过金属接触连接到同一层金属 以保证n 区的等电位,从而实现像素单元的并联,不需要每个像素单元都有源极或漏极的 金属接触;根据阵列版图结构,非沟道非n 的区域上方没有控制栅,不存在像素间导通串扰 的问题,因而不需要STI等方式进行像素间隔离。 (3)本发明在没有改变像素单元结构的情况下,能有效地实现像素的紧密排列,可 以很大程度的提高成像阵列的像素密度,提高分辨率。 (4)本发明提供了适用于该成像阵列的一种曝光方法,能够通过调节电压控制成 像阵列的全局曝光成像,具有无暗电流干扰、成像速度快的特点。 (5)本发明提供了适用于该成像阵列的一种读取方法,通过控制所有像素单元在 读取时有同样大小的串联电阻,有效避免了阵列的不同位置的像素所串联的金属线电阻不 同所带来的固定图形噪声。 附图说明 图1为本发明实施例的复合介质栅光敏探测器结构示意图; 图2为本发明实施例的复合介质栅光敏探测器电路示意图; 图3为本发明基于复合介质栅结构像素单元的成像阵列原理图; 图4为本发明基于复合介质栅结构像素单元的成像阵列版图; 图5为本发明实施例中成像阵列曝光示意图; 图6为本发明实施例中成像阵列读取示意图。 4 CN 111554700 A 说 明 书 3/4 页