技术摘要:

本发明公开了一种基于动态可重配技术的可扩展多端口块状存储单元,涉及可编程逻辑器件领域,该可扩展多端口块状存储单元通过特殊的物理布局和设计,其工作模式可以基于动态可重配技术在多端口模式和普通模式两者之间动态切换,当出现大量的并行操作时,可以将其切换为 全部

背景技术:

可编程逻辑器件具有开发周期短、成本低、风险小、集成度高、灵活性大、便于电子 系统维护和升级等优点,因此受到了广大终端产品用户的青睐,成为了集成电路芯片的主 流,且被广泛应用在各种领域如通信、控制、视频、信息处理、电子、互联网、汽车以及航空航 天等。 可编程逻辑器件主要包含控制系统、可编程逻辑单元、数字信号处理DSP、存储单 元块状SRAM以及一些高速接口、时钟模块和IP核等。FPGA是一种灵活通用性的可编程逻辑 器件,随着FPGA的发展,CPU、AI等单元也集成入FPGA,对于系统运算性能需求越来越明确, 大量的并行操作出现在FPGA逻辑中,因此对多端口块状SRAM的需求增多。多端口块状SRAM 相同地址宽度面积较普通单端或双端口要多,固化集成专用多端口块状SRAM会使得FPGA被 多端口块状SRAM消耗大量面积,这种方法复用率低、低功耗成效差的特点与可编程逻辑器 件的灵活性相悖,由此可见,如何兼顾性能和面积对于可编程逻辑器件来说是一个巨大的 挑战。

技术实现要素:

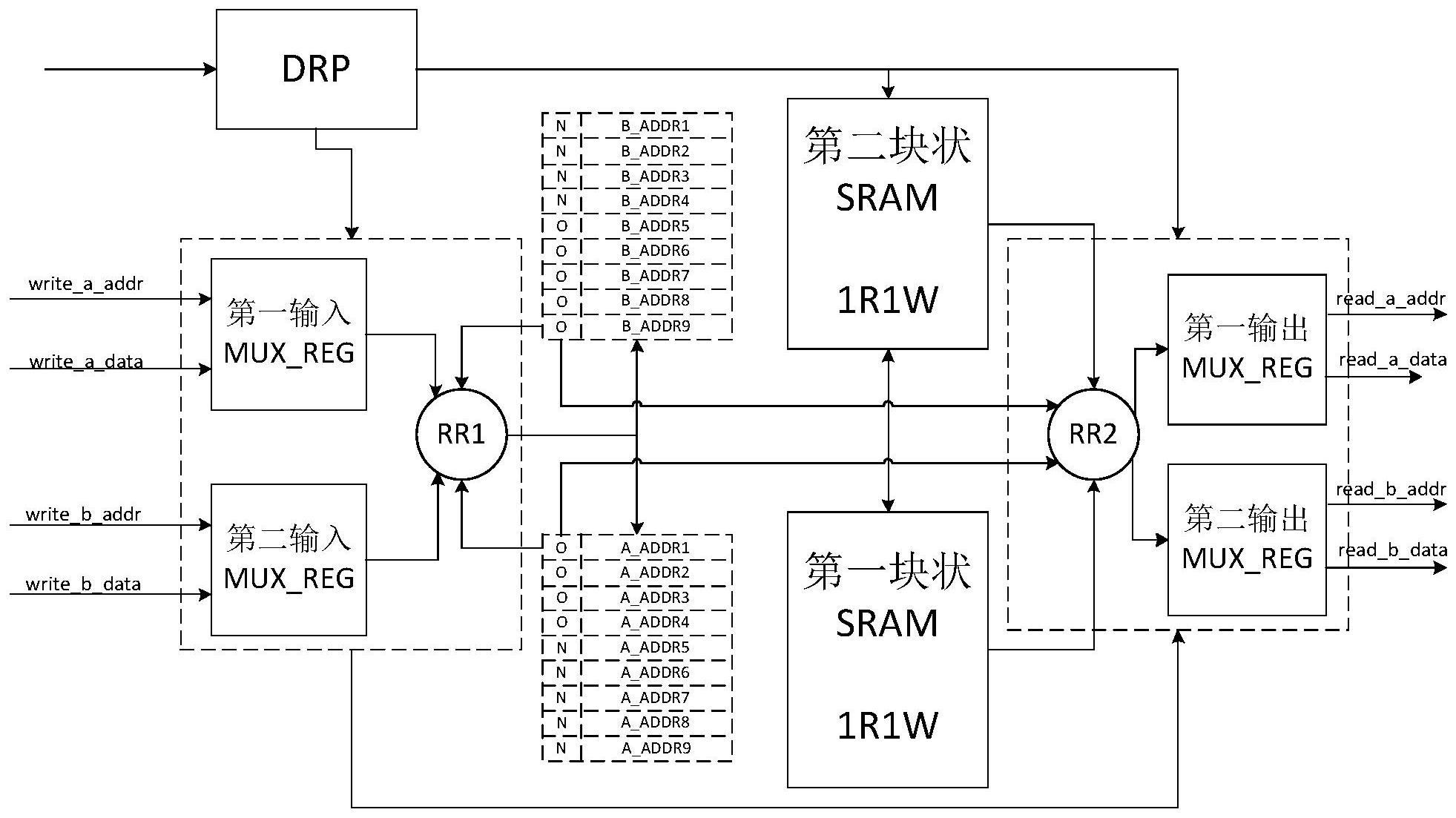

本发明人针对上述问题及技术需求,提出了一种基于动态可重配技术的可扩展多 端口块状存储单元,包括动态重配置接口、第一块状SRAM、第二块状SRAM、读控制模块和写 控制模块,两块SRAM完全相同且端口均为1R1W,动态重配置接口的输入端获取配置参数、输 出端连接读控制模块、写控制模块、第一块状SRAM和第二块状SRAM,动态重配置接口根据获 取到的配置参数配置读控制模块、写控制模块、第一块状SRAM和第二块状SRAM的配置位,使 得可扩展多端口块状存储单元在多端口工作模式和普通工作模式之间动态切换; 当可扩展多端口块状存储单元处于多端口工作模式时,第一块状SRAM和第二块状 SRAM在内部的地址控制模块的控制下并行工作,第一块状SRAM和第二块状SRAM占用相同的 地址,可扩展多端口块状存储单元的有效地址宽度为第一块状SRAM的有效地址宽度;写控 制模块通过两个写数据端口获取写数据并写入其中一个块状SRMA中、读控制模块从其中一 个块状SRAM中获取读数据并通过一个读数据端口输出,或者,写控制模块通过一个写数据 端口获取写数据并写入其中一个块状SRMA中、读控制模块从其中一个块状SRAM中获取读数 据并通过两个读数据端口输出,或者,写控制模块通过两个写数据端口获取写数据并写入 其中一个块状SRMA中、读控制模块从其中一个块状SRAM中获取读数据并通过两个读数据端 口输出; 当可扩展多端口块状存储单元处于普通工作模式时,第一块状SRAM和第二块状 SRAM在内部的地址控制模块的控制下串行工作,第一块状SRAM占用低位地址,第二块状 4 CN 111599391 A 说 明 书 2/5 页 SRAM占用高位地址,可扩展多端口块状存储单元的有效地址宽度为第一块状SRAM的有效地 址宽度与第二块状SRAM的有效地址宽度之和;读控制模块和写控制模块均处于旁路状态, 写数据通过块状SRAM的写端口写入、块状SRAM的数据通过读端口输出。 其进一步的技术方案为,两个块状SRAM内部的地址控制模块包括地址指示标志电 路; 当可扩展多端口块状存储单元处于多端口工作模式时,地址指示标志电路指示各 个地址的指示标志位的状态为新状态或旧状态,且两个块状SRAM中对于同一个地址的指示 标志位的状态始终相反;写控制模块写入写数据后,地址指示标志电路更新两个块状SRAM 中的指示标志位的状态;读控制模块根据两个块状SRAM中的指示标志位的状态获取读数 据; 当可扩展多端口块状存储单元处于普通工作模式时,两个块状SRAM内部的地址指 示标志电路均处于旁路状态。 其进一步的技术方案为,写控制模块包括第一输入MUX_REG、第二输入MUX_REG和 输入选择调度器,两个输入MUX_REG分别连接两个写数据端口,两个输入MUX_REG内部分别 包括写寄存器,两个输入MUX_REG根据输入选择调度器选择控制写入获取到的写数据; 读控制模块包括第一输出MUX_REG、第二输出MUX_REG和输出选择调度器,两个输 出MUX_REG分别连接两个读数据端口,两个输出MUX_REG内部分别包括读寄存器,两个输出 MUX_REG根据输出选择调度器选择控制获取读数据。 其进一步的技术方案为,两个输入MUX_REG通过输入选择调度器查询处于空闲状 态的块状SRAM并写入获取到的写数据,地址指示标志电路将写入数据的的块状SRAM的相应 地址的指示标志位的状态置为新状态、将另一个块状SRAM的同一地址的指示标志位的状态 置为旧状态; 两个输出MUX_REG通过输出选择调度器查询相应地址的地址标志位的状态为新状 态的块状SRAM并获取读数据输出。 其进一步的技术方案为,当两个输入MUX_REG同时写同一个地址时,归一化成一次 写操作;当两个输出MUX_REG同时读同一个地址时,从地址标志位的状态为新状态的块状 SRAM中读取并分别寄存两个输出MUX_REG输出。 其进一步的技术方案为,每个输入MUX_REG利用写寄存器对获取到的写数据寄存 一拍后选择控制写入其中一个块状SRAM中;每个输出MUX_REG利用读寄存器对获取到的读 数据寄存一拍后输出。 其进一步的技术方案为,当两个输出MUX_REG同时从同一个块状SRAM中获取读数 据时,缓存两次读操作,第一输出MUX_REG读操作第一个周期数据寄存一拍后输出、第二输 出MUX_REG读操作第二个周期数据直接输出。 其进一步的技术方案为,当出现读写同地址同周期的情况时,可扩展多端口块状 存储单元支持写穿透模式,输入MUX_REG将获取到的写数据直接传输输出MUX_REG输出,或 者,输入MUX_REG利用写寄存器对获取到的写数据寄存一拍后传输到输出MUX_REG输出。 其进一步的技术方案为,当可扩展多端口块状存储单元从普通工作模式切换至多 端口工作模式时,可扩展多端口块状存储单元保留其中一个块状SRAM中的数据,并将保留 数据的块状SRAM中所有地址的指示标志位都置为新状态,将另一个块状SRAM中所有地址的 5 CN 111599391 A 说 明 书 3/5 页 指示标志位都置为旧状态。 本发明的有益技术效果是: 本申请公开了一种基于动态可重配技术的可扩展多端口块状存储单元,该块状存 储单元通过特殊的物理布局和设计,其工作模式可以在多端口模式和普通模式两者之间动 态切换,当出现大量的并行操作时,可以将其切换为多端口模式,两个块状SRAM并行工作, 通过并行链表和查找表的管理,可以满足多线程并行操作的需求,提升FPGA在网络和AI应 用时系统性能;当没有特殊需求时可以工作在普通工作模式下,两个块状SRAM串行工作配 置成普通的SRAM复用给基本逻辑单元。通过两个块状SRAM可以实现两种工作模式的切换, 复用率高,可以达到性能和资源的平衡,适用于多种使用场景,灵活性高、通用性好、读写端 口选择性高,灵活便利适应各规模的FPGA。 附图说明 图1是本申请的可扩展多端口块状存储单元的逻辑结构示意图。 图2是本申请的可扩展多端口块状存储单元的端口扩展示意图。 图3是本申请的块状存储单元两种工作模式下的有效地址宽度示意图。