技术摘要:

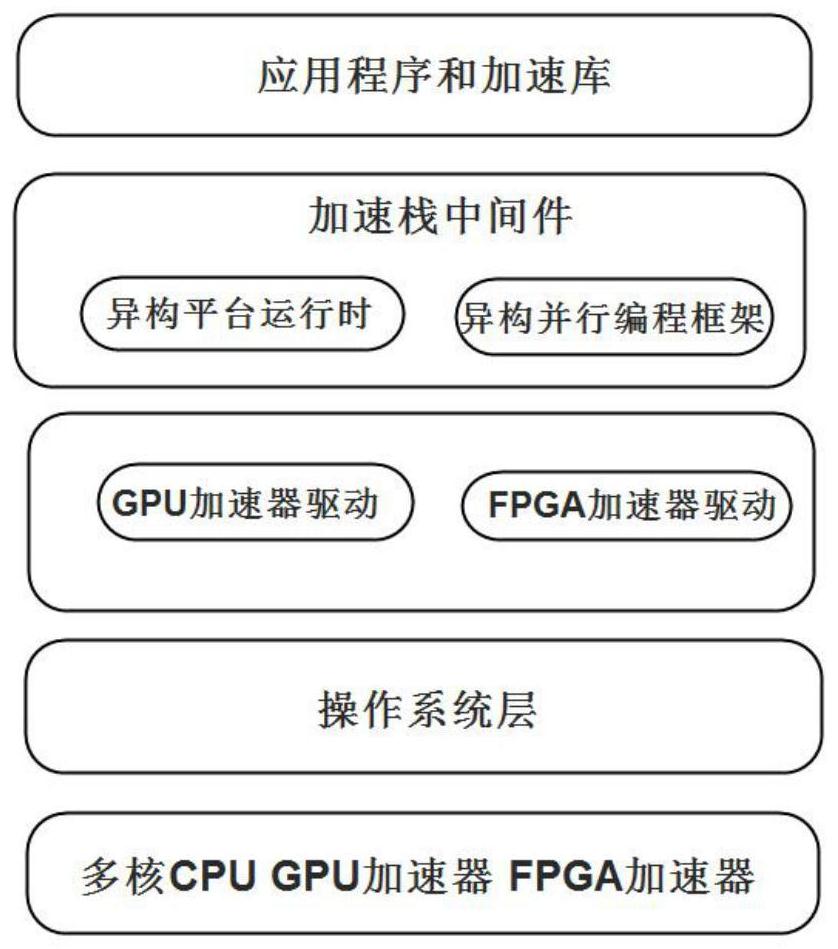

本发明涉及一种国产化异构计算加速平台,其技术特点是:包括加速器硬件平台、操作系统层、GPU加速器驱动层、FPGA加速器驱动层、异构加速栈中间件、应用程序和加速库;加速器硬件平台负责计算存储资源分配和调度;GPU加速器驱动层和FPGA加速器驱动层提供底层硬件内部资 全部

背景技术:

随着智能化、信息化的快速发展,舰艇作战指挥系统、综合导航、云计算中心、密码 系统等装备对计算性能提出了更高要求。目前,部署在舰艇中的计算中心仍采用CPU集群并 行计算架构,其处理器性能和功耗不断逼近物理极限,其性能已经无法满足人工智能、大数 据等应用场景需求,因此需要开拓新的计算架构突破性能瓶颈。 随着“中兴事件”带来的冲击使得国产化自主可控成为舰艇装备发展的必经之路。 具有我国自主知识产权的CPU、GPU以及FPGA芯片近年来才逐渐浮出水面,国产化异构计算 平台的研究仍处于起步阶段。如何有效提高国产CPU平台通用计算能力,满足武器装备智能 化需求是目前迫切需要解决的问题。

技术实现要素:

本发明的目的在于克服现有技术的不足,提出一种设计合理、处理速度快且性能 稳定可靠的国产化异构计算加速平台。 本发明解决其技术问题是采取以下技术方案实现的: 一种国产化异构计算加速平台,包括加速器硬件平台、操作系统层、GPU加速器驱 动层、FPGA加速器驱动层、异构加速栈中间件、应用程序和加速库;所述加速器硬件平台负 责计算存储资源分配和调度;所述GPU加速器驱动层和FPGA加速器驱动层提供底层硬件内 部资源管理接口,供异构平台中间件调用;所述加速栈中间件将异构系统计算和存储资源 映射到操作系统用户空间,为顶层应用程序提供标准化的调用接口;所述加速库提供基本 运算并行化以及底层优化,应用程序执行时由主机提交计算内核和执行指令,在设备上的 计算单元中执行计算。 所述加速器硬件平台包括主机端CPU、GPU加速器和FPGA加速器,所述主机端CPU与 GPU加速器、FPGA加速器通过PCIe总线相连接实现高速通信功能。 所述主机端包括多核CPU和系统存储器,多核CPU内置高速缓存和异构体系结构存 储器控制器;所述GPU加速器包括PCIe控制器、存储器、线程调度引擎、计算单元、视频加速 器、编解码器和L2缓存;所述FPGA加速器包括PCIe控制器、ARM内核、并行逻辑计算单元、高 速互联总线控制器、DDR存储器。 所述主机端CPU采用飞腾CPU芯片,适配国产银河麒麟操作系统;所述GPU加速器采 用景嘉微电子JM7200芯片;所述FPGA加速器采用复旦微电子JMF7K325T芯片。 所述异构加速栈中间件包括异构平台运行时和异构并行编程框架;所述异构平台 运行时是建立在硬件平台驱动层之上的一组底层API,将应用程序运行过程中的计算内核 动态编译成底层硬件语言,再将指令队列和内核发送到设备中运行;所述异构并行编程框 架是一种跨平台的并行编程接口,具备异构资源调度管理、内核生成与执行、内存共享传输 3 CN 111611198 A 说 明 书 2/3 页 功能。 本发明的优点和积极效果是: 本发明使用国产化的CPU、GPU、FPGA以及操作系统搭建基础软硬件平台,通过专用 加速器,以异构计算的方式提升计算性能,构建异构众核加速栈和异构并行计算框架,隐藏 异构系统平台之间的差异;同时,实现异构加速软硬件平台的国产化替代,为核心技术的自 主可控以及智能化技术应用于综合导航系统提供技术支撑。 附图说明 图1是本发明的体系架构图; 图2是本发明的加速栈硬件平台架构图; 图3是本发明的CPU GPU异构平台执行模型; 图4是本发明的CPU FPGA异构平台执行模型。