技术摘要:

本发明公开了快闪存储器的非易失性计算方法,存储器内乘法与累加电路包括存储阵列,例如或非(NOR)快闪阵列,以储存权重Wi,n。行译码器耦接到一组字线,并且被配置为施加字线电压以选择此组中的字线。位线偏压电路产生各个位线的位线偏压电压,作为相应输入上的输入数 全部

背景技术:

在神经形态计算系统中,机器学习系统及用于基于线性代数的某些类型的计算电 路中,乘法与累加或乘积和函数可以是重要的组成部分。这些函数可表达如下: 在此算式中,每个乘积项目是可变输入Xi和权重Wi的乘积。权重Wi可以在此些项目 之间变化,例如对应于可变输入Xi的系数。 乘积和函数可以实现为使用交叉点阵列架构的电路操作,其中阵列单元的电性特 性实现此功能。由于计算中使用的存储器位置之间的数据流复杂性,可能涉及大张量 (tensor)的输入变数的和大量权重,因此出现了与这种类型的大量计算相关联的一个问 题。 一种期望在于提供适于在存储器内实现乘积和操作的结构,以减少所需的数据移 动操作的数量。

技术实现要素:

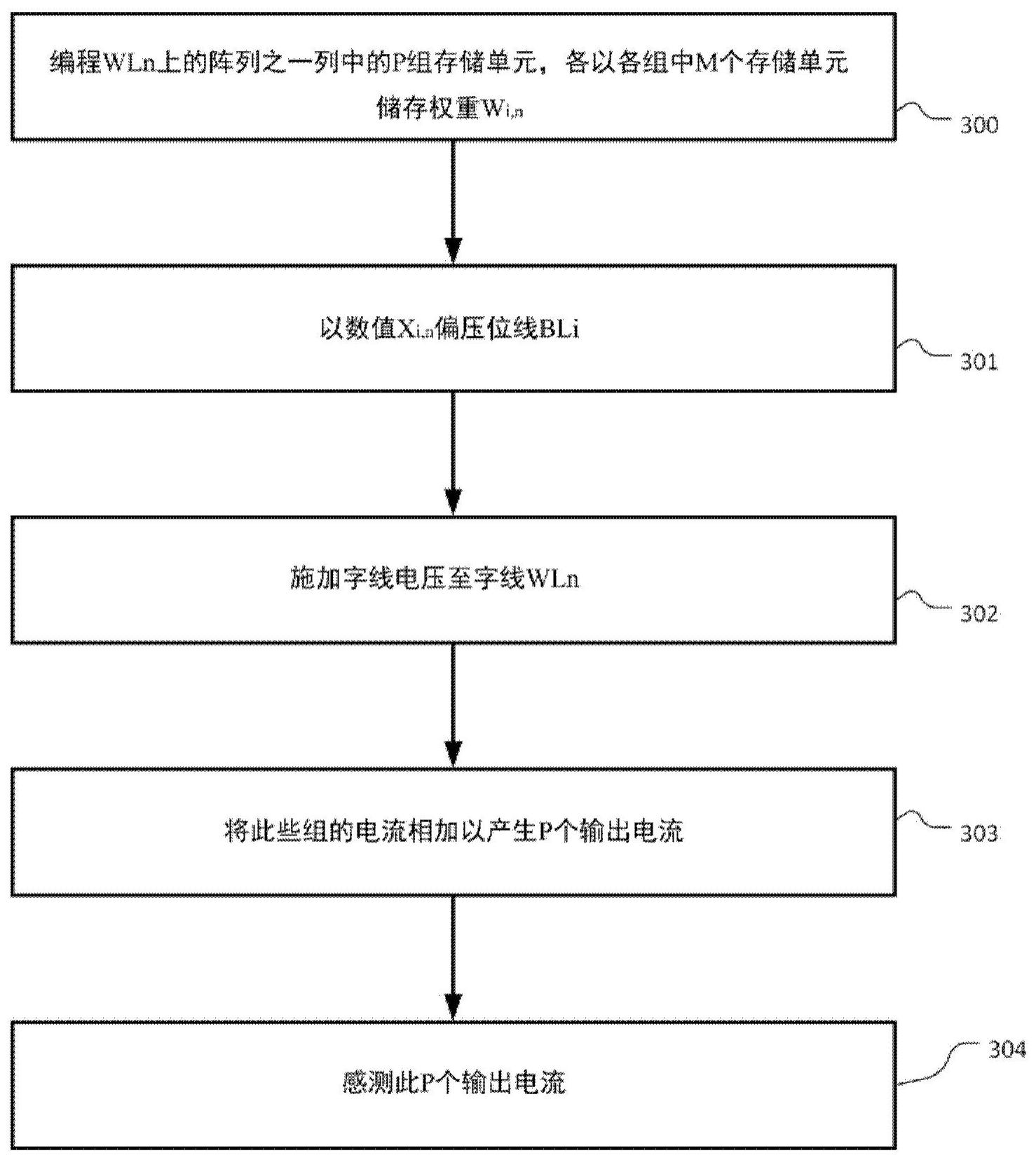

描述一种用于存储器内乘法与累加函数的技术。在一个方面,此技术提供了一种 使用存储单元阵列的方法,例如或非(NOR)快闪架构存储单元。 所描述的一种方法包括依数值Wi,n(i从0至M-1)编程在特定字线WLn上和在多条位 线BLi(i从0至M-1)上的阵列的一行中的M个存储单元,或存取已编程的存储单元,例如控制 控行译码器以选择字线而用于特定一行的编程单元。数值Wi,n可以为使用字线WLn上及位线 BLi上的单元而对应的乘积和或乘法与累加函数中的权重、系数、或项目。数值Wi,n可以基于 每个单元的多个位元。在NOR快闪存储器实施例中,数值Wi,n对应于存储单元的阈值。再者, 此方法包括依输入数值Xi,n分别偏压位线BLi(i从0至M-1),以用于字线WLn上的此些单元。 输入数值可以是类比偏压电压,其是回应于针对乘积和函数的每个项目的多位元数字输入 信号,使用数模转换器而产生。此方法包括将字线电压施加到特定字线WLn,使得此行上的 存储单元传导对应于来自此行中各个单元的乘积Wi,n×Xi,n的电流。由此行中的单元所传导 的电流表示乘积和函数的对应项目,并且被相加以产生表示项目之和的输出电流。输出电 流被感测以提供乘积和函数的存储器内计算的结果。 在一些实施例中,阵列中此行存储单元可以被配置为P组每组M个单元,且M大于1。 来自P组M个单元的每组的输出电流可以并行地相和。 在一些实施例中,可以编程或存取阵列的多行,并根据应用于配置操作的控制电 4 CN 111722830 A 说 明 书 2/9 页 路和命令,依次为每行计算结果。再者,在一些实施例中,可以在单个感测操作中编程或存 取阵列的多行,并根据控制电路和用于配置操作的命令为每条位线计算结果。 再者,描述存储器内乘法与累加电路。在本文描述的示例中,此电路包括存储器阵 列,此存储器阵列包括在例如NOR快闪阵列一组字线上和一组位线上的存储单元,其储存相 应的权重Wi,n。行译码器耦接到此组字线,且配置为施加字线电压以选择此组中的字线。多 个位线偏压电路是被包括。位线偏压电路具有连接到输入数据路径的相应输入,且具有连 接到此组位线中对应的位线的输出。位线偏压电路产生位线偏压电压用于对应的位线,作 为相应输入上的输入数值Xi,n的函数。电路包括多个电流感测电路,多个电流感测电路中的 每一个被连接以从此组位线中对应的多数子集合位线接收并行的电流,并回应于来自相应 的多数子集合位线的此些电流相加而产生输出。在一些实施例中,多数子集合位线可以是 整组位线。在其他实施例中,电路可以包括并行使用的多个多数子集合。 在其他实施例中,行译码器耦接到此组字线,且被配置为施加字线电压以选择此 组中的多个字线,以并行存取多个存储单元。多个位线偏压电路被包括。位线偏压电路具有 连接到输入数据路径的相应输入,且具有连接到此组位线中对应的位线的输出。位线偏压 电路产生位线偏压电压用于对应的位线,作为相应输入上的输入数值Xi,n的函数。电路包括 多个电流感测电路,多个电流感测电路中的每一个直接或通过开关连接,以从选定的一个 位线接收电流,并回应于来自所选位线上相应的多个存储单元的电流相加而产生输出。 在一些实施例中,位线偏压电路可包括数模(digital-to-analog,DAC)转换器。 再者,在本文描述的一个电路中,阵列中的一些或所有存储单元是连接在相应的 位线和公共参考线之间,公共参考线可被称为与NOR快闪阵列连接而作为公共来源线。来源 线偏压电路可以连接到公共来源线,并连接到位线偏压电路,以补偿公共来源线上的电压 变化。 为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并配合附图详 细说明如下。 附图说明 图1绘示依照本文所述实施例的存储器内乘积和电路的简易示意图。 图2绘示依照本文所述实施例的存储器内乘积和电路的替代实施的简易示意图。 图3绘示依照本文所述实施例的乘积和电路的详细示意图。 图4绘示依照本文所述实施例的存储单元所储存的权重或系数所对应的阈值电压 分布图。 图5绘示依照本文所述实施例的可用于位线偏压电路的范例性数模转换器的示意 图。 图6绘示依照本文所述实施例的适用于感测电流总和的范例性感测放大器的示意 图。 图7绘示图6的感测放大器的运作的时序图。 图8绘示图6的感测放大器的运作的逻辑表格。 图9绘示依照本文所述实施例的存储器内乘积和操作的流程图。 图10绘示依照本文所述实施例的替代性乘积和电路的详细示意图。 5 CN 111722830 A 说 明 书 3/9 页 【附图标记说明】 10、20:阵列 11:字线电路 12:位线电路 13、85、86、215:节点 14、90、91、590、591、SA、SA0~SA127:感测放大器 15:控制电路 21:公共来源线 22:源极偏压控制电路 23、92、93、592、593:线 50、51:存储单元区块 55、555:行译码器 58、59、60、61:晶体管 68、69、70、71:存储单元 75、76、77、78:位线钳位晶体管 80、81、82、83、580、581、582、583:数模转换器 100、101、102、103、104:分布 150:暂存器 151:多工器 152:梯形电阻器 153、160:运算放大器 154:p通道晶体管 155、163:反馈 161:n通道晶体管 162:电阻器 200:电流 201:感测节点 210、211、212、213:晶体管组 220:参考电流产生器 221、222、223:致能晶体管 225、226、227:电流源晶体管 235:控制逻辑 240、241、242:反栅 230、231、232:闩锁器 300~304:流程步骤 550、551:区块 558、559、560、561、568、569、570、571、I_cell 1、I_cell 2:存储单元 565、566、567、568:位线钳位晶体管 585、586:开关 6 CN 111722830 A 说 明 书 4/9 页 B0、B1、B2:三位元输出数值 Bit0、Bit1、Bit2:三位元输出 BL0、BL1~BL511:位线 BLT0~BLT15:区块选择线 BGREF:带隙参考电压 clk:感测时钟信号 EN0、EN1、EN2、Sense0、Sense1、Sense2:控制信号 EN[2:0]:致能信号 I-ref:参考电流 ISENSE:输出电流 MPA[2:0]、MSA[2:0]、MSB[2:0]:晶体管组 MPB[2:0]:晶体管 VREF:参考电压 W0,0;W1,0;W0,1;W1,1:权重 WL0、WL1~WL511、WLn、WL480:字线 X0,n、X1,n~~X511,n:输入