技术摘要:

本发明公开了一种FPGA模拟eMMC接口与ARM芯片高速通信的方法,包括以下步骤:FPGA模拟eMMC接口标准的高速通信数据线;FPGA模拟eMMC接口标准的数据收发;FPGA模拟eMMC接口标准的内部寄存器;FPGA模拟eMMC接口标准的数据传输。本发明在FPGA上模拟并实现ARM芯片具有的eMMC 全部

背景技术:

现场可编程逻辑器件FPGA,具有丰富的可配置的资源,可实现设计灵活复杂的逻 辑、时序、算法处理等设计,其功能模块并发性好,数据吞吐率高;广泛应用于在高速数据处 理,网络通信、各种电子仪器等领域。 eMMC是现在广泛使用的数据存储器,eMMC具有统一、高速的数据接口。不同厂家生 产的各种产品之间,在不需要做专门的接口匹配情况下实现稳定的数据通信。降低了产品 的开发难度以及时间和精力投入,减少了产品的开发周期。 ARM芯片具有较低功耗,较强的图形处理能力,灵活的人机输入接口。特别是搭载 Android操作系统之后,具有简洁、直观、方便的人机交互界面,丰富的输入输出接口,广泛 应用于移动便携式设备上。 FPGA主要是面向高性能的领域,其接口主要是高速的通用IO管脚,以及10Gbps级 别的专用Serdes;而ARM芯片主要是面向低功耗领域的手持设备,其接口主要是低速接口 (I2C、SPI、串口等),高速接口主要是USB、eMMC、LCD等;由于FPGA与ARM发展方向不同,一般 ARM芯片和FPGA只能通过低速接口(I2C、SPI、串口等,通信速率通常小于100Mbps)进行直接 通信;在需要FPGA的复杂而灵活设计以及ARM低功耗优越的人机交互功能时,却缺乏高速通 信接口。

技术实现要素:

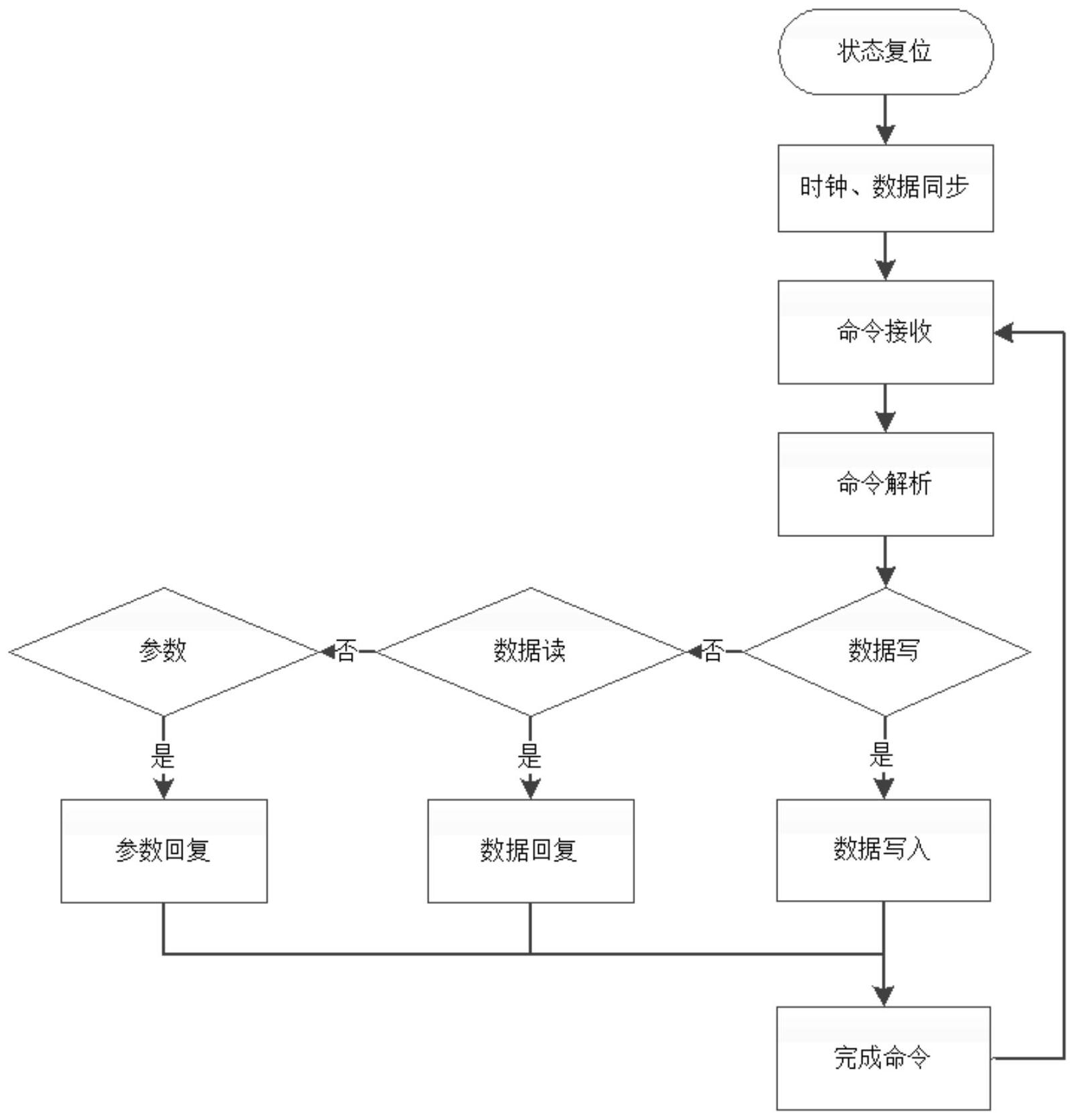

为解决现有技术中存在的问题,本发明的目的是提供一种FPGA模拟eMMC接口与 ARM芯片高速通信的方法,实现普通ARM芯片与FPGA之间的高速通信的目的。 为实现上述目的,本发明采用的技术方案是:一种FPGA模拟eMMC接口与ARM芯片高 速通信的方法,包括以下步骤: 步骤一、FPGA模拟eMMC接口标准的高速通信数据线; 步骤二、FPGA模拟eMMC接口标准的数据收发; 步骤三、FPGA模拟eMMC接口标准的内部寄存器; 步骤四、FPGA模拟eMMC接口标准的数据传输。 作为一种优选的实施方式,所述步骤一中,FPGA通过模拟eMMC设备的输入输出管 脚接口实现物理连接,FPGA模拟的输入输出管脚包括钟CLK管脚、命令和状态CMD管脚,通信 数据DAT0-7管脚和数据锁存信号DS管脚。 作为另一种优选的实施方式,所述步骤二具体包括: FPGA通过时钟CLK管脚边沿采集命令和状态CMD管脚,接收eMMC控制器命令,按照 eMMC协议要求,通过命令和状态CMD管脚向eMMC控制器回复状态,通过数据锁存信号DS管脚 3 CN 111581146 A 说 明 书 2/4 页 和通信数据DAT0-7管脚收发数据。 作为另一种优选的实施方式,所述步骤三具体包括: FPGA在通过eMMC接口接收到寄存器读取时,进入到参数读取状态,通过参数地址, 返回相应的参数数据。 作为另一种优选的实施方式,所述步骤四具体包括: FPGA在通过eMMC接口接收到数据命令时,进入到数据读取、写入状态,通过通信数 据DAT0-7管脚,以及数据锁存信号DS管脚读取或者写入数据;FPGA模拟eMMC接口部分与数 据生产逻辑、数据接收逻辑通过FIFO的方式进行数据握手完成数据的交互。 本发明的有益效果是: 本发明在FPGA上模拟并实现ARM芯片具有的eMMC接口,实现普通ARM芯片与FPGA之 间的高速通信的目的,可以弥补一般ARM芯片只能通过低速接口与FPGA进行直接通信的缺 点,实现高速通信的能力,而不需要定制化的ARM、FPGA芯片,拓宽ARM、FPGA芯片可选择范 围,简化设计难度、降低设计成本。 附图说明 图1为本发明实施例1中FPGA模拟eMMC接口功能的模块图; 图2为本发明实施例1中FPGA模拟eMMC接口功能的流程图; 图3为本发明实施例1中eMMC接口的通信管脚定义图; 图4为本发明实施例1中数据线DATA与锁存信号DS数据收发时的时序图。