技术摘要:

本发明公开了一种立体存储器元件及其制作方法,该立体存储器元件包含一基材、多个导电层、多个绝缘层、一储存层、一绝缘隔墙、一第一通道部、一第二通道部以及一第一导电插塞。这些导电层以及绝缘层彼此交错叠层位于基材上以形成一多层叠层结构。储存层穿过多层叠层结 全部

背景技术:

存储器元件是可携式电子装置,例如MP3播放器、数字相机、笔记本电脑、智能型手 机等...中重要的数据储存元件。随着各种应用程序的增加及功能的提升,对于存储器元件 的需求,也趋向较小的尺寸、较大的存储容量。而为了因应这种需求,目前设计者转而开发 一种包含有多个存储单元阶层叠层的立体存储器元件,例如垂直通道式立体NAND闪存元 件。 然而,随着元件的关键尺寸微缩至一般存储单元技术领域的极限,如何在现有设 备的制备工艺能力限制下,获得到更高的储存容量,已成了该技术领域所面临的重要课题。 因此,有需要提供一种先进的立体存储器元件及其制作方法,来解决已知技术所面临的问 题。

技术实现要素:

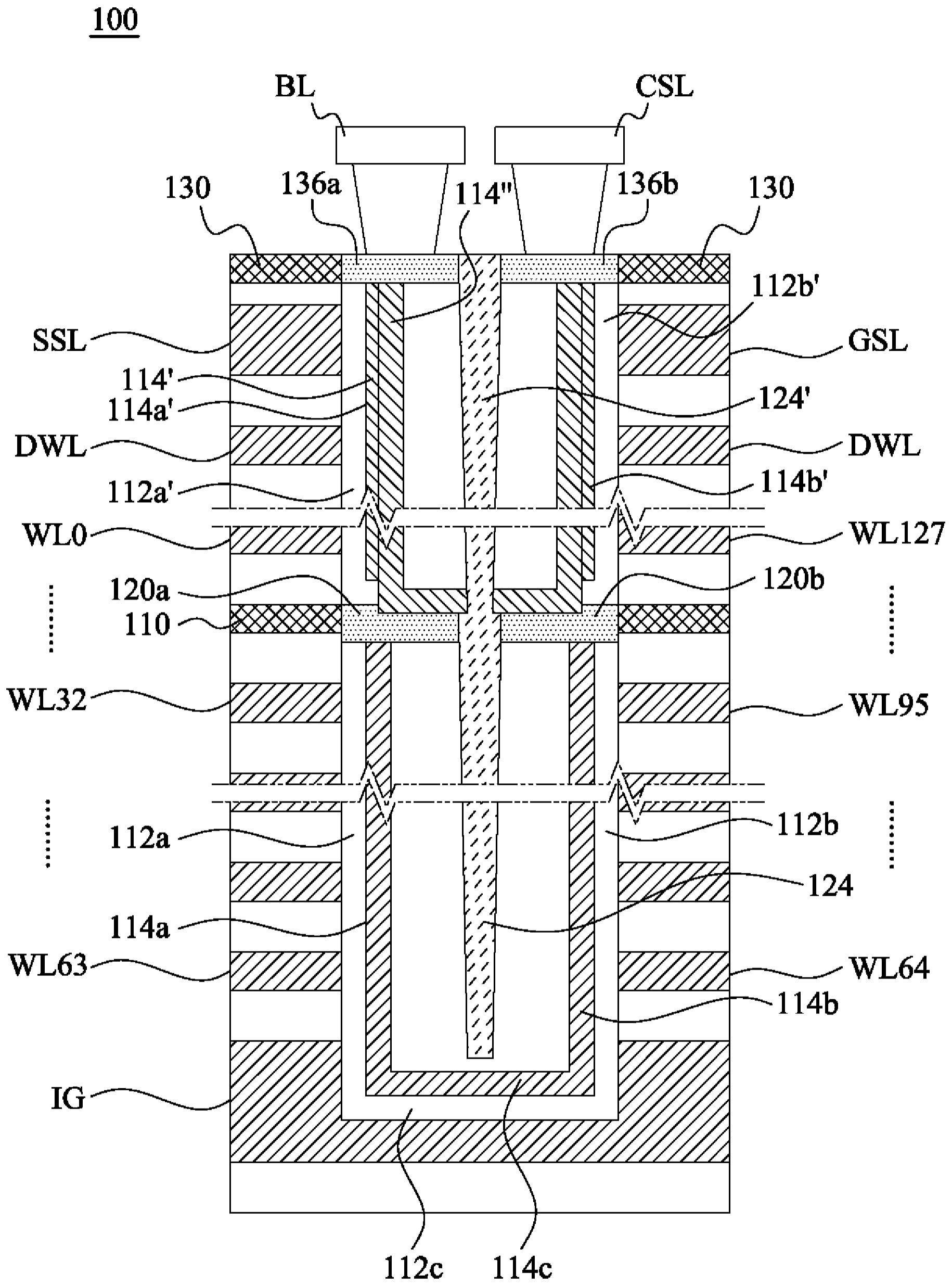

本说明书的一实施例公开一种立体存储器元件,其包含一基材、多个导电层、多个 绝缘层、一储存层、一绝缘隔墙、一第一通道部、一第二通道部以及一第一导电插塞。这些导 电层以及绝缘层彼此交错叠层位于基材上以形成一多层叠层结构。储存层穿过多层叠层结 构,且具有彼此分离的一第一串行部以及一第二串行部。第一通道部位于第一串行部的一 侧边,且第一串行部位于多层叠层结构与第一通道部之间。第二通道部位于第二串行部的 一侧边,且第二串行部位于多层叠层结构与第二通道部之间。第一通道部与第二通道部各 包含一上通道部份以及一下通道部份。第一导电插塞连接于上通道部份以及下通道部份之 间。 在本说明书的其他实施例中,立体存储器元件还包含一刻蚀阻挡层位于多层叠层 结构中,且位于第一导电插塞一侧。 在本说明书的其他实施例中,立体存储器元件还包含一底部通道,且第一通道部 与该二通道的下通道部份为彼此分离的U型通道,且连接至底部通道的两端。 在本说明书的其他实施例中,立体存储器元件还包含一介电隔墙位于储存层的第 一、二串行部之间,介电隔墙包含一上部以及一下部,下部的顶端的截面宽于上部的底端的 截面。 在本说明书的其他实施例中,上通道部份包含一外通道层以及一内通道层,外通 道层位于储存层与内通道层之间,且与第一导电插塞分离。 在本说明书的其他实施例中,立体存储器元件还包含一第二导电插塞,其位于多 层叠层结构上方且连接至上通道部份。 在本说明书的其他实施例中,立体存储器元件还包含一刻蚀阻挡层,其位于多层 4 CN 111554689 A 说 明 书 2/9 页 叠层结构上方且位于第二导电插塞一侧。 在本说明书的其他实施例中,第一导电插塞与第二导电插塞的材质皆为掺杂的多 晶硅。 本说明书的另一实施例公开一种立体存储器元件的制作方法,其包含以下步骤: 交替沉积多个第一导电层以及第一绝缘层于一基材上;刻蚀一第一通孔穿越这些第一导电 层以及这些第一绝缘层;沉积一第一储存层于该第一通孔内;沉积一下通道部于该第一储 存层上;沉积一第一导电插塞接触该下通道部;交替沉积多个第二通道层以及第二绝缘层 于该第一导电插塞上;刻蚀一第二通孔穿越这些第二通道层以及这些第二绝缘层以暴露该 第一导电插塞;沉积一第二储存层于该第二通孔内;沉积一第二通道层于该第二储存层上; 刻蚀该第二储存层以及该第二通道层以暴露该第一导电插塞,且刻蚀后剩余的该第二通道 层位于该第二储存层的侧壁;沉积一第三通道层于刻蚀后剩余的该第二通道层上以形成一 第二通道部,其接触该第一导电插塞;以及沉积一第二导电插塞接触该第二通道部的顶端。 在本说明书的其他实施例中,立体存储器元件的制作方法还包含在沉积这些第二 通道层以及这些第二绝缘层前,刻蚀一第一沟道以切割该第一导电插塞、该第一储存层以 及该下通道部;沉积一第一介电隔墙以填入该第一沟道;刻蚀一第二沟道以切割该第二导 电插塞、该第二储存层以及该上通道部以暴露该第一介电隔墙;以及沉积一第二介电隔墙 以填入该第二沟道,并接触该第一介电隔墙。 半圆柱半导体存储器元件利用多步骤刻蚀方案增加总深宽度,使得具有正常刻蚀 能力的传统刻蚀工具仍然能够制造更高密度的半导体存储器元件。 以下将以实施方式对上述的说明作详细的描述,并对本发明之技术方案提供更进 一步的解释。 附图说明 为让本发明的上述和其他目的、特征、优点与实施例能更明显易懂,所附图式的说 明如下: 图1是绘示依照本发明的一实施例的立体半导体存储元件的剖面图; 图2A~图22A是绘示依照本发明的某些实施例的半导体存储元件制造方法于多个 步骤中的上视图; 图2B~图22B是绘示依照本发明的某些实施例的半导体存储元件制造方法于多个 步骤中的剖面图; 图23A是绘示依照本发明的另一实施例的立体半导体存储元件的上视图; 图23B是绘示沿图23A的剖面线23B-23B的剖面图;以及 图24绘示依照本发明的另一实施例的立体半导体存储元件的剖面图。 【符号说明】 100:存储器元件 200:存储器元件 102:基材 104:导体层 106:绝缘层 5 CN 111554689 A 说 明 书 3/9 页 110:刻蚀停止层 112:储存层 112’:储存层 112a:串行部 112b:串行部 112c:串行部 112a’:串行部 112b’:串行部 114:通道层 114’:通道层 114”:通道层 114a:通道部 114b:通道部 114a’:通道部 114b’:通道部 114a”:通道部 114b”:通道部 114c:通道部 116:孔洞 116’:孔洞 116a:凹部 116a’:凹部 118:介电填充柱 120:导电插塞层 120a:导电插塞 120b:导电插塞 122:沟槽 122’:沟槽 124:介电隔墙 124’:介电隔墙 130:刻蚀停止层 132:介电填充柱 136:导电插塞层 136a:导电插塞 136b:导电插塞 DWL:虚字线 WL(0~127):字线 BL:位线 IG:非门极 6 CN 111554689 A 说 明 书 4/9 页 SSL:串选择线 CSL:共同源极线 GSL:栅极选择线 T1:厚度 T2:厚度 W1:宽度 C1:宽度 C2:宽度 D1:深度 D2:深度 E1:宽度 E2:宽度