技术摘要:

本申请提供一种阵列基板以及显示面板,所述阵列基板包括:多级级联设置的GOA单元以及多条时钟信号总线,所述多条时钟信号走线与相应所述多级级联设置的GOA单元电性连接;每一级所述GOA单元均包括一第一输出晶体管,所述第一输出晶体管的源极与相应所述时钟信号总线连接 全部

背景技术:

阵列基板栅极驱动技术(Gate Driveron Array,简称GOA),是将栅极驱动电路集 成在显示面板的阵列基板上,以实现逐行扫描的驱动方式,从而可以省掉栅极驱动电路部 分,具有降低生产成本和实现面板窄边框设计的优点,为多种显示面板所使用。 在现有的GOA电路中,各级GOA单元中的输出晶体管用于根据相应的时钟信号输出 扫描信号,由于时钟信号在时钟信号总线中存在传输损耗,会造成输出波形的阻容延迟,使 得扫描信号形成上升沿和下降沿,并且各级级联设置的GOA单元输出的扫描信号的上升时 间以及下降时间不一致,进而导致显示面板充电不均一。

技术实现要素:

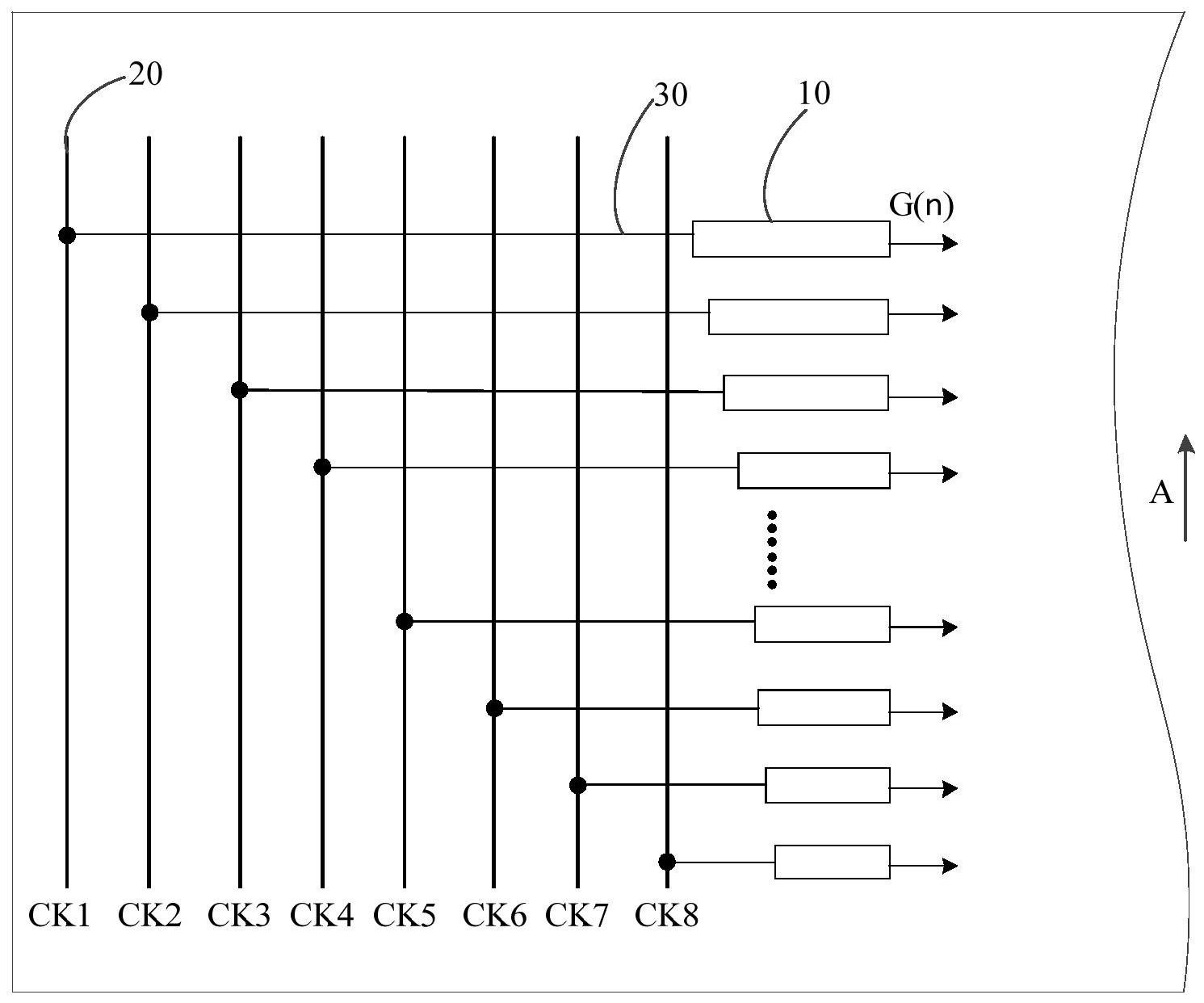

本申请提供一种阵列基板以及显示面板,以解决现有技术中各级级联的GOA单元 输出的扫描信号的上升时间以及下降时间不一致,进而导致显示面板充电不均一的技术问 题。 本申请提供一种阵列基板,其包括:多级级联设置的GOA单元以及多条时钟信号总 线,所述多条时钟信号走线与相应所述多级级联设置的GOA单元电性连接; 每一级所述GOA单元均包括一第一输出晶体管,所述第一输出晶体管的源极与相 应所述时钟信号总线连接,所述第一输出晶体管的漏极与相应所述GOA单元的扫描信号输 出端电性连接;其中, 在所述多级级联设置的GOA单元中,多个所述第一输出晶体管的尺寸沿着预设方 向增大,所述预设方向为任一所述时钟信号总线上的信号传递方向。 在本申请提供的阵列基板中,多个所述第一输出晶体管的尺寸沿着所述预设方向 依次增大。 在本申请提供的阵列基板中,所述阵列基板包括多个沿列方向排布的第一GOA单 元区域;每个所述第一GOA单元区域均包括至少一所述GOA单元; 其中,每一所述第一GOA单元区域内的所述第一输出晶体管的尺寸相同。 在本申请提供的阵列基板中,每一所述时钟信号总线的宽度沿着所述预设方向减 小。 在本申请提供的阵列基板中,所述多条时钟信号总线沿行方向依次排布;其中, 在所述行方向上,靠近所述多级级联设置的GOA单元的所述时钟信号总线的宽度 小于远离所述多级级联设置的GOA单元的所述时钟信号总线的宽度。 在本申请提供的阵列基板中,所述阵列基板还包括多条时钟信号连接走线,每一 级所述GOA单元均通过相应所述时钟信号连接走线与相应所述时钟信号总线连接; 所述阵列基板包括多个沿列方向排布的第二GOA单元区域,每一所述第二GOA单元 3 CN 111583882 A 说 明 书 2/6 页 区域均包括多个GOA单元,所述多个GOA单元与所述多条时钟信号总线一一对应连接;其中, 在任一所述第二GOA单元区域中,所述时钟信号连接走线的宽度各不相同。 在本申请提供的阵列基板中,在所述多级级联设置的GOA单元中,连接同一所述时 钟信号总线的所述GOA单元对应的所述时钟信号连接走线的宽度相同。 在本申请提供的阵列基板中,每一级所述GOA单元还均包括一第二输出晶体管;所 述第二输出晶体管的源极与相应所述时钟信号总线连接,所述第二输出晶体管的漏极与相 应所述GOA单元的级联信号输出端电性连接;其中, 在所述多级级联设置的GOA单元中,多个所述第二输出晶体管的尺寸沿着所述预 设方向增大。 在本申请提供的阵列基板中,所述第一输出晶体管和所述第二输出晶体管均为低 温多晶硅薄膜晶体管或氧化物半导体薄膜晶体管。 相应的,本申请还提供一种显示面板,所述显示面板包括以上任意一项所述的阵 列基板。 本申请提供一种阵列基板以及显示面板,该阵列基板包括多级级联设置的GOA单 元以及多条时钟信号总线,所述多条时钟信号走线与相应所述GOA单元电性连接,其中,每 一级GOA单元均包括一第一输出晶体管,在时钟信号总线中的信号传递方向上,通过将多个 第一输出晶体管的尺寸增大,可以降低各级级联设置的GOA单元输出的扫描信号之间的差 异,进而提高显示面板的充电均一性。 附图说明 为了更清楚地说明本申请实施例中的技术方案,下面将对实施例描述中所需要使 用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于 本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附 图。 图1是本申请提供的阵列基板的第一结构示意图; 图2是本申请提供的阵列基板的第二结构示意图; 图3是本申请提供的GOA单元的电路结构示意图; 图4是本申请提供的扫描信号的波形图; 图5是本申请提供的阵列基板的第三结构示意图; 图6是本申请提供的阵列基板的第四结构示意图; 图7是本申请提供的阵列基板的第五结构示意图; 图8是本申请提供的阵列基板的第六结构示意图; 图9是本申请提供的阵列基板的第七结构示意图。