技术摘要:

本发明公开了一种SOI FinFET器件及其制作方法,其中所述SOI FinFET器件包括:衬底,在衬底上具有掺杂形成成组的源区和漏区;每一组源区和漏区之间的上方为第一区域、第二区域、第三区域和第四区域中的任一区域;第一区域的衬底上方依次设置为高K介质层、第一掺杂层、第 全部

背景技术:

阈值电压决定了MOS(Metal-Oxide-Semiconductor,金属-氧化物-半导体)器件的 工作电流和开关速度,静态功耗等性能,是MOS器件的关键参数,如何精确控制器件的阈值 电压是MOS器件制造的关键技术。 Fin FET(Fin Field-Effect Transistor,鳍式场效应晶体管)器件的栅极一般采 用高K(high-k,HK)金属栅工艺,栅极有效功函数决定了高K金属器件的阈值电压,目前高K 金属栅SOI(Silicon-On-Insulator,绝缘体上硅)FinFET器件阈值电压的调节方式主要是 通过控制栅极功函数金属的厚度。实验表明,在一定的厚度范围内,栅极整体的有效功函数 随着功函数金属层的厚度改变而改变,其中P型功函数金属TiN(氮化钛)比较典型,TiN的厚 度基本和栅极整体功函数成正比,厚度越大,栅极有效功函数越大。可以认为栅极功函数的 变化完全来源于TiN厚度的变化,因此改变TiN厚度的方法能够调节栅极有效功函数,达到 控制阈值电压的目的。除了功函数金属的厚度调节,高K金属栅器件也采用过在高K介质层 之上第一层金属栅上离子注入杂质的方式调节阈值电压,在PMOS(Positive channel- Metal-Oxide-Semiconductor,P型金属氧化物半导体)区域的第一层金属栅注入可增大有 效功函数的掺杂剂,在NMOS(Negative channel-Metal-Oxide-Semiconductor,N型金属氧 化物半导体)区域的一层金属栅注入可减小有效功函数的掺杂剂,以此调节阈值电压。 上述现有方案中通过功函数金属厚度调节阈值电压,在电压的调制幅度上有局限 性。有数据表明,随着功函数金属厚度的增加,栅极有效功函数的变化率逐渐降低,直到某 个临界厚度之后不再改变,在制作超低阈值电压器件的时候,阈值电压可能无法满足需求; 其次,栅极功函数金属的厚度过厚会影响到栅极后续金属的填充,如图1所示,功函数金属 层102越厚,留给栅极接触金属101的空间就越小,在制作PMOS,尤其是超低阈值电压PMOS (ultra low Vt PMOS,ULVT PMOS)时,需要很厚的栅极功函数金属,容易造成填充问题,会 影响到栅极电阻率。因此,现有技术存在如下缺点:制作超低阈值电压器件时存在局限性, 同时较厚的栅极金属会导致填充问题从而影响栅极的电阻率。

技术实现要素:

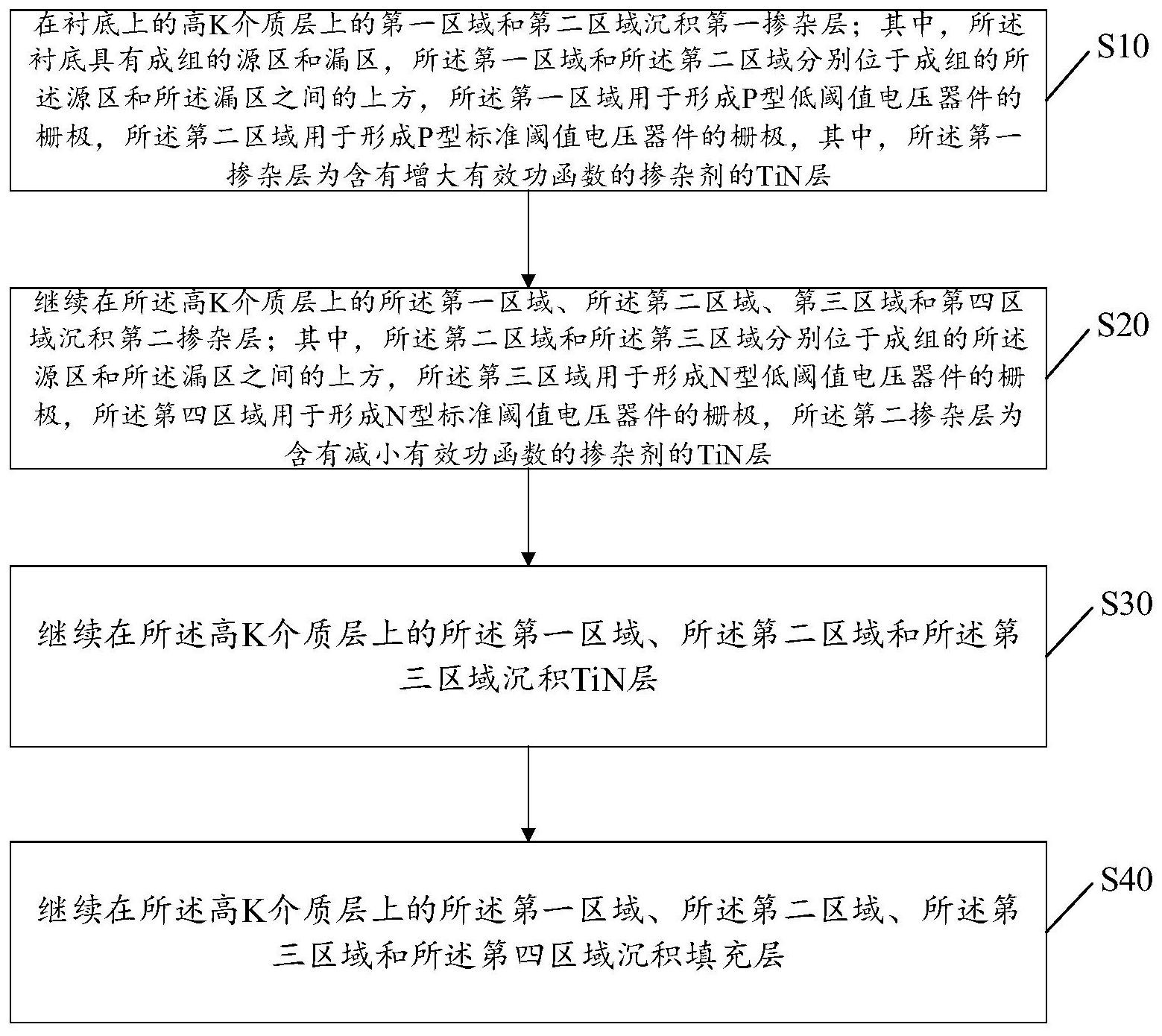

鉴于上述问题,本发明提出了一种SOI FinFET器件及其制作方法,其中器件的栅 极结构不需很厚的栅极功函数金属,栅极电阻率稳定;所述制作方法能够有效的避免栅极 金属的填充问题,且同时制作P型、N型低阈值电压器件,P型、N型标准阈值电压器件至同一 芯片上,解决了局限性问题。 第一方面,本申请通过本申请的一实施例提供如下技术方案: 一种SOI FinFET器件,包括: 衬底,在所述衬底上具有掺杂形成成组的源区和漏区; 4 CN 111554679 A 说 明 书 2/8 页 每一组所述源区和所述漏区之间的上方为第一区域、第二区域、第三区域和第四 区域中的任一区域;其中,所述第一区域用于形成P型低阈值电压器件的栅极,所述第二区 域用于形成P型标准阈值电压器件的栅极,所述第三区域用于形成N型低阈值电压器件的栅 极,所述第四区域用于形成N型标准阈值电压器件的栅极; 所述第一区域由下至上依次设置为高K介质层、第一掺杂层、第二掺杂层、TiN层以 及填充层;其中,所述第一掺杂层为含有增大有效功函数的掺杂剂的TiN层,所述第二掺杂 层为含有减小有效功函数的掺杂剂的TiN层; 所述第二区域由下至上依次设置为所述高K介质层、所述第一掺杂层、所述第二掺 杂层、所述TiN层以及所述填充层; 所述第三区域由下至上依次设置为所述高K介质层、所述第二掺杂层、所述TiN层 以及所述填充层; 所述第四区域由下至上依次设置为所述高K介质层、所述第二掺杂层以及所述填 充层。 优选地,所述第一区域、所述第二区域、所述第三区域以及所述第四区域中任一个 或多个区域的所述第二掺杂层上方相邻一层均设置有刻蚀阻挡层。 优选地,所述第一区域中的所述TiN层的厚度大于所述第二区域中的所述TiN层的 厚度。 优选地,所述填充层由下至上依次为TiAl层,TiN层以及金属钨。 优选地,所述第一掺杂层为BF2离子的TiN层,所述第二掺杂层为P离子的TiN层。 第二方面,基于同一发明构思,本申请通过本申请的一实施例提供如下技术方案: 一种SOI FinFET器件的制作方法,包括: 在衬底上的高K介质层上的第一区域和第二区域沉积第一掺杂层;其中,所述衬底 具有成组的源区和漏区,所述第一区域和所述第二区域分别位于成组的所述源区和所述漏 区之间的上方,所述第一区域用于形成P型低阈值电压器件的栅极,所述第二区域用于形成 P型标准阈值电压器件的栅极,其中,所述第一掺杂层为含有增大有效功函数的掺杂剂的 TiN层; 继续在所述高K介质层上的所述第一区域、所述第二区域、第三区域和第四区域沉 积第二掺杂层;其中,所述第二区域和所述第三区域分别位于成组的所述源区和所述漏区 之间的上方,所述第三区域用于形成N型低阈值电压器件的栅极,所述第四区域用于形成N 型标准阈值电压器件的栅极,所述第二掺杂层为含有减小有效功函数的掺杂剂的TiN层; 继续在所述高K介质层上的所述第一区域、所述第二区域和所述第三区域沉积TiN 层; 继续在所述高K介质层上的所述第一区域、所述第二区域、所述第三区域和所述第 四区域沉积填充层。 优选地,所述在衬底上的高K介质层上的第一区域和第二区域沉积第一掺杂层,包 括: 在衬底上的高K介质层上沉积第一掺杂层; 在所述第一掺杂层上涂布BARC层,并剥除所述第三区域和所述第四区域的所述 BARC层; 5 CN 111554679 A 说 明 书 3/8 页 采用刻蚀方法去除所述第三区域和所述第四区域的所述第一掺杂层。 优选地,所述在所述高K介质层上的所述第一区域、所述第二区域、第三区域和第 四区域沉积第二掺杂层之后,且所述在所述高K介质层上的所述第一区域、所述第二区域和 所述第三区域沉积TiN层之前,还包括: 在所述第一区域、所述第二区域、所述第三区域和所述第四区域沉积刻蚀阻挡层。 优选地,所述在所述高K介质层上的所述第一区域、所述第二区域和所述第三区域 沉积TiN层,包括: 在所述刻蚀阻挡层上方沉积第一层所述TiN层; 对所述第二区域和所述第三区域刻蚀至所述刻蚀阻挡层; 继续在所述刻蚀阻挡层上方层积第二层所述TiN层; 对所述第四区域刻蚀至所述刻蚀阻挡层。 优选地,所述在所述高K介质层上的所述第一区域、所述第二区域、所述第三区域 和所述第四区域沉积填充层,包括: 在所述高K介质层上的所述第一区域、所述第二区域、所述第三区域和所述第四区 域依次沉积TiAl层,TiN层以及金属钨。 本发明提供的一种SOI FinFET器件,通过TiN层以及第一/第二掺杂层对栅极阈值 电压进行影响,使得该SOI FinFET器件的栅极结构具有更大范围的阈值电压调整范围,进 而超低阈值电压P型器件(即第一区域和第二区域)不再需要厚的功函数层,P型器件栅极金 属填充问题得到了很好的改善。 本发明提供的一种SOI FinFET器件的制作方法,在形成金属栅第一层时,先沉积 TiN并掺杂P型器件(即第一区域和第二区域)所需的增大有效功函数的掺杂剂,然后刻蚀掉 N型区域(即第三区域和第四区域)的TiN,再沉积TiN并掺杂N型区域所需的减小有效功函数 的掺杂剂,掺杂计量可控,从而可控制阈值电压。相比于现有技术中通过改变栅极功函数层 厚度调节阈值电压的方式相比,调节幅度更大,解决了局限性问题;对于超低阈值电压P型 FinFET器件不再需要厚的功函数层,P型器件的栅极金属填充问题得到较大改善。进一步 的,在本发明实施例中,对于各阈值电压类型的器件的不同功函数需求,无需通过杂质计 量,而是通过后续在各区域沉积相应厚度的功函数金属层TiN来满足,最后完成栅极金属的 填充。针对P型低阈值电压器件、P型标准阈值电压器件、N型低阈值电压器件以及N型标准阈 值电压器件,沉积的功函数金属层厚度递减,从而可以省去了多次沉积、掺杂、和刻蚀步骤, 并且可将P型、N型低阈值电压器件,P型、N型标准阈值电压器件制作到同一芯片上,使得该 制作工艺大大的降低了制作成本。 上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段, 而可依照说明书的内容予以实施,并且为了让本发明的上述和其它目的、特征和优点能够 更明显易懂,以下特举本发明的