技术摘要:

本发明提供一种改善介电层孔隙的方法,提供基底、位于基底上相互间隔的多个多晶硅栅结构及其上的氮化硅、位于多晶硅栅结构侧壁的第一至第三侧墙;去除第二、第三侧墙及氮化硅;沉积氮化硅层和氧化硅层,旋涂光刻胶以填充满多晶硅栅结构之间空隙;去除多晶硅栅结构上的 全部

背景技术:

现行的HKMG(高介电常数金属栅极)先进逻辑芯片的栅极制备工艺,主要分为:伪 栅极(dummy poly)工艺制备临时栅极来定义源、漏极,去除伪栅极dummy poly实现金属栅 的沉积。其中去除伪栅极dummy poly工艺中,如何在不损伤源漏极结构的前提下完成栅极 平坦化对整个芯片性能至关重要。由于随着器件结构越来越小,栅极间容易在氧化层 (oxide)沉积过程中出现空隙,并在之后的栅极平坦化过程中暴露出来,最终在金属栅沉积 时保留栅极金属而影响芯片性能。 因此,需要提出一种新的改善栅极间介电层孔隙的方法来解决上述问题。

技术实现要素:

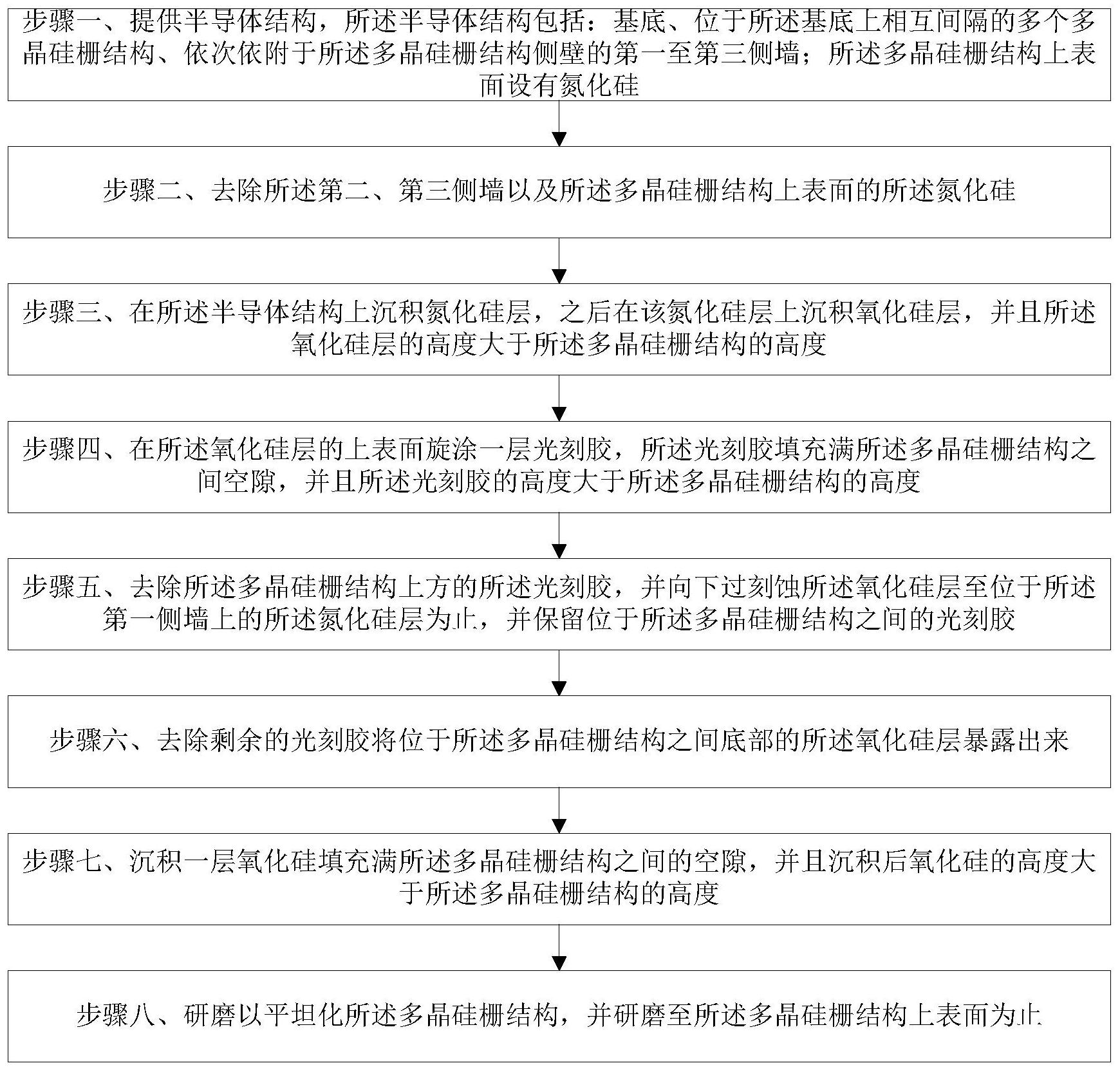

鉴于以上所述现有技术的缺点,本发明的目的在于提供一种改善介电层孔隙的方 法,用于解决现有技术中栅极之间的氧化层在其沉积过程中容易出现孔隙,从而在后续栅 极平坦化的过程中暴露出来,进而影响芯片性能的问题。 为实现上述目的及其他相关目的,本发明提供一种改善介电层孔隙的方法,该方 法至少包括以下步骤: 步骤一、提供半导体结构,所述半导体结构包括:基底、位于所述基底上相互间隔 的多个多晶硅栅结构、依次依附于所述多晶硅栅结构侧壁的第一至第三侧墙;所述多晶硅 栅结构上表面设有氮化硅; 步骤二、去除所述第二、第三侧墙以及所述多晶硅栅结构上表面的所述氮化硅; 步骤三、在所述半导体结构上沉积氮化硅层,之后在该氮化硅层上沉积氧化硅层, 并且所述氧化硅层的高度大于所述多晶硅栅结构的高度; 步骤四、在所述氧化硅层的上表面旋涂一层光刻胶,所述光刻胶填充满所述多晶 硅栅结构之间空隙,并且所述光刻胶的高度大于所述多晶硅栅结构的高度; 步骤五、去除所述多晶硅栅结构上方的所述光刻胶,并向下过刻蚀所述氧化硅层 至位于所述第一侧墙上的所述氮化硅层为止,并保留位于所述多晶硅栅结构之间的光刻 胶; 步骤六、去除剩余的光刻胶将位于所述多晶硅栅结构之间底部的所述氧化硅层暴 露出来; 步骤七、沉积一层氧化硅填充满所述多晶硅栅结构之间的空隙,并且沉积后氧化 硅的高度大于所述多晶硅栅结构的高度; 步骤八、研磨以平坦化所述多晶硅栅结构,并研磨至所述多晶硅栅结构上表面为 止。 优选地,步骤一中的所述第二侧墙和第三侧墙都为氮化硅。 3 CN 111599761 A 说 明 书 2/4 页 优选地,步骤二中利用湿法刻蚀工艺去除所述第二、第三侧墙以及位于所述多晶 硅栅结构上表面的氮化硅。 优选地,步骤三中在所述半导体结构上沉积的所述氮化硅层填充了所述多晶硅结 构之间的基底上表面。 优选地,步骤五中采用干法刻蚀去除位于所述多晶硅栅结构上方的所述光刻胶。 优选地,步骤五中在所述干法刻蚀过程中,向下刻蚀所述光刻胶至所述多晶硅栅 结构上的所述氧化硅层停止;之后采用选择比高的气体刻蚀所述氧化硅层至位于所述第一 侧墙上的所述氮化硅层为止,并保留位于所述多晶硅栅结构之间的光刻胶保留。 优选地,步骤六中采用灰化工艺去除剩余的所述光刻胶。 优选地,步骤八中采用化学机械研磨工艺平坦化所述多晶硅栅结构。 优选地,步骤八中的所述化学机械研磨工艺采用等比例研磨所述氧化硅和所述氮 化硅层。 如上所述,本发明的改善介电层孔隙的方法,具有以下有益效果:本发明在刻蚀氧 化硅的过程中,通过保留栅极间的光刻胶,在后续栅极间再填充氧化硅来达到避免栅极间 孔隙的出现,进而在后续平坦化栅极的过程中,避免孔隙暴露,改善了工艺,提高了芯片性 能。 附图说明 图1显示为本发明所提供的半导体结构示意图; 图2显示为本发明去除第二、第三侧墙以及多晶硅栅结构上的氮化硅后的结构示 意图; 图3显示为本发明在半导体结构上沉积氮化硅层后的结构示意图; 图4显示为本发明中在氮化硅层上沉积氧化硅层后的结构示意图; 图5显示为本发明中在氧化硅层上旋涂光刻胶后的结构示意图; 图6显示为本发明去除多晶硅栅结构上方的光刻胶后的结构示意图; 图7显示为本发明过刻蚀氧化硅层后的结构示意图; 图8显示为本发明去除剩余光刻胶后将多晶硅栅结构之间的氧化硅层暴露出的结 构示意图; 图9显示为本发明沉积氧化硅以填充多晶硅栅结构之间空隙的结构示意图; 图10显示为本发明对多晶硅栅结构平坦化后的结构示意图; 图11显示为本发明改善介电层孔隙的方法的流程图。