技术摘要:

一种LDMOS器件及其制作方法,所述LDMOS器件包括:衬底,所述衬底内形成有漂移区;栅极结构,位于所述漂移区一侧的所述衬底上,并覆盖部分所述漂移区;漏极区,位于所述栅极结构一侧的漂移区内;位于所述衬底上的隔离结构,所述隔离结构位于所述漏极区与所述栅极结构之 全部

背景技术:

横向扩散金属氧化物半导体(La t e r a l l y D i f f u s e d M e t a l O x i d e Semiconductor,LDMOS)晶体管,由于其更容易与互补金属氧化物半导体(Complementary Metal Oxide Semiconductors,CMOS)的逻辑工艺兼容而被广泛应的用于功率集成电路中。 而在功率集成电路中,器件的源漏击穿电压-导通电阻(BVDss-Rdson)特性对于设计高效的 功率应用电路具有重要意义。 通常,LDMOS的Rdson和BVDss是相互制约的两个性能。如果Rdson减小,BVDss很可 能降低,反之亦然。因此,如何提高BVDss,且不增大Rdson,成为亟待解决的问题。

技术实现要素:

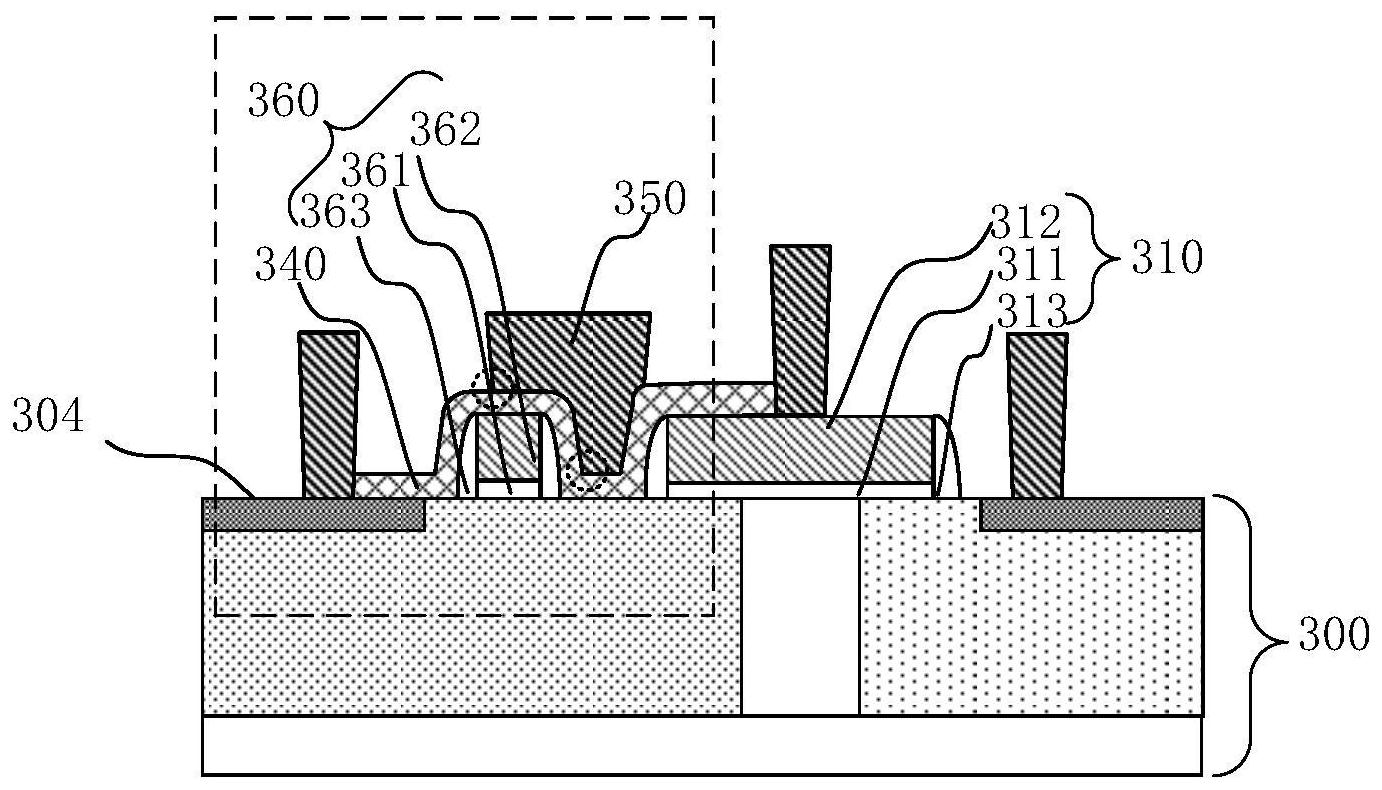

本发明实施例提供一种LDMOS器件及其制作方法,提高了器件击穿电压,且不会增 大导通电阻。 为解决上述问题,本发明实施例提供一种LDMOS器件,包括:衬底,所述衬底内形成 有漂移区;栅极结构,位于所述漂移区一侧的所述衬底上,并覆盖部分所述漂移区;漏极区, 位于所述栅极结构一侧的漂移区内;位于所述衬底上的隔离结构,所述隔离结构位于所述 漏极区与所述栅极结构之间;栅电极,位于所述栅极结构上且电连接所述栅极结构;漏电 极,位于所述漏极区上且电连接所述漏极区;阻挡层,保形覆盖所述栅电极和所述漏电极之 间的漂移区和隔离结构;位于所述阻挡层上的沟槽电极,所述沟槽电极位于所述隔离结构 与所述栅极结构之间,且至少覆盖部分隔离结构的顶部。 此外,本发明实施例还提供了一种LDMOS器件的制造方法,包括:提供衬底,所述衬 底内形成有漂移区;在所述衬底上形成栅极结构,所述栅极结构位于所述漂移区的一侧并 覆盖部分所述漂移区;在所述衬底上形成隔离结构,所述隔离结构位于所述漂移区上;在所 述栅极结构一侧的漂移区内形成漏极区,所述漏极区和所述栅极结构相隔离;其中,所述隔 离结构位于所述栅极结构和漏极区之间,且所述隔离结构与所述栅极结构相隔离;形成所 述栅极结构、隔离结构和漏极区后,形成保形覆盖所述漂移区和隔离结构的阻挡层;形成所 述阻挡层后,形成漏电极、栅电极和沟槽电极,其中,所述漏电极位于所述漏极区顶部且电 连接所述漏极区,所述栅电极位于所述栅极结构顶部且电连接所述栅极结构,所述沟槽电 极位于所述隔离结构与所述栅极结构之间的阻挡层上,且至少覆盖部分隔离结构的顶部。 与现有技术相比,本发明实施例的技术方案具有以下优点: 本发明实施例提供了一种LDMOS器件及其制作方法,在衬底上形成位于所述漏极 区与所述栅极结构之间的隔离结构,并使沟槽电极位于所述隔离结构与所述栅极结构之 间,且至少覆盖部分隔离结构的顶部,即,沟槽电极下方朝向漏极区的一侧与衬底之间设置 了隔离结构,所述隔离结构和阻挡层相当于位于沟槽电极下方朝向漏极区的一侧与衬底之 4 CN 111613663 A 说 明 书 2/11 页 间的隔离层,与隔离层仅包括阻挡层的方案相比,所述隔离结构的设置增大了所述沟槽电 极下方朝向漏极区的一侧与衬底之间的隔离层厚度,使得该位置处不易发生击穿,进而提 高器件击穿电压。 同时,本发明实施例不改变所述半导体结构中的其他部件(例如:衬底内的功能区 布局、各功能区的离子注入浓度,以及栅源漏的电极结构),因而不会增大器件的导通电阻, 使得本发明实施例中的LDMOS器件在提高器件击穿电压的同时,不会增大导通电阻。 附图说明 图1为一种LDMOS器件的结构示意图; 图2为本发明一实施例中的LDMOS器件的结构示意图; 图3为图2中虚线框内结构的局部放大图; 图4为本发明另一实施例中的LDMOS器件的结构示意图; 图5为图4中虚线框内结构的局部放大图; 图6至图9为图4所示实施例中的LDMOS器件与一种LDMOS器件的性能对比图; 图10至图15是本发明一实施例中LDMOS器件的制造方法中各步骤对应的结构示意 图; 图16至图18是本发明另一实施例中LDMOS器件的制造方法中各步骤对应的结构示 意图。