技术摘要:

本发明涉及深度神经网络、激活函数、FPGA设计,为能够适用于实现多种不同类型的激活函数,提高所述激活函数实现装置的计算效率,降低硬件功耗,降低硬件实现难度,本发明,可配置重用的分段式查找表激活函数实现装置,包括:输入数据处理单元、范围判断单元、地址索引 全部

背景技术:

从2006年的复兴开始,深度神经网络(Deep Neural Network,DNN),或所谓的深度 学习(Deep Learning,DL),已成为机器学习领域最重要的技术之一。近年,深度学习的快速 发展致使越来越多的人从事相关的研究工作,其在目标检测、自然语言处理、计算机视觉等 等领域成效斐然。深度神经网络(Deep Neural Networks,DNN)则是深度学习领域内的一个 重要模型,随着集成电路的发展、计算机处理能力的不断提高,神经网络再度成为人工只能 研究发展的热点。 卷积神经网络是一种源于人工神经网络的深度学习算法,它降低了网络模型的复 杂度,减少了权值的数量,这个优点在处理图像数据时尤为明显,避免了传统算法中复杂的 特征提取和数据重建过程。神经网络包含一系列并行工作的隐藏层,并且每一个隐藏层中 包含大量神经元。每一个神经元都从其他神经元中获取输入,再计算输出,激活函数就被用 在此处。在卷积神经网络中,使用线性的激活函数只有线性表达的能力,所以要使用非线性 的激活函数来增加卷积神经网路的表达能力,使其具有人工智能的真正意义。 现场可编程门阵列(Field-Programmable Gate Array,FPGA)是一种集成电路, 被设计为制造后可以由客户或设计者进行配置,因此被称为“现场可编程”。FPGA能通过硬 件编程实现并行运算,用FPGA来实现神经网络激活函数,能大大加快计算速度,达到实时性 要求,降低功耗。 然而,神经网络的任何硬件实现中最重要,最昂贵且难以实现的部分是神经元的 非线性激活函数。非线性的激活函数主要有sigmoid函数、tanh函数、softmax函数、ReLU函 数、ELU函数、PReLU函数等,这些激活函数都有其各自的优缺点,他们的实现难度也都不一 样。已有一些常用的tanh函数的FPGA硬件实现,针对sigmoid函数也有一系列优化方法。其 中激活函数逼近算法使用较多,泰勒级数逼近能力最差;坐标旋转算法和查找表法能达到 较高的精度,但是所需要FPGA资源较多。 虽然国内外对于激活函数的硬件加速器的实现已经有很多工作,但关注点仅仅在 提高硬件性能和节约硬件资源上,且多数工作只局限于单个激活函数在硬件上的实现。其 实目前集成电路和FPGA的发展已经远远能够满足了激活函数算法在硬件上的实现,对激活 函数的实现不应局限于硬件资源方面,应该更关注算法在硬件上的实现效率,以达到硬件 资源的充分利用。因此,本发明提出一款能在在充分利用硬件资源的基础上,提高计算效 率,降低功耗,尽可能减少存储面积资源,同时能通过配置适用于多种激活函数的实现装 置。 4 CN 111581593 A 说 明 书 2/7 页

技术实现要素:

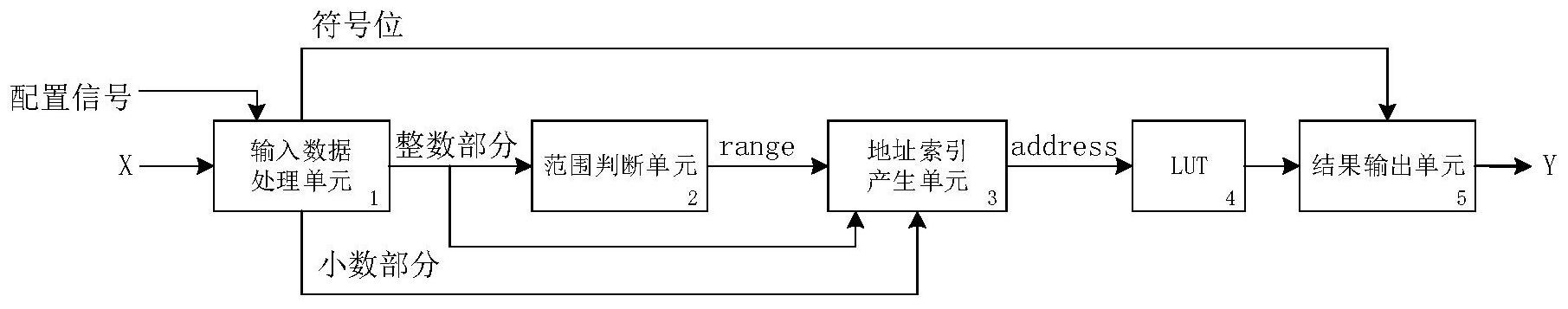

为克服现有技术的不足,本发明旨在提出一种基于查找表法的激活函数实现装 置,能够适用于实现多种不同类型的激活函数,提高所述激活函数实现装置的计算效率,降 低硬件功耗,降低硬件实现难度。此外,在此基础上,本发明提出了一种基于激活函数精确 度要求分段实现查找表的方案。基于该方案,可以实现以激活函数精确度为标准制定不同 大小的查找表,以完成对应的硬件设计,该方案能最大限度的降低查找表存储面积资源消 耗。所述实现装置同时支持16位和32位自定义定点数数据精度的计算,满足对激活函数不 同精度的要求。为此,本发明采取的技术方案是,可配置重用的分段式查找表激活函数实现 装置,包括: 输入数据处理单元:输入端连接符合16位或32位输入数据和配置信号,输出数据 符号、整数部分和小数部分,分别连接结果输出单元、范围判断单元和地址索引产生单元; 范围判断单元:输入端连接输入数据处理单元输出的整数部分,用于范围判断,输 出范围判断结果信号,输出端连接地址索引产生单元; 地址索引产生单元:输入端连接输入数据处理单元和范围判断单元,用于生成查 找表的地址索引,输出查找表地址信号,输出端连接查找表; 查找表:输入端连接地址索引产出单元,用于存储激活函数结果数据,使用BRAM资 源存储,输出端连接结果输出单元; 结果输出单元:输入端连接输入数据处理单元和查找表,用于产生最终结果,输出 输入数据对应的激活函数结果。 查找表分为四段内容,其中每一段存放激活函数不同部分的输出数据,每一段的 地址对应于激活函数的输入数据,这样就完成了激活函数的输入输出映射;每当输入数据 输入本激活函数实现装置时,硬件设备完成地址索引的计算,根据地址到查找表中找到对 应的激活函数输出数据。 输入数据处理单元由译码器构成,当输入数据和配置信号输入译码器时,译码器 根据不同位宽对输入数据进行译码,将输入数据的符号位、整数部分和小数部分分隔开,移 交给不同输出信号,完成输入数据处理的主要任务。 范围判断单元由三个比较器构成,当输入数据的整数部分输入时,所述范围判断 单元使用三个比较器确定该输入数据属于哪一个范围,所述三个比较器分别为与1比较、与 3比较、与6比较,由此可能得出四个结果,分别为0、1、2、3,对应四个分段范围[0,1)、[1,3)、 [3,6)、[6,∞),所述范围判断单元输出数据为两位宽,数值可能为0、1、2、3。 地址索引产生单元由多路选择器和移位器构成,多路选择器用于根据所述范围判 断单元传来的范围range信号选取输入数据索引的起始地址;移位器用于将输入数据数值 部分进行移位,以得到输入数据索引的偏移地址;将两项地址相加即可得到查找表最终的 索引地址。 地址索引产生单元中计算方式如表1所示: 表1地址索引计算规则 5 CN 111581593 A 说 明 书 3/7 页 表中range即所示范围判断单元的输出结果,data为所述输入数据处理单元的整 数部分输出和小数部分输出的结合,即输入数据的数值部分,n0~n3指为满足不同分段中的 相同精度要求而得出的不同位宽。 数字手写体识别装置,利用卷积神经网络实现手写体识别,其中采用激活函数实 现装置替换ReLU函数为Swish函数。 深度神经网络装置,其激活函数采用激活函数实现装置实现。 本发明的特点及有益效果是: 本发明提出了一种可配置重用的分段式查找表激活函数实现装置,并基于该装 置,在FPGA上实验并验证了tanh函数与sigmoid函数,均达到较好的实验结果。所述激活函 数实现装置在满足激活函数的精确度要求的基础上,使用分段结构,最大限度的减少存储 面积资源消耗,同时,在硬件算法上使用查找表法实现激活函数,极大提高了运算效率,降 低功耗。此外,本发明适用性极高,由于采用查找表法实现激活函数的逼近,理论上适用于 所有激活函数的实现,而且操作简单,易于实现,有很大的实用价值。 附图说明: 图1数据格式图。 图2硬件设计架构图。 图3输入数据处理单元架构图。 图4范围判断单元架构图。 图5地址索引产生单元架构图。