技术摘要:

本发明属于计算机视觉技术领域,公开了一种配置目标跟踪硬件加速控制方法、系统、存储介质及应用,完成对感兴趣区域的提取以及样本标签值的计算;完成对感兴趣区域目标特征提取,根据目标特点,选择灰度特征、颜色特征或者HOG特征进行配置;对提取的目标特征通过不同的 全部

背景技术:

在视频目标跟踪的过程中,许多目标跟踪算法通过C 或M语言进行实现,并部署 在CPU和GPU中,由于这些平台不能在实际场景下满足实时性的要求,因此目标跟踪算法的 高速处理是计算机视觉领域中一项具有应用价值的工作。 目前提出的目标跟踪加速算法很多都是基于传统FPGA设计方法进行实现。这类算 法大多数只针对单一场景且不能快速进行迭代更新以适应于多种实际环境。此外,随着算 法的复杂度越来越高,目标的特征提取算法很难利用硬件描述语言VHDL或者Verilog进行 实现。

技术实现要素:

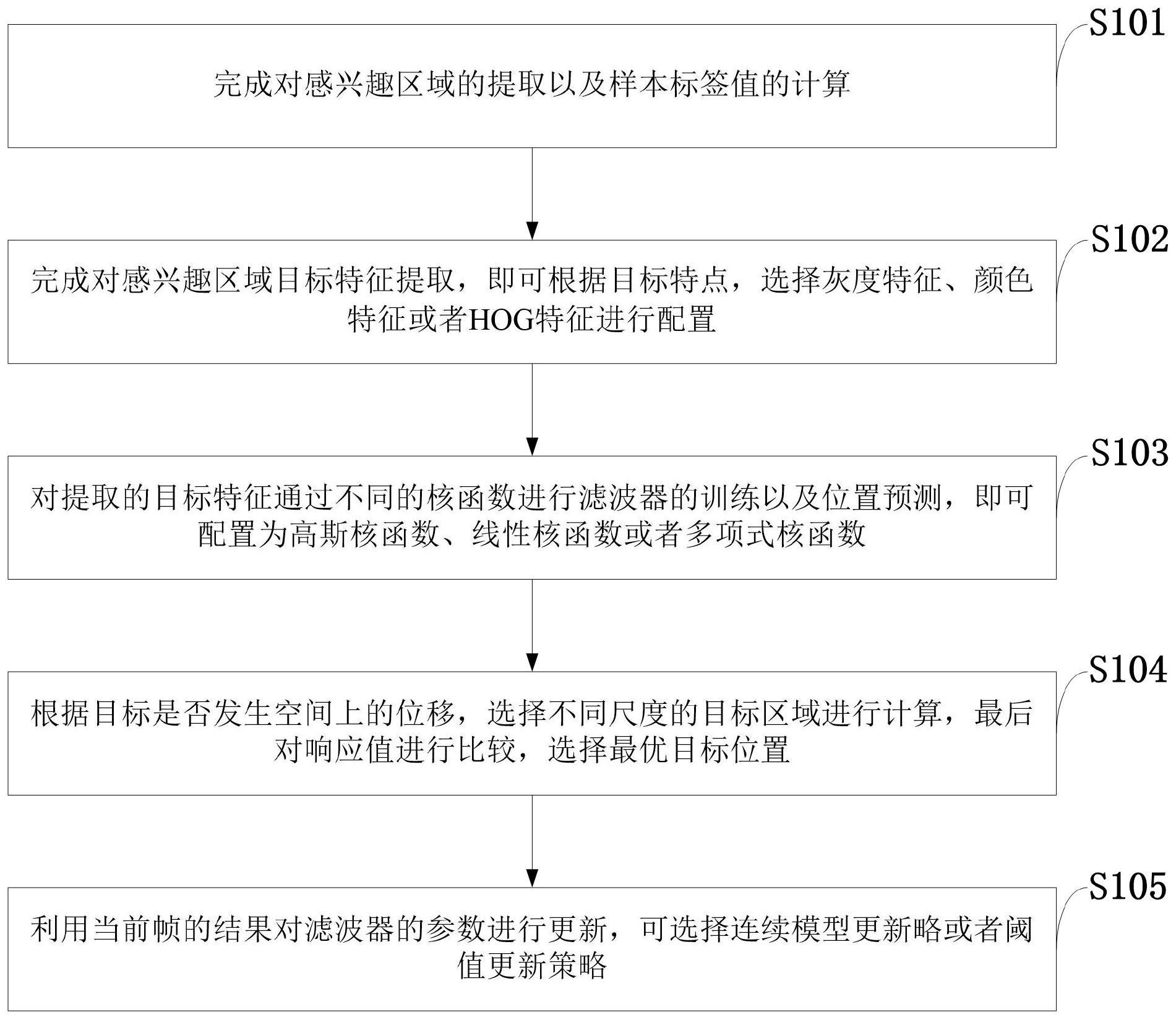

针对现有技术存在的问题,本发明提供了一种配置目标跟踪硬件加速控制方法、 系统、存储介质及应用。 本发明是这样实现的,一种配置目标跟踪硬件加速控制方法,所述配置目标跟踪 硬件加速控制方法包括: 第一步,完成对感兴趣区域的提取以及样本标签值的计算; 第二步,完成对感兴趣区域目标特征提取,根据目标特点,选择灰度特征、颜色特 征或者HOG特征进行配置; 第三步,对提取的目标特征通过不同的核函数进行滤波器的训练以及位置预测, 配置为高斯核函数、线性核函数或者多项式核函数; 第四步,根据目标是否发生空间上的位移,选择不同尺度的目标区域进行计算,对 响应值进行比较,选择最优目标位置; 第五步,利用当前帧的结果对滤波器的参数进行更新,可选择连续模型更新略或 者阈值更新策略。 进一步,所述第一步还包括对输入帧的感兴趣区域进行提取以及对应样本标签值 的计算。感兴趣区域提取电路根据已给出初始帧的位置,使用感兴趣区域选择模块ROI对感 兴趣区域进行提取;对于初始帧将选定的区域在Matlab中进行计算其傅里叶变换 将所 得结果存入二维查找表中。 进一步,所述第二步还包括对选定的图像区域进行特征提取,选择配置为灰度特 征提取、颜色特征提取和HOG特征提取; 在灰度特征提取电路中,将图像区域归一化为0到1之间,并将像素数据分两路计 算,一路使用均值计算模块计算每一帧图像的均值,另外一路利用乒乓FIFO对输入帧进行 缓冲,以达到当前帧与对应均值进行匹配做差,所得结果为灰度特征的表示; 5 CN 111582266 A 说 明 书 2/7 页 在颜色特征提取电路中,将RGB图像转化至HSV颜色空间,在Simulink中,使用乘法 器和加减法器对所有可能结果进行表示,颜色特征提取电路,对于S分量和V分量可直接输 出,而H分量通过选择模块Switch对所有可能结果进行进行级联,根据条件进行选择输出; 在HOG特征提取电路中,利用Simulink中的颜色空间转换模块Color Space Converter将RGB图像转化为灰度图像;利用两个滤波器模块Image Filter,并将其系数设 置为[1,0,-1]和[1,0,-1]T,输出即为x和y方向上的梯度分量;通过乘法器和开方模块Spqt 计算每个像素的梯度幅值,同时利用反正切模块Atan进行梯度角的计算;将所得的梯度幅 值利用行缓冲模块Line Buffer进行缓冲,并使用延时模块Tapped Delay对缓冲数据构成 大小为4x4的邻域,同时将输入的梯度角等分为8个区间,将对应区间的梯度幅值进行累加, 得到1x8维数据并行输出,即为一个cell的梯度直方图,根据上述方法计算出4个cell的直 方图并依次首尾形成一个block,即输出为1x32维的向量;按照将每个block进行归一化得 到最终的HOG特征。 进一步,所述第三步还包括利用提取到的图像特征和核函数计算滤波器的系数以 及位置的预测, 的二维傅里叶变换电路,在初始帧中,对于图像特征x先计算行方向上的 一维傅里叶变换,并将结果缓冲至RAM中,等待第64行的第64个数据计算完成之后,将RAM中 的数据按列进行读出,计算列方向上的一维傅里叶变换,输出为图像特征的二维傅里叶变 换;利用图像特征的二维傅里叶变换 通过选择合适的核函数进行自相关计算,结果记为 选择配置为高斯核函数、线性核函数和多项式核函数;将二维查找表中的样本标签值 与核函数 利用下式进行计算得出滤波器系数 当后续帧z到来时,执行操作得出 根据下式计算响应值,并经过二维傅里叶反 变换后选取最大值作为目标的最终位置: 进一步,所述第四步还包括根据对所跟踪目标进行判断,如果目标发生尺度变化, 设置尺度因子为0.5,1和1.5,利用最近邻插值方法对图像进行缩放处理,以适配所设计的 滤波器,并将其同时送至三路相同的滤波器,并执行第三步的操作。 进一步,所述第五步还包括使用当前帧的计算结果通过配置连续更新策略或者阈 值更新策略对滤波器的参数进行更新,连续更新策略中使用对参数进行更新,表示为: α′t=(1-β)αt-1 βαt x′t=(1-β)xt-1 βxt; 其中,α′t、x′t表示更新后的滤波器系数和目标模板,α′t-1、x′t-1表示上一帧的滤波 器系数和目标模板,αt、xt表示当前帧的滤波器系数和目标模板,β表示学习率,为常数。 阈值更新策略中可计算当前帧计算出的响应值与之前每一帧响应值的均值的比 值,表示为p: 6 CN 111582266 A 说 明 书 3/7 页 其中,fi表示第i帧的响应值大小,t表示帧数。 与设置的阈值0.5进行比较,如果高于阈值,则不进行模型更新,若低于阈值,则更 新当前模型,表示为下式: 其中,α′t、x′t表示更新后的滤波器系数和目标模板,α′t-1、x′t-1表示上一帧的滤波 器系数和目标模板,αt、xt表示当前帧的滤波器系数和目标模板,β表示学习率,为常数。 本发明的另一目的在于提供一种接收用户输入程序存储介质,所存储的计算机程 序使电子设备执行权利要求任意一项所述包括下列步骤: 第一步,完成对感兴趣区域的提取以及样本标签值的计算; 第二步,完成对感兴趣区域目标特征提取,根据目标特点,选择灰度特征、颜色特 征或者HOG特征进行配置; 第三步,对提取的目标特征通过不同的核函数进行滤波器的训练以及位置预测, 配置为高斯核函数、线性核函数或者多项式核函数; 第四步,根据目标是否发生空间上的位移,选择不同尺度的目标区域进行计算,对 响应值进行比较,选择最优目标位置; 第五步,利用当前帧的结果对滤波器的参数进行更新,可选择连续模型更新略或 者阈值更新策略。 本发明的另一目的在于提供一种实施所述配置目标跟踪硬件加速控制方法的配 置目标跟踪硬件加速控制系统,所述配置目标跟踪硬件加速控制系统包括: 初始化模块,用于完成对感兴趣区域的提取以及样本标签值的计算; 特征提取模块,用于完成对感兴趣区域目标特征提取,根据目标特点,选择灰度特 征、颜色特征或者HOG特征进行配置; 滤波器模块,用于对提取的目标特征通过不同的核函数进行滤波器的训练以及位 置预测,配置为高斯核函数、线性核函数或者多项式核函数; 尺度处理模块,用于根据目标是否发生空间上的位移,选择不同尺度的目标区域 进行计算,最后对响应值进行比较,选择最优目标位置; 模型更新模块,用于利用当前帧的结果对滤波器的参数进行更新,可选择连续模 型更新略或者阈值更新策略。 本发明的另一目的在于提供一种硬件加速平台,所述硬件加速平台安装有所述的 配置目标跟踪硬件加速控制系统。 本发明的另一目的在于提供一种图像处理器,所述图像处理器安装有所述的配置 目标跟踪硬件加速控制系统。 7 CN 111582266 A 说 明 书 4/7 页 结合上述的所有技术方案,本发明所具备的优点及积极效果为:本发明可以根据 实际场景的特性,合理配置相关算法模块,即特征提取模块、滤波器模块、尺度处理模块和 模型更新模块,组成一种特定的目标跟踪算法,完成感兴趣目标的追踪;最后使用Simulink 软件自上而下对该硬件加速架构进行设计实现,以达到高效迭代目标跟踪架构并进行实时 跟踪的目的。 本发明提出了基于模型的可配置目标跟踪硬件加速方法。可以根据实际场景的特 点,选择相应模块,合理配置为一种特定的目标跟踪算法,同时对各模块及内部之间并行流 水线设计,能够确保达到实时跟踪的目的。本发明使用Simulink平台对所设计的算法快速 硬件实现,并可以通过代码转换工具直接生成硬件描述语言,以适合在FPGA上进行部署,此 外该设计方法可以快速更新迭代,对于其他计算机视觉算法而言,这种通过Simulink软件 进行模型化设计并部署在FPGA平台的开发方法有较强的参考性。 附图说明 为了更清楚地说明本申请实施例的技术方案,下面将对本申请实施例中所需要使 用的附图做简单的介绍,显而易见地,下面所描述的附图仅仅是本申请的一些实施例,对于 本领域普通技术人员来讲,在不付出创造性劳动的前提下还可以根据这些附图获得其他的 附图。 图1是本发明实施例提供的配置目标跟踪硬件加速控制方法流程图。 图2是本发明实施例提供的配置目标跟踪硬件加速控制系统的结构示意图; 图中:1、初始化模块;2、特征提取模块;3、滤波器模块;4、尺度处理模块;5、模型更 新模块。 图3是本发明实施例提供的基于模型设计的可配置目标跟踪算法框架示意图。 图4是本发明实施例提供的可配置目标跟踪架构预测模型示意图。 图5是本发明实施例提供的感兴趣区域提取电路示意图。 图6是本发明实施例提供的存放样本标签的二维查找表。 图7是本发明实施例提供的灰度特征提取电路示意图。 图8是本发明实施例提供的颜色特征提取电路示意图。 图9是本发明实施例提供的特征矩阵的二维傅里叶变换电路示意图。 图10是本发明实施例提供的三种核函数电路示意图。 图11是本发明实施例提供的滤波器系数计算电路示意图。 图12是本发明实施例提供的尺度处理模块的流程图。 图13是本发明实施例提供的OTB100数据集中的boy的跟踪结果图。