技术摘要:

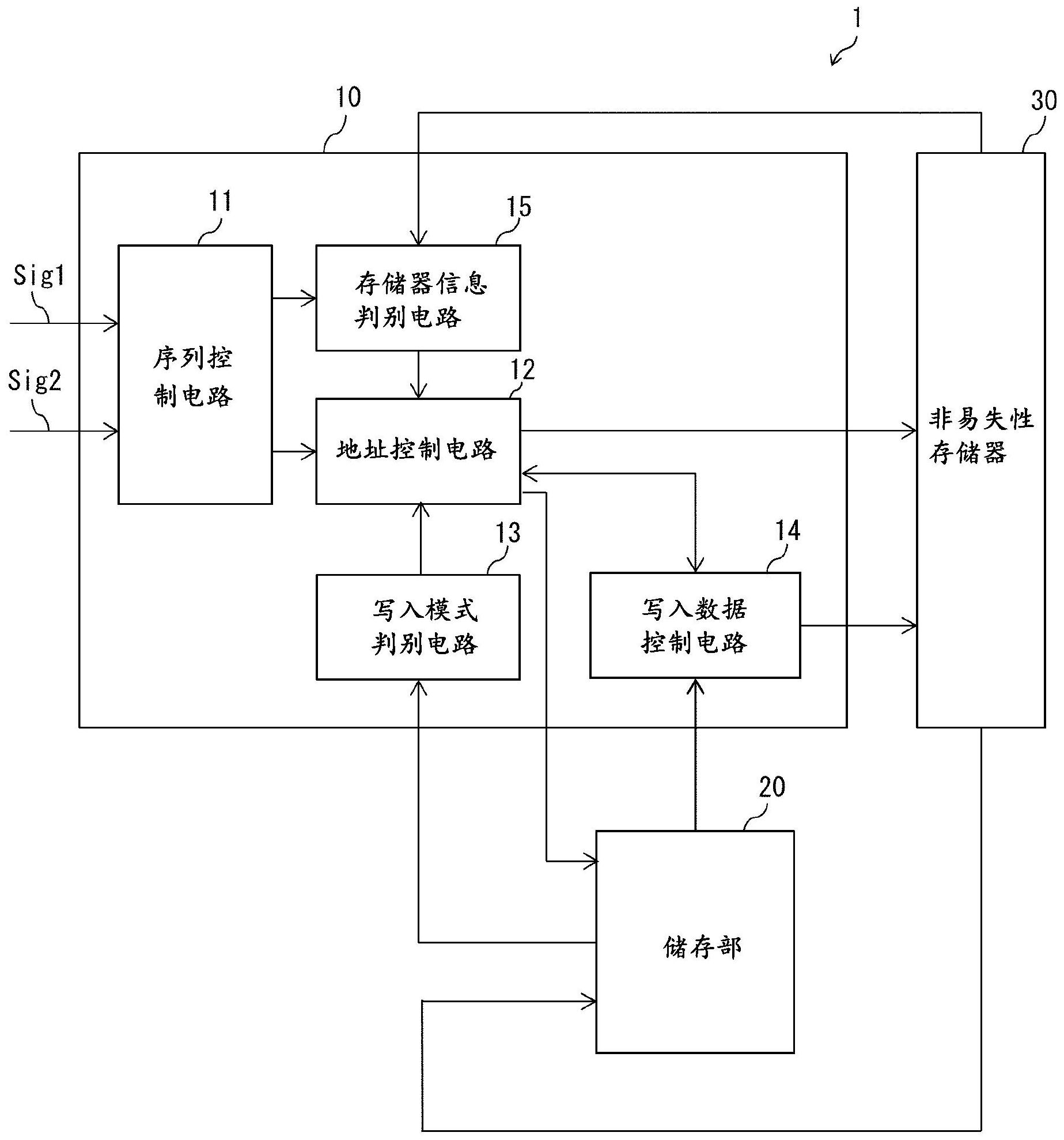

提供一种能够削减参数的写入的处理时间的控制装置及控制方法。控制装置(1)具备储存多个参数的储存部(20)、可改写的非易失性存储器(30)、以及从多个参数之中将写入对象的参数写入非易失性存储器(30)的控制电路(10)。参数包含表示储存部(20)中的储存位置的参数地址、和至 全部

背景技术:

近年来,由于显示装置的高清晰化、使用了有机发光二极管元件(OLED:Organic Light Emitting Diode)等的显示装置的登场,关于显示装置中的图像显示等所使用的参 数的量变多。这里,在与显示装置相关的参数中,具有与面板尺寸及分辨率相关的参数、与 面板的电气特性、驱动定时的设定相关的参数、为了提供高画质的影像而对图像数据实施 的校正处理所使用的校正参数等。 上述的参数存储在内置于显示装置的驱动IC(Integrated Circuit:集成电路)的 非易失性存储器中。在用户进行参数的设定、更新时,进行储存在储存部(寄存器)内的参数 向非易失性存储器的写入。 然而,在近年来的芯片上的非易失性存储器中,即使分割成多组来进行参数的写 入,被允许的写入次数也不是十分多。 因此,在有限的存储器区域中,进行大量的参数的写入成为课题。 因此,例如,提出了一种具备能够储存最大改写次数不同的参数的非易失性存储 器的显示控制装置(参照专利文献1)。在该显示控制装置中,如图6所示,针对每个要求相同 的最大写入次数的参数进行分组。即,对地址A及地址B所属的组2a、和地址C及地址D所属的 组2b进行分组,并将参数储存在储存部2内。 现有技术文献 专利文献 专利文献1:日本特开2015-25837号公报

技术实现要素:

本发明所要解决的技术问题 在上述的显示控制装置中,例如,在地址A的参数需要更新,地址B的参数不需要更 新的情况下,由于针对每组进行参数的写入,因此属于不需要更新的地址B的参数也被写入 非易失性存储器3中。 像这样,在上述的显示控制装置中,存在如下问题:即使是具有包含不需要更新的 参数的情况、保持初始值不变即可的参数,储存部2内的参数也被写入非易失性存储器3中。 另外,写入不需要更新的参数的处理尽管不需要更新也需要从非易失性存储器3向储存部2 读取参数,因此存在处理时间很长这一问题。 本发明是鉴于上述的课题所做出的,目的在于提供能够削减参数的写入的处理时 间的控制装置及控制方法。 解决问题的方案 (1)本发明的一个实施方式为一种控制装置,其具备:储存部,其储存多个参数;可 5 CN 111599397 A 说 明 书 2/9 页 改写的非易失性存储器;以及控制电路,其从上述多个参数之中将写入对象的参数写入上 述非易失性存储器中,上述参数包含表示上述储存部中的储存位置的参数地址、和至少一 个参数数据,在上述参数地址或参数数据中设置0或1的控制位,上述控制电路在上述控制 位为1的情况下写入上述参数。 (2)另外,本发明的某一实施方式为一种控制装置,在上述(1)的结构的基础上,上 述控制电路具有写入数据控制电路和地址控制电路,上述地址控制电路读取写入有上述参 数的上述非易失性存储器中的未储存区域的地址,并指示上述写入数据控制电路读取上述 储存部内的上述参数,上述写入数据控制电路读取储存在上述储存部中的上述参数,在该 读取到的参数的上述控制位为1的情况下,将上述读取到的参数写入上述非易失性存储器 的上述未储存区域的地址中。 (3)另外,本发明的某一实施方式为一种控制装置,在上述(1)的结构的基础上,针 对每个参数地址设置上述控制位,上述控制电路具有写入数据控制电路和地址控制电路, 上述地址控制电路读取写入有上述参数的上述非易失性存储器的未储存区域的地址,并指 示上述写入数据控制电路读取上述储存部内的上述参数地址,上述写入数据控制电路根据 来自上述地址控制电路的指示读取上述储存部内的上述参数地址,在该读取到的参数地址 的上述控制位为1的情况下,将上述读取到的参数地址、上述参数数据、以及上述参数数据 的总数写入上述非易失性存储器的上述未储存区域的地址中。 (4)另外,本发明的某一实施方式为一种控制装置,在上述(1)的结构的基础上,针 对每个参数数据设置上述控制位,上述控制电路具有写入数据控制电路和地址控制电路, 上述地址控制电路读取写入有上述参数的上述非易失性存储器的未储存区域的地址,并指 示上述写入数据控制电路读取上述储存部内的上述参数数据,上述写入数据控制电路根据 来自上述地址控制电路的指示读取上述储存部内的上述参数数据,在该读取到的参数数据 的上述控制位为1的情况下,将上述读取到的参数数据、上述参数地址、以及上述参数数据 的排列顺序写入上述非易失性存储器的上述未储存区域的地址中。 (5)另外,本发明的某一实施方式为一种控制装置,在上述(3)的结构的基础上,上 述地址控制电路经由上述写入数据控制电路而获取上述储存部内的上述参数地址,上述写 入数据控制电路判定上述储存部内的上述参数地址与储存在上述非易失性存储器中的上 述参数地址是否相同,在上述储存部内的上述参数地址与储存在上述非易失性存储器中的 上述参数地址相同的情况下,将储存在上述非易失性存储器中的上述参数地址改写为规定 的数值。 (6)本发明的一个实施方式为一种控制方法,其为控制装置的控制方法,上述控制 装置具有:储存多个参数的储存部;可改写的非易失性存储器;以及从上述多个参数之中将 写入对象的参数写入上述非易失性存储器中的控制电路,上述控制方法包含:地址读取步 骤,其读取写入有包含表示上述储存部中的储存位置的参数地址、和至少一个参数数据的 上述参数的上述非易失性存储器的未储存区域的地址;参数读取步骤,其读取储存在上述 储存部中的上述参数;写入判定步骤,其基于在上述参数地址或参数数据中设置的0或1的 控制位,来判定是否通过上述控制电路将该读取到的上述参数写入上述非易失性存储器的 上述未储存区域的地址中;以及写入步骤,其在上述控制位为1的情况下,通过上述控制电 路将在上述参数读取步骤中读取到的上述参数写入上述非易失性存储器中。 6 CN 111599397 A 说 明 书 3/9 页 (7)另外,本发明的某一实施方式为一种控制方法,其在上述(6)的结构的基础上, 上述控制电路具有写入数据控制电路和地址控制电路,在上述地址读取步骤中,使上述地 址控制电路读取写入有上述参数的上述非易失性存储器的上述未储存区域的地址,在上述 参数读取步骤中,通过上述地址控制电路使上述写入数据控制电路读取上述储存部内的上 述参数,在上述写入判定步骤中,在上述控制位为1的情况下,通过上述写入数据控制电路 将在上述参数读取步骤中读取到的上述参数写入上述非易失性存储器的上述地址中。 (8)另外,本发明的某一实施方式为一种控制方法,其在上述(6)的结构的基础上, 针对每个上述参数地址设置上述控制位,上述控制电路具有写入数据控制电路和地址控制 电路,在上述地址读取步骤中,使上述地址控制电路读取写入有上述参数的上述非易失性 存储器的上述未储存区域的地址,在上述参数读取步骤中,通过上述地址控制电路使上述 写入数据控制电路读取上述储存部内的上述参数地址,在上述写入判定步骤中,在上述控 制位为1的情况下,判定是否将在上述参数读取步骤中读取到的上述参数地址写入上述非 易失性存储器的上述地址中,在上述写入步骤中,将上述读取到的参数地址、上述参数数 据、以及上述参数数据的总数写入上述非易失性存储器的上述地址中。 (9)另外,本发明的某一实施方式为一种控制方法,其在上述(6)的结构的基础上, 针对每个上述参数数据设置上述控制位,上述控制电路具有写入数据控制电路和地址控制 电路,在上述地址读取步骤中,使上述地址控制电路读取写入有上述参数的上述非易失性 存储器的上述未储存区域的地址,在上述参数读取步骤中,通过上述地址控制电路使上述 写入数据控制电路读取上述储存部内的上述参数数据,在上述写入判定步骤中,在上述控 制位为1的情况下,将在上述参数读取步骤中读取到的上述参数数据写入上述非易失性存 储器的上述未储存区域的地址中,在上述写入步骤中,将上述读取到的参数数据、上述参数 地址、以及上述参数数据的排列顺序写入上述非易失性存储器的上述地址中。 (10)另外,本发明的某一实施方式为一种控制方法,其在上述(8)的结构的基础 上,包含:参数地址读取步骤,其读取被写入上述非易失性存储器内的上述参数地址;覆写 判定步骤,其判定储存在上述储存部中的上述参数地址与储存在上述非易失性存储器中的 上述参数地址是否相同;以及覆写步骤,其在上述覆写判定步骤中,在判定为上述储存部内 的上述参数地址与上述非易失性存储器内的上述参数地址相同的情况下,将上述非易失性 存储器内的上述参数地址改写为规定的数值。 发明效果 根据本发明的一个方式的控制装置及控制方法,能够削减参数的写入的处理时 间。 附图说明 图1是说明与本发明的第一实施方式所涉及的控制装置相关的框图。 图2是表示本发明的第一实施方式所涉及的参数的写入方法的图。 图3是表示本发明的第一实施方式所涉及的参数的写入处理的流程的流程图。 图4是表示本发明的第二实施方式所涉及的参数的写入方法的图。 图5是本发明的第三实施方式所涉及的参数的覆写处理的流程的流程图。 图6是表示现有的控制装置所涉及的参数的写入方法的参考图。 7 CN 111599397 A 说 明 书 4/9 页