技术摘要:

本发明公开一种电阻式随机存取存储器及其制造方法,其中该电阻式随机存取存储器包括堆叠结构、至少一垂直电极、选择元件以及多个可变电阻结构。堆叠结构是由交替堆叠的多个水平电极与多个第一介电层所组成,其中堆叠结构具有至少一孔道贯穿水平电极与第一介电层。垂直 全部

背景技术:

由于电阻式随机存取存储器(resistive random access memory,RRAM)具备优越 的可扩缩性(scalability)、易操作性、低耗能以及较简单的制作工艺,所以已成为目前最 具前景的非挥发性存储器技术之一。 如图1所示,现今电阻式随机存取存储器100的构成多具有垂直电极102、可变电阻 层104、水平电极106、位线108以及由MOS构成的字符线110等。可变电阻层104形成于垂直电 极102与水平电极106之间,且每个垂直电极102连接位线108,以进行电荷的判读,并通过字 符线110控制电阻式随机存取存储器100的开或关。 由于电阻式随机存取存储器需要设置如MOS的选择元件,来控制电流的流路,以避 免电阻式随机存取存储器由于潜泄电流(sneak current)所造成的读取错误,因此其体积 由于元件设计的关系无法进一步缩减,而对于电阻式随机存取存储器的集成度造成限制。

技术实现要素:

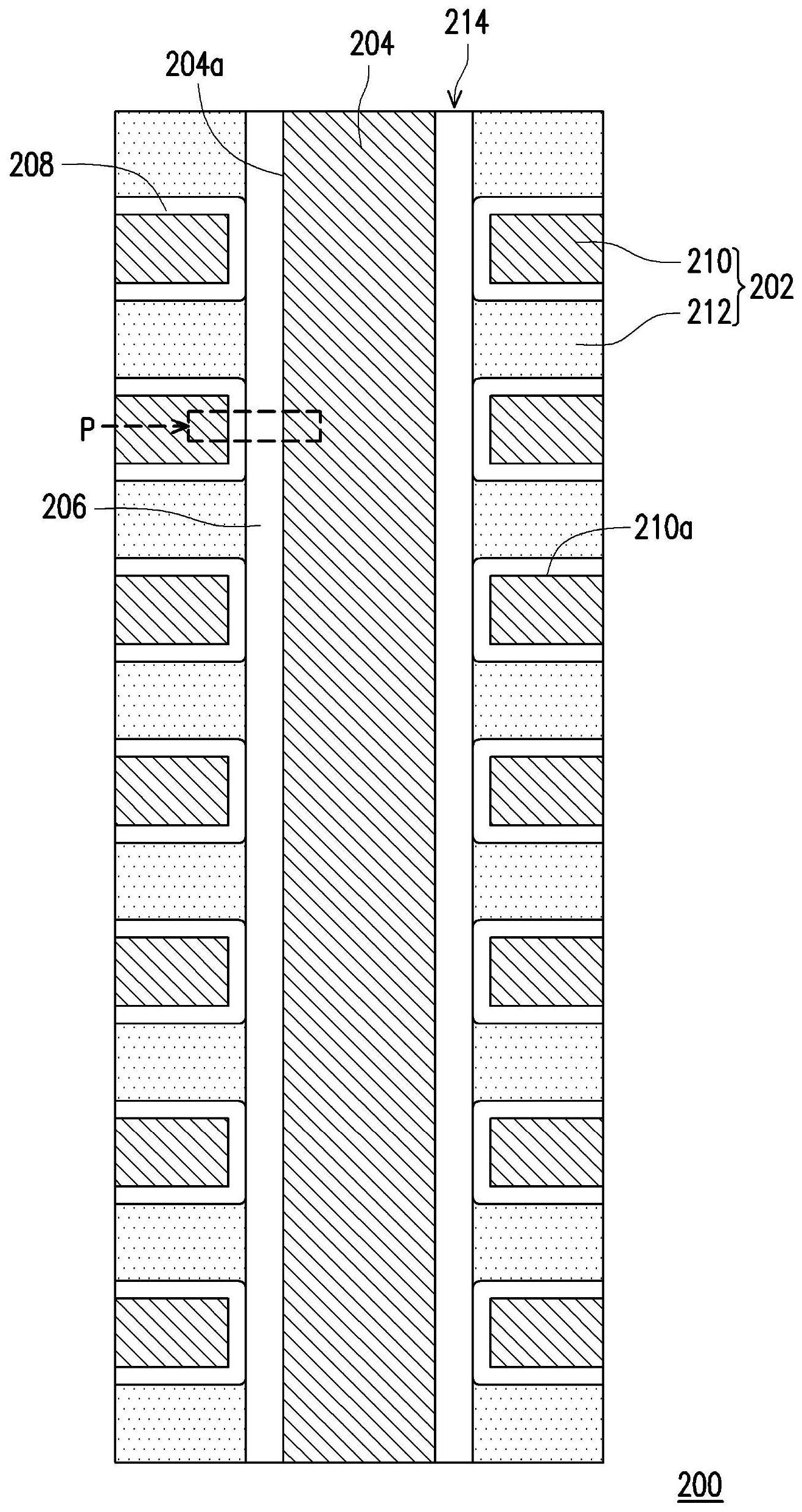

本发明提供一种电阻式随机存取存储器,其可有效提升电阻式随机存取存储器的 集成度,进而提升元件的性能。 本发明另提供一种电阻式随机存取存储器的制造方法,能整合于现有制作工艺并 制作出高集成度的电阻式随机存取存储器。 本发明的电阻式随机存取存储器包括堆叠结构、至少一垂直电极、选择元件以及 多个可变电阻结构。堆叠结构是由交替堆叠的多个水平电极与多个第一介电层所组成,其 中堆叠结构具有至少一孔道贯穿水平电极与第一介电层。垂直电极形成于至少一孔道内。 选择元件(selector element)形成于垂直电极与堆叠结构之间的孔道内。可变电阻结构设 置于每个水平电极的表面并与孔道内的选择元件接触。 在本发明的一实施例中,上述可变电阻结构包括存储层、介于存储层与选择元件 之间的氧化层以及介于存储层与水平电极的表面之间的阻障层。 在本发明的一实施例中,上述选择元件包括:过渡金属氧化物(Transition Metal Oxide,TMO)选择元件、双向阈值开关(Ovonic Threshold Switching,OTS)选择元件、金属/ 硅/金属(metal/silicon/metal,MSM)选择元件或混合离子与电子导体(Mixed Ionic Electronic Conduction,MIEC)二极管。 在本发明的一实施例中,上述选择元件包括与垂直电极接触的栅极层、与氧化层 接触的通道层以及介于通道层与栅极层之间的栅极绝缘层。 在本发明的一实施例中,上述选择元件还可包括第一导电态掺杂区以及第一导电 态外延层。第一导电态掺杂区形成于孔道的第一端的通道层内,其中通道层为第二导电态。 4 CN 111584495 A 说 明 书 2/6 页 第一导电态外延层形成于孔道的第二端,第一导电态外延层与通道层接触并与栅极层通过 栅极绝缘层隔绝,其中栅极层为第二导电态。 在本发明的一实施例中,上述第一导电态为N型,第二导电态为P型。 在本发明的一实施例中,上述第一导电态为P型,第二导电态为N型。 本发明的电阻式随机存取存储器的制造方法,包括以下步骤。形成堆叠结构,其由 交替堆叠的多个第一介电层与多个第二介电层所组成,其中第一介电层与第二介电层具有 不同的蚀刻速率。在堆叠结构中形成至少一孔道,孔道贯穿多个第一介电层与多个第二介 电层。在孔道的内面共形地形成选择元件。在孔道内形成垂直电极。移除堆叠结构内的所有 第二介电层,并露出部分选择元件。在堆叠结构内的多个第一介电层的表面和选择元件的 暴露表面共形地形成多个可变电阻结构,其与孔道内的选择元件接触。在多个第一介电层 之间形成多个水平电极。 在本发明的另一实施例中,形成上述可变电阻结构的步骤包括在第一介电层的表 面和选择元件的暴露表面依序形成氧化层、存储层以及阻障层。 在本发明的另一实施例中,上述选择元件包括:过渡金属氧化物(TMO)选择元件、 双向阈值开关(OTS)选择元件、金属/硅/金属(MSM)选择元件或混合离子与电子导体(MIEC) 二极管。 在本发明的另一实施例中,形成上述选择元件的步骤包括:在至少一孔道的内面 依序形成通道层、栅极绝缘层以及栅极层。 在本发明的另一实施例中,上述形成选择元件的步骤还可包括在形成通道层之 前,在孔道的第一端形成第一导电态外延层,并在形成通道层之后,对孔道的第二端的通道 层进行掺杂,以形成第一导电态掺杂区,其中通道层为第二导电态。 在本发明的另一实施例中,上述第一导电态为N型,第二导电态为P型。 在本发明的另一实施例中,上述第一导电态为P型,第二导电态为N型。 在本发明的另一实施例中,上述孔道若为多个孔道,则在形成垂直电极之后,更包 括移除两两孔道之间的堆叠结构,并保留孔道周围预定形成多个水平电极的部位的堆叠结 构。 基于上述,本发明在电阻式随机存取存储器的垂直电极与堆叠结构之间的孔道内 形成选择元件,并使可变电阻结构形成于每个水平电极的表面。如此一来,相较于已知的电 阻式随机存取存储器,通过本发明的设计与制作工艺可有效降低电阻式随机存取存储器所 需的体积,进而提升存储器元件的集成度。 为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附的附 图作详细说明如下。 附图说明 图1是现有的一种电阻式随机存取存储器的示意图; 图2是本发明的第一实施例的一种电阻式随机存取存储器的剖面示意图; 图3是图2的P部分的放大示意图; 图4是本发明的第二实施例的一种电阻式随机存取存储器的剖面示意图; 图5A、图5B与图5C分别是图4的P1部分、P2部分与P3部分的放大示意图; 5 CN 111584495 A 说 明 书 3/6 页 图6A至图6F是本发明的第二实施例的一种电阻式随机存取存储器的制造流程剖 面示意图; 图7是本发明的第二实施例的一种电阻式随机存取存储器的立体示意图。 符号说明 100、200、400、700:电阻式随机存取存储器 102、204、626:垂直电极 104、208、628:可变电阻结构 106、210、636:水平电极 108:位线 110:字符线 202、602:堆叠结构 204a、210a、600a、604a、612a、614a、624a:表面 206、406、624:选择元件 212、604:第一介电层 214、608:孔道 300、630:氧化层 302、632:存储层 304、634:阻障层 401、600:基底 410、622:栅极层 412、620:栅极绝缘层 414、614:通道层 416、618:第一导电态掺杂区 418、612:第一导电态外延层 420、610:第一端 422、616:第二端 606:第二介电层 608a:内面 702:绝缘材料 P、P1、P2、P3:部分