技术摘要:

一种由MOS管组成的MOS管输出编辑传输型多进制及十进制位权加法器,由不同形式的多值加法模块组成,所述的多值加法模块有输出本位等于0模块、等于1模块、等于2模块……等于N模块,所述的模块是由不同方式连接的运算单元组合连接构成,所述的单元用专利申请201711119713. 全部

背景技术:

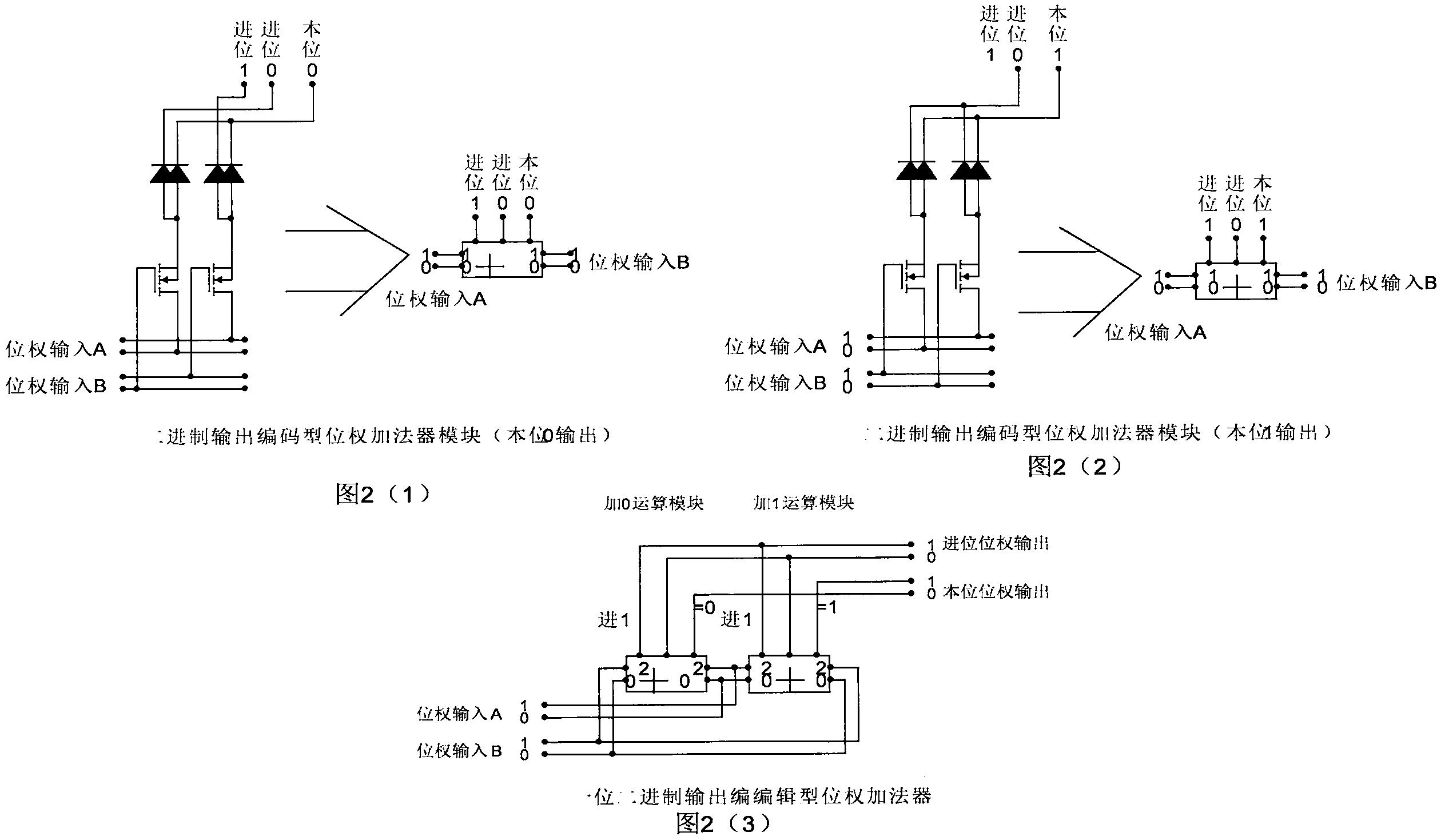

“量化逻辑”是用模拟信息量化后产生的标记信息做为算子进行逻辑运算,演绎, 判断的逻辑系统 量化逻辑的简单理解 把连续、模糊、混沌信息量化后的标记值做为输入输出进行逻辑运算的方法就叫 做量化逻辑,实现其运算的电路就叫做量化逻辑电路,于是量化逻辑电路的输入前置部分 大多数是量化器或被量化了的权值线。后置输出部分为量化权值线或量化幅权线。 量化逻辑运用了二值逻辑和多值逻辑乃至模糊逻辑的基本思想,并且用简单有效 的具有二值取向电路实现了多值及其模糊逻辑的关键电路,使得在逻辑原件只限于简单两 种状态的情况下,同样组成多值及其模糊的逻辑运算电路,特别是量化逻辑的兼容性运算 和量化寄存的方法从根本上解决了多值运算、寄存的难题,从而开辟了新一代计算设备的 更新坦途。量化逻辑繁华多样的运算方法对人工智能的发展可提供有效的硬件支撑。 自然信息是模拟连续变化的,思维只能对稳定形象和固定属性的事物信息产生认 知,不进行定形固化的信息是不能被认知的,于是对模拟连续变化的信息进行定形固化的 处理方法将是思维运作的优先的基本方法,由于现有的知识把对信息的这类处理方式叫做 量化,于是我们把“量化”产生的信息的逻辑关系称为“量化逻辑”。 量化就是模数转换的一种处理信息的方法,有定点、采样值、归并三个步骤。 量化也是思维处理信息的一种方法,亦有三个步骤,划界,标记、混叠 量化亦是自然事物集散属性的一种表现,任何事物总是以有别于其他事物的特征 显现自身的属性,不同属性的确定事物的交接处生成边界,不同属性的表现形成特征,相近 属性的延展混为一体。 于是我们定义:利用事物的异样属性和思维的比较特征分析和辩解事物的方法就 叫做量化。用量化思维对现实事物信息的操作方法和运算规则就叫做量化逻辑。 量化的主要操作方法是:多元量化,多值量化,多重量化 量化的基本规则是对自然百态信息属性的简单离散化,最小稳定化,规整有序化, 4 CN 111610951 A 说 明 书 2/12 页 定点清晰化,形成含义浅显的具有囊括属性的标记过程。 量化逻辑把信息定义成模拟信息,数字信息。数字信息又定义为“幅权信息”和“位 权信息”。幅权信息是时变幅度权重信息,位权信息是空间分布位置的权重信息。 其中模拟信息在量化逻辑中的定义: 模拟信息由两部分组成,一是表现信息,它是连续时刻的幅度权值信息。二是隐含 信息,它是“有”“无”状态信息,“有”是表示有信息但不管幅值大小,“无”表示没信息,没信 息表示没有信息作用在该系统上。 数字信息在量化逻辑中的定义:数字信息在量化逻辑中是指以做了适度量化的信 息。 幅权信息在量化逻辑中的定义: 幅权信息也是由两部分组成,一是表现信息,幅权表现信息是把模拟信息用量化 归并的方法把其幅值阶梯化了的信息,归并后的有序梯阶组成以进位制为限的多值数字序 列,序列中各元素的值便是幅权值,幅权值是表现信息。幅权信息中的隐含信息是二态单值 信息,是“有”“无”状态信息,“有”是表示有信息但不管幅权值大小,“无”表示没信息,没信 息表示没有信息作用在该系统上。实质上幅权信息就是“含态权值”信息。 位权信息在量化逻辑中的定义: 位权信息也是由两部分组成,一是表现信息,它是在位权输出线组中唯一有电平 输出的端子,其输出及信息具有互不相容属性。二是隐含信息,它是由有电平输出线在多个 位权输出线中的空间位置所确定的权重信息。位权信息虽然是两种状态信息但由于使用 “有”“无”两种状态,而“无”状态表示没有连接(和开关的断开是一样的属性)故而是二态单 值逻辑信息。另外无和零值是不同的,无是不存在,对连接在该点上的事物没有作用,零是 存在的,对连接在该点上的事物产生零的作用。这也就是零作用和无作用的区别。实质上位 权信息就是“含权态值”信息。 简单的说:在量化逻辑中,模拟信息,幅权信息,位权信息都内含有两种信息,即表 现信息和隐含信息,一种是“权”信息,一种是“态”信息。“态”信息具逻辑属性,“权”信息具 量度属性。在量化逻辑中,态运算和权运算是分离的,态运算是逻辑运算,权运算依照需求 进行赋意分形的数值运算,亦可做为多值逻辑运算。权运算在做为逻辑运算时具有和传统 逻辑不同的运算关系,如:异值与,同值与,异值或,同值或等,并且逻辑运算关系在电路实 施上有幅权逻辑运算电路和位权逻辑运算电路两种结构。传统二值“与”逻辑是退化了的同 值与逻辑,二值“或”逻辑是退化了的同值或逻辑。 在量化逻辑中用“最小取向”法则所获得的信息是“态”值信息。“逻辑运算”只是 “最小取向运算”,是“态”值运算,于是只有“与”“或”逻辑运算,其它的运算如:取大,取小, 求补,加,减,乘,除,比较等等均是“权值”运算,“态”值逻辑运算判断运算条件的完备性,权 值“量度”运算确定多种规则运算的操作值。 量化逻辑以“量化”为手段直接获取所需信息,并且所获得的信息通过量化器直接 转变为“幅权”或“位权”数字信息,“幅权”或“位权”数字信息便于运算和储存,幅权信息有 利于传输交流,位权信息有利于运算记录。量化器承担信息的转换。 在量化逻辑的中,传统二值逻辑信息是“二权值幅权信息”。量化逻辑和传统逻辑 互相兼容。量化逻辑和传统逻辑的最大不同是把逻辑状态信息和信息权值信息分解开来, 5 CN 111610951 A 说 明 书 3/12 页 逻辑状态信息和传统逻辑信息基本相同,信息权值可以突破二值限制实现多值化运算。同 时可以突破多值运算需要多值逻辑支持的限制,原则上可以实现任意进位制的数值运算及 多值逻辑运算。所有的二值逻辑电路均可运行量化逻辑信息,一般情况下需在二值电路的 输入上连接下拉电阻,已消除二值信息中多余的一个逻辑值,在输出方面亦采用与开关性 状相同的单值器件以阻止多余的一个逻辑值输出。 实现量化运算的关键电路是量化器,量化器有幅权量化器和位权量化器,位权量 化器是把时间信息转化为空间信息的“时-空”变换器件,幅权量化器是把空间信息转化为 时间信息的“空-时”变换器件。空间信息特征是区域分布控制信息,时间信息特征是实时随 机变化信息。 “位权”信息和“幅权”信息在电路实施上的差异是,“位权”信息的优势是:逻辑电 压需求简单,逻辑摆幅可以做的很小,于是器件参数要求不高,功耗可以做的很低,其关键 是状态明晰,速度快,出错率极低。但器件耗用量大,空置资源很多,占用空间资源较大。“幅 权”信息的优势是:器件耗用量小,空置资源少,占用空间资源少,其关键是单端多值特性, 信息蕴含量很高,但对器件参数要求较高,器件工作电压较高,功耗较大。 从量化逻辑的基本特征可见,量化逻辑和传统二值逻辑相比具有如下不同: 1:传统二值逻辑是一种“逻辑态”和“信息权”整合型逻辑,没有态和权这一说法。 量化逻辑把“逻辑态”和“信息权”的分离,使得态值运算和权值运算各自独立,实现了用现 有逻辑硬件进行数字化的多值运算。 2:传统二值逻辑没有“幅权”和“位权”定义 量化逻辑则把数字信息分为“幅权信息”和“位权信息”,并用“量化器”进行转换。 3:传统观点认为模拟信息就是时间连续信息,是自然获得的未经处理的原始信 息。 量化逻辑认为模拟信息是连续的“幅权信息”,“幅权信息”内含幅值权重信息和态 值逻辑信息,逻辑态值信息和幅值权重信息可以分离。 4:传统观点认为“开关”是二值元件,开和关分别表示两个逻辑值。 量化逻辑认为“开关”是二态单值逻辑器件,因为开关的“开与关”其实质内容是 “连接”与“断开”,“连接”可作为一个逻辑值,但“断开”只能是一种状态而不是一个逻辑值。 一种与系统毫无关联的状态不能做为逻辑值。 5:量化逻辑的基本思想和传统的二值逻辑思想并无冲突,因为传统的二值逻辑是 量化逻辑中的一种,是“二值幅权”逻辑。 在量化逻辑中,运行信息有两种类型,幅权信息和位权信息,幅权信息和传统二值 信息相似,但其取值范围不限于二值特征而趋于多值,很显然由于幅权信息的特征,在二值 状态下是最佳的运行方案,如果选值过多势必导致信息幅度稳定空间变小,易受外部侵扰, 加之器件内部运行环境的的影响,使得电路运行可靠性不能保障。故此,在量化逻辑中,数 值运算的实现是依托信息的变换;信息的输入是模拟或幅权信息,通过位权量化器转换为 位权信息,用位权信息实现各种数值运算和逻辑运算,输出的位权信息通过幅权量化器转 换为幅权信息输出。选择用位权信息进行数值运算和逻辑运算的理由是:位权信息是“含权 态值”信息,“含权态值”信息本身“态值”是表现信息,就是电路实际运行的信息,并且态值 信息,其表现特征和传统的二值信息极为相似,因此所有的数值运算实质上进行的是和二 6 CN 111610951 A 说 明 书 4/12 页 值逻辑运算相似运算,于是在电路架构设计及实施上占据有成熟的技术和可靠的运行环 境,只要构建完整的电路架构可立即投入生产和运行。 另一方面“量化逻辑”从理论上解决了多值逻辑和二值逻辑的兼容性问题,清除了 计算机进位制之间的壁垒,从电路设计上打破了各进位制之间电路结构互不通用的障碍, 使得计算机设计在进位制选择上随心所欲,喜欢什么进位制的计算机,便可以设计什么进 位制的计算机,从二进制到十进制以及更多的进位制,共同拥有相同的原理,相同的基本电 路,相同的架构,能够达到和超越当前二值计算机的诸多运算效果。不同进位制的选择纯粹 转变为人们的喜好和现实应用的需求,不会受制于逻辑理论和电路性状的限制。“量化逻 辑”电路使各进位制的电路互相融合,在一个电路系统中可以有不同进位制的电路共存,使 用不同进位制电路的优点,回避各进位制电路的缺点,使得组合电路系统更为理想。“量化 逻辑”电路完美的解决了计算机输入输出信息的唯二值选项,拓宽了计算机输入输出信息 类型的限制,使其直接用自然模拟信息输入,能够有效地融合在自然信息体系里边,和自然 信息形成互动,以促成对自然信息的解析、表达,使计算机本身提升为更高级的设备。随着 所选进位制多少,电路规模会产生较大变化,二进制电路最简单,资源利用率最高,十进制 电路规模最大,资源利用率最低。量化逻辑电路在多进制状况下特别是十进制电路应用时, 结构比较复杂,但我相信在超大规模集成电路技术的支持下,通过不断地努力可以实现性 能超于二值计算设备的机器。 MOS管输出编辑传输型多进制及十进制位权加法器是一种用于加法运算的前级电 路,可以实现一位加法数字运算,采用多个一位加法运算电路组合,可以实现多位数加法的 直接运算,是多进制运算器的核心运算电路。 一种由MOS管组成的一位多值数字加法器“MOS管输出编辑传输型多进制及十进制 位权加法器”,由不同形式的多值加法模块组成,所述的多值加法模块有输出本位等于0模 块、等于1模块、等于2模块……等于N模块,所述的模块是由不同方式连接的运算单元组合 连接构成,所述的单元用专利申请201711119713.x“量化逻辑之多进制算术运算器赋意分 形集成单元电路”的权利要求3所述电路做为单元排列组合而成;把各单元根据进位制的选 择、和两输入加数相加后,其“和”值的个位相同的单元排列在一起,组成不同规模的运算模 块,模块中各单元的栅极组成一组位权数据的输入,模块中各单元的漏极组成一组位权数 据的输入,把单元中各分形输出进位1输出连接在一起作为模块进位输出,把单元中进位等 于0的输出连接到一起组成模块进位0输出,把各单元本位输出连接到一起组成模块的本位 输出;不管选择什么进位制,模块输出只有三路;所述的模块输入依据所选电路的进位制不 同亦不相同,二进制加法器各有两路两条线输入,三进制加法器各有两路三条线输入,四进 制加法器各有两路四条线输入,五进制加法器各有两路五条线输入,六进制加法器各有两 路六条线输入,七进制加法器各有两路七条线输入,八进制加法器各有两路八条线输入,九 进制加法器各有两路九条线输入,十进制加法器各有两路十条线输入….;所述的MOS管的 栅极和漏极按照加法规则和分形二极管的本位输出相同的要求,依照加法表进行编辑并连 接;所述的二进制加法器共用两个模块,等于0模块,等于1模块;所述的三进制加法器共用 三个加法模块,等于0模块,等于1模块,等于2模块;所述的四进制加法器共用四个加法模 块,等于0模块,等于1模块,等于2模块,等于3模块;所述的五进制加法器共用五个加法模 块,等于0模块,等于1模块,等于2模块,等于3模块,等于4模块;所述的六进制加法器共用六 7 CN 111610951 A 说 明 书 5/12 页 个加法模块,等于0模块,等于1模块,等于2模块,等于3模块,等于4 模块,等于5模块;所述 的七进制加法器共用七个加法模块,等于0模块,等于1模块,等于2模块,等于3模块,等于4 模块,等于5模块,等于6模块;所述的八进制加法器共用八个加法模块,等于0模块,等于1模 块,等于2模块,等于3模块,等于4模块,等于5 模块,等于6模块,等于7模块;所述的九进制 加法器共用九个加法模块,等于0模块,等于1模块,等于2模块,等于3模块,等于4模块,等于 5模块,等于6模块,等于7模块,等于8模块;所述的十进制加法器共用十个加法模块,等于0 模块,等于1模块,等于2 模块,等于3模块,等于4模块,等于5模块,等于6模块,等于7模块, 等于8模块,等于9模块;随着进位制升高模块数依次变多。 所述的模块是由不同方式连接的加法运算单元组合连接构成,所述的单元用专利 申请 201711119713.x“量化逻辑之多进制算术运算器赋意分形集成单元电路”的权利要求 3所述电路做为单元排列组合而成;所述的单元是把两路加数相加所得的“和”的个位相等 的单元组合在一起,并把本位输出连接到一起,本位输出是各单元加法运算“和”的个位相 等的数,进位输出对应于进位0和进位1线进行连接;所述的各单元的栅极作为一路加数的 位权输入,各单元的漏极作为另一路加数的输入,所述的各输入的连接方法是按照输出的 “和”的加法关系把对应的两路输入连接到位权输入端子上。 所述的模块由专利申请201711119713.x“量化逻辑之多进制算术运算器赋意分形 集成单元电路”权利要求3所述电路做为单元排列组合而成;所述的模块所使用的单元数目 由进位制的选择确定,二进制加法器使用两个加法单元,三进制加法器使用三个加法单元, 四进制加法器使用四个加法单元,五进制加法器使用五个加法单元,六进制加法器使用六 个加法单元,七进制加法器使用七个加法单元,八进制加法器使用八个加法单元,九进制加 法器使用九个加法单元,十进制加法器使用十个加法单元,N进制加法器使用N个加法单元。 把MOS管组成的一位多值数字加法器“MOS管输出编辑传输型多进制及十进制位权 加法器”依照专利申请201710024248.5“多进制算数运算器”的权利要求1所述的方式组成 的多位多进制全加器;所述的多位二进制全加器由多个一位二进制加法器按照专利申请 201710024248.5“多进制算数运算器”的权利要求1所述的方式组成;所述的多位三进制全 加器由多个一位三进制加法器按照专利申请201710024248.5“多进制算数运算器”的权利 要求1所述的方式组成;所述的多位四进制全加器由多个一位四进制加法器按照专利申请 201710024248.5“多进制算数运算器”的权利要求1所述的方式组成;所述的多位五进制全 加器由多个一位五进制加法器按照专利申请201710024248.5“多进制算数运算器”的权利 要求1所述的方式组成;所述的多位六进制全加器由多个一位六进制加法器按照专利申请 201710024248.5“多进制算数运算器”的权利要求1所述的方式组成;所述的多位七进制全 加器由多个一位七进制加法器按照专利申请201710024248.5“多进制算数运算器”的权利 要求1所述的方式组成;所述的多位八进制全加器由多个一位八进制加法器按照专利申请 201710024248.5“多进制算数运算器”的权利要求1所述的方式组成;所述的多位九进制全 加器由多个一位九进制加法器按照专利申请201710024248.5“多进制算数运算器”的权利 要求1所述的方式组成;所述的多位十进制全加器由多个一位十进制加法器按照专利申请 201710024248.5“多进制算数运算器”的权利要求1所述的方式组成;所述的多位N进制全加 器由多个一位N进制加法器按照专利申请201710024248.5“多进制算数运算器”的权利要求 1所述的方式组成。 8 CN 111610951 A 说 明 书 6/12 页 附图说明 图1(1)是二进制加法表 图1(2)是三进制加法表 图1(3)是四进制加法表 图1(4)是五进制加法表 图1(5)是六进制加法表 图1(6)是七进制加法表 图1(7)是八进制加法表 图1(8)是九进制加法表 图1(9)是十进制加法表 图2(1)是二进制MOS管输出编辑型位权加法器本位输出等于0模块电路 图2(2)是二进制MOS管输出编辑型位权加法器本位输出等于1模块电路 图2(3)是一位二进制MOS管输出编辑型位权加法器模块组合主控运算电路 图3(1)是三进制MOS管输出编辑型位权加法器本位输出等于0模块电路 图3(2)是三进制MOS管输出编辑型位权加法器本位输出等于1模块电路 图3(3)是三进制MOS管输出编辑型位权加法器本位输出等于2模块电路 图3(4)是一位三进制MOS管输出编辑型位权加法器模块组合主控运算电路 图4(1)是四进制MOS管输出编辑型位权加法器本位输出等于0模块电路 图4(2)是四进制MOS管输出编辑型位权加法器本位输出等于1模块电路 图4(3)是四进制MOS管输出编辑型位权加法器本位输出等于2模块电路 图4(4)是四进制MOS管输出编辑型位权加法器本位输出等于3模块电路 图4(5)是一位四进制MOS管输出编辑型位权加法器模块组合主控运算电路 图5(1)是五进制MOS管输出编辑型位权加法器本位输出等于0模块电路 图5(2)是五进制MOS管输出编辑型位权加法器本位输出等于1模块电路 图5(3)是五进制MOS管输出编辑型位权加法器本位输出等于2模块电路 图5(4)是五进制MOS管输出编辑型位权加法器本位输出等于3模块电路 图5(5)是五进制MOS管输出编辑型位权加法器本位输出等于4模块电路 图5(6)是一位五进制MOS管输出编辑型位权加法器模块组合主控运算电路 图6(1)是六进制MOS管输出编辑型位权加法器本位输出等于0模块电路 图6(2)是六进制MOS管输出编辑型位权加法器本位输出等于1模块电路 图6(3)是六进制MOS管输出编辑型位权加法器本位输出等于2模块电路 图6(4)是六进制MOS管输出编辑型位权加法器本位输出等于3模块电路 图6(5)是六进制MOS管输出编辑型位权加法器本位输出等于4模块电路 图6(6)是六进制MOS管输出编辑型位权加法器本位输出等于5模块电路 图6(7)是一位六进制MOS管输出编辑型位权加法器模块组合主控运算电路 图7(1)是七进制MOS管输出编辑型位权加法器本位输出等于0模块电路 图7(2)是七进制MOS管输出编辑型位权加法器本位输出等于1模块电路 图7(3)是七进制MOS管输出编辑型位权加法器本位输出等于2模块电路 图7(4)是七进制MOS管输出编辑型位权加法器本位输出等于3模块电路 9 CN 111610951 A 说 明 书 7/12 页 图7(5)是七进制MOS管输出编辑型位权加法器本位输出等于4模块电路 图7(6)是七进制MOS管输出编辑型位权加法器本位输出等于5模块电路 图7(7)是七进制MOS管输出编辑型位权加法器本位输出等于6模块电路 图7(8)是一位七进制MOS管输出编辑型位权加法器模块组合主控运算电路 图8(1)是八进制MOS管输出编辑型位权加法器本位输出等于0模块电路 图8(2)是八进制MOS管输出编辑型位权加法器本位输出等于1模块电路 图8(3)是八进制MOS管输出编辑型位权加法器本位输出等于2模块电路 图8(4)是八进制MOS管输出编辑型位权加法器本位输出等于3模块电路 图8(5)是八进制MOS管输出编辑型位权加法器本位输出等于4模块电路 图8(6)是八进制MOS管输出编辑型位权加法器本位输出等于5模块电路 图8(7)是八进制MOS管输出编辑型位权加法器本位输出等于6模块电路 图8(8)是八进制MOS管输出编辑型位权加法器本位输出等于7模块电路 图8(9)是一位八进制MOS管输出编辑型位权加法器模块组合主控运算电路 图9(1)是九进制MOS管输出编辑型位权加法器本位输出等于0模块电路 图9(2)是九进制MOS管输出编辑型位权加法器本位输出等于1模块电路 图9(3)是九进制MOS管输出编辑型位权加法器本位输出等于2模块电路 图9(4)是九进制MOS管输出编辑型位权加法器本位输出等于3模块电路 图9(5)是九进制MOS管输出编辑型位权加法器本位输出等于4模块电路 图9(6)是九进制MOS管输出编辑型位权加法器本位输出等于5模块电路 图9(7)是九进制MOS管输出编辑型位权加法器本位输出等于6模块电路 图9(8)是九进制MOS管输出编辑型位权加法器本位输出等于7模块电路 图9(9)是九进制MOS管输出编辑型位权加法器本位输出等于8模块电路 图9(10)是一位九进制MOS管输出编辑型位权加法器模块组合主控运算电路 图10(1)是十进制MOS管输出编辑型位权加法器本位输出等于0模块电路 图10(2)是十进制MOS管输出编辑型位权加法器本位输出等于1模块电路 图10(3)是十进制MOS管输出编辑型位权加法器本位输出等于2模块电路 图10(4)是十进制MOS管输出编辑型位权加法器本位输出等于3模块电路 图10(5)是十进制MOS管输出编辑型位权加法器本位输出等于4模块电路 图10(6)是十进制MOS管输出编辑型位权加法器本位输出等于5模块电路 图10(7)是十进制MOS管输出编辑型位权加法器本位输出等于6模块电路 图10(8)是十进制MOS管输出编辑型位权加法器本位输出等于7模块电路 图10(9)是十进制MOS管输出编辑型位权加法器本位输出等于8模块电路 图10(10)是十进制MOS管输出编辑型位权加法器本位输出等于9模块电路 图10(11)是一位十进制MOS管输出编辑型位权加法器模块组合主控运算电路 实施方式 参照图2(1)、2(2)、2(3),用两个专利申请201711119713.x“量化逻辑之多进制算 术运算器赋意分形集成单元电路”中权利要求3所述的电路做为单元电路,并且用各MOS 管 的栅极做为一组位权输入,各MOS管的漏极做为另一组位权输入,MOS管的栅极和漏极按照 加法规则和分形二极管的本位输出要求,依照图1(1)的加法表编辑并连接,因此组成输出 10 CN 111610951 A 说 明 书 8/12 页 本位相同的加法运算模块,本位输出等于0模块,本为输出等于1模块。本为输出等于 0模块 按图2(1)所述的方法及图1(1)所述的加法表,编辑输出的位权信息并连接到对应的输出位 权总线上。本为输出等于1模块按照图2(2)所述的方法及图1(1)所述的加法表,编辑输出的 位权信息并连接到对应的输出位权总线上。最后按照图2(3)的方法把本为输出等于0模块, 本为输出等于1模块的输入输出总线按线号对应的连接到一起做为加法器的位权输入、输 出,此即为一位二进制输出编辑型位权加法器。 参照图3(1)、3(2)、3(3),3(4)用三个专利申请201711119713.x“量化逻辑之多进 制算术运算器赋意分形集成单元电路”中权利要求3所述的电路做为单元电路,并且用各 MOS管的栅极做为一组位权输入,各MOS管的漏极做为另一组位权输入,MOS管的栅极和漏极 按照加法规则和分形二极管的本位输出要求,依照图1(2)的加法表编辑并连接,因此组成 输出本位相同的加法运算模块,本位输出等于0模块,本为输出等于1模块,本为输出等于2 模块。本为输出等于0模块按图3(1)所述的方法及图1(2)所述的加法表,编辑输出的位权信 息并连接到对应的输出位权总线上。本为输出等于1模块按照图3(2)所述的方法及图1(2) 所述的加法表,编辑输出的位权信息并连接到对应的输出位权总线上。本为输出等于2模块 按照图3(3)所述的方法及图1(2)所述的加法表,编辑输出的位权信息并连接到对应的输出 位权总线上。最后按照图3(4)的方法把本为输出等于0模块,本为输出等于1模块,本为输出 等于2模块的输入输出总线按线号对应的连接到一起做为加法器的位权输入、输出,此即为 一位三进制输出编辑型位权加法器。 参照图4(1),4(2),4(3),4(4)4(5)用四个专利申请201711119713.x“量化逻辑之 多进制算术运算器赋意分形集成单元电路”中权利要求3所述的电路做为单元电路,并且用 各MOS管的栅极做为一组位权输入,各MOS管的漏极做为另一组位权输入,MOS管的栅极和漏 极按照加法规则和分形二极管的本位输出要求,依照图1(3)的加法表编辑并连接,因此组 成输出本位相同的加法运算模块,本位输出等于0模块,本为输出等于1模块,本为输出等于 2模块,本为输出等于2模块。本为输出等于0模块按图4(1)所述的方法及图1(3)所述的加法 表,编辑输出的位权信息并连接到对应的输出位权总线上。本为输出等于 1模块按照图4 (2)所述的方法及图1(3)所述的加法表,编辑输出的位权信息并连接到对应的输出位权总 线上。本为输出等于2模块按照图4(3)所述的方法及图1(3)所述的加法表,编辑输出的位权 信息并连接到对应的输出位权总线上,本为输出等于3模块按照图4(4)所述的方法及图1 (3)所述的加法表,编辑输出的位权信息并连接到对应的输出位权总线上。最后按照图4(5) 的方法把本为输出等于0模块,本为输出等于1模块,本为输出等于2模块,本为输出等于3模 块的输入输出总线按线号对应的连接到一起做为加法器的位权输入、输出,此即为一位四 进制输出编辑型位权加法器。 参照图5(1),5(2),5(3),5(4)5(5),5(6),用五个专利申请201711119713.x “量化 逻辑之多进制算术运算器赋意分形集成单元电路”中权利要求3所述的电路做为单元电路, 并且用各MOS管的栅极做为一组位权输入,各MOS管的漏极做为另一组位权输入,MOS 管的 栅极和漏极按照加法规则和分形二极管的本位输出要求,依照图1(4)的加法表编辑并连 接,因此组成输出本位相同的加法运算模块,本位输出等于0模块,本为输出等于1 模块,本 为输出等于2模块,本为输出等于3模块,本为输出等于4模块。本为输出等于0 模块按图5 (1)所述的方法及图1(4)所述的加法表,编辑输出的位权信息并连接到对应的输出位权总 11 CN 111610951 A 说 明 书 9/12 页 线上。本为输出等于1模块按照图5(2)所述的方法及图1(4)所述的加法表,编辑输出的位权 信息并连接到对应的输出位权总线上。本为输出等于2模块按照图5(3)所述的方法及图1 (4)所述的加法表,编辑输出的位权信息并连接到对应的输出位权总线上,本为输出等于3 模块按照图5(4)所述的方法及图1(4)所述的加法表,编辑输出的位权信息并连接到对应的 输出位权总线上,本为输出等于4模块按照图5(5)所述的方法及图1(4)所述的加法表,编辑 输出的位权信息并连接到对应的输出位权总线上。最后按照图5(6)的方法把本为输出等于 0模块,本为输出等于1模块,本为输出等于2模块,本为输出等于3模块,本为输出等于4模块 的输入输出总线按线号对应的连接到一起做为加法器的位权输入、输出,此即为一位五进 制输出编辑型位权加法器。 参照图6(1),6(2),6(3),6(4)6(5),6(6),6(7),用六个专利申请201711119713.x “量化逻辑之多进制算术运算器赋意分形集成单元电路”中权利要求3所述的电路做为单元 电路,并且用各MOS管的栅极做为一组位权输入,各MOS管的漏极做为另一组位权输入,MOS 管的栅极和漏极按照加法规则和分形二极管的本位输出要求,依照图1(5)的加法表编辑并 连接,因此组成输出本位相同的加法运算模块,本位输出等于0模块,本为输出等于1 模块, 本为输出等于2模块,本为输出等于3模块,本为输出等于4模块,本为输出等于5 模块。本为 输出等于0模块按图6(1)所述的方法及图1(5)所述的加法表,编辑输出的位权信息并连接 到对应的输出位权总线上。本为输出等于1模块按照图6(2)所述的方法及图1(5)所述的加 法表,编辑输出的位权信息并连接到对应的输出位权总线上。本为输出等于2模块按照图6 (3)所述的方法及图1(5)所述的加法表,编辑输出的位权信息并连接到对应的输出位权总 线上,本为输出等于3模块按照图6(4)所述的方法及图1(5)所述的加法表,编辑输出的位权 信息并连接到对应的输出位权总线上,本为输出等于4模块按照图6(5)所述的方法及图1 (5)所述的加法表,编辑输出的位权信息并连接到对应的输出位权总线上,本为输出等于5 模块按照图6(6)所述的方法及图1(5)所述的加法表,编辑输出的位权信息并连接到对应的 输出位权总线上。最后按照图6(7)的方法把本为输出等于0模块,本为输出等于1模块,本为 输出等于2模块,本为输出等于3模块,本为输出等于4模块,本为输出等于5模块的输入输出 总线按线号对应的连接到一起做为加法器的位权输入、输出,此即为一位六进制输出编辑 型位权加法器。 参照图7(1),7(2),7(3),7(4),7(5),7(6),7(7),7(8),用七个专利申请 201711119713.x“量化逻辑之多进制算术运算器赋意分形集成单元电路”中权利要求3 所 述的电路做为单元电路,并且用各MOS管的栅极做为一组位权输入,各MOS管的漏极做为另 一组位权输入,MOS管的栅极和漏极按照加法规则和分形二极管的本位输出要求,依照图1 (6)的加法表编辑并连接,因此组成输出本位相同的加法运算模块,本位输出等于0模块,本 为输出等于1模块,本为输出等于2模块,本为输出等于3模块,本为输出等于4模块,本为输 出等于5模块,本为输出等于6模块。本为输出等于0模块按图7(1)所述的方法及图1(6)所述 的加法表,编辑输出的位权信息并连接到对应的输出位权总线上。本为输出等于1模块按照 图7(2)所述的方法及图1(6)所述的加法表,编辑输出的位权信息并连接到对应的输出位权 总线上。本为输出等于2模块按照图7(3)所述的方法及图1(6)所述的加法表,编辑输出的位 权信息并连接到对应的输出位权总线上,本为输出等于3模块按照图7(4)所述的方法及图1 (6)所述的加法表,编辑输出的位权信息并连接到对应的输出位权总线上,本为输出等于4 12 CN 111610951 A 说 明 书 10/12 页 模块按照图7(5)所述的方法及图1(6)所述的加法表,编辑输出的位权信息并连接到对应的 输出位权总线上,本为输出等于5模块按照图7(6)所述的方法及图1(6)所述的加法表,编辑 输出的位权信息并连接到对应的输出位权总线上,本为输出等于6模块按照图7(7)所述的 方法及图1(6)所述的加法表,编辑输出的位权信息并连接到对应的输出位权总线上。最后 按照图7(8)的方法把本为输出等于0模块,本为输出等于1模块,本为输出等于2模块,本为 输出等于3模块,本为输出等于4 模块,本为输出等于5模块,本为输出等于6模块的输入输 出总线按线号对应的连接到一起做为加法器的位权输入、输出,此即为一位七进制输出编 辑型位权加法器。 参照图8(1),8(2),8(3),8(4),8(5),8(6),8(7),8(8),8(9),用八个专利申请 201711119713.x“量化逻辑之多进制算术运算器赋意分形集成单元电路”中权利要求3所述 的电路做为单元电路,并且用各MOS管的栅极做为一组位权输入,各MOS管的漏极做为另一 组位权输入,MOS管的栅极和漏极按照加法规则和分形二极管的本位输出要求,依照图1(7) 的加法表编辑并连接,因此组成输出本位相同的加法运算模块,本位输出等于0模块,本为 输出等于1模块,本为输出等于2模块,本为输出等于3模块,本为输出等于4模块,本为输出 等于5模块,本为输出等于6模块,本为输出等于7模块。本为输出等于0模块按图8(1)所述的 方法及图1(7)所述的加法表,编辑输出的位权信息并连接到对应的输出位权总线上。本为 输出等于1模块按照图8(2)所述的方法及图1(7)所述的加法表,编辑输出的位权信息并连 接到对应的输出位权总线上。本为输出等于2模块按照图8(3)所述的方法及图1(7)所述的 加法表,编辑输出的位权信息并连接到对应的输出位权总线上,本为输出等于3模块按照图 8(4)所述的方法及图1(7)所述的加法表,编辑输出的位权信息并连接到对应的输出位权总 线上,本为输出等于4模块按照图8(5)所述的方法及图1(7)所述的加法表,编辑输出的位权 信息并连接到对应的输出位权总线上,本为输出等于5模块按照图8(6)所述的方法及图1 (7)所述的加法表,编辑输出的位权信息并连接到对应的输出位权总线上,本为输出等于6 模块按照图8(7)所述的方法及图1(7)所述的加法表,编辑输出的位权信息并连接到对应的 输出位权总线上,本为输出等于 7模块按照图8(8)所述的方法及图1(7)所述的加法表,编 辑输出的位权信息并连接到对应的输出位权总线上。最后按照图8(9)的方法把本为输出等 于0模块,本为输出等于1 模块,本为输出等于2模块,本为输出等于3模块,本为输出等于4 模块,本为输出等于5 模块,本为输出等于6模块,本为输出等于7模块的输入输出总线按线 号对应的连接到一起做为加法器的位权输入、输出,此即为一位八进制输出编辑型位权加 法器。 参照图9(1),9(2),9(3),9(4),9(5),9(6),9(7),9(8),9(9),9(10),用九个专利申 请201711119713.x“量化逻辑之多进制算术运算器赋意分形集成单元电路”中权利要求3所 述的电路做为单元电路,并且用各MOS管的栅极做为一组位权输入,各MOS 管的漏极做为另 一组位权输入,MOS管的栅极和漏极按照加法规则和分形二极管的本位输出要求,依照图1 (8)的加法表编辑并连接,因此组成输出本位相同的加法运算模块,本位输出等于0模块,本 为输出等于1模块,本为输出等于2模块,本为输出等于3模块,本为输出等于4模块,本为输 出等于5模块,本为输出等于6模块,本为输出等于7模块,本为输出等于8模块。本为输出等 于0模块按图9(1)所述的方法及图1(8)所述的加法表,编辑输出的位权信息并连接到对应 的输出位权总线上。本为输出等于1模块按照图9(2)所述的方法及图1(8)所述的加法表,编 13 CN 111610951 A 说 明 书 11/12 页 辑输出的位权信息并连接到对应的输出位权总线上。本为输出等于2模块按照图9(3)所述 的方法及图1(8)所述的加法表,编辑输出的位权信息并连接到对应的输出位权总线上,本 为输出等于3模块按照图9(4)所述的方法及图1(8)所述的加法表,编辑输出的位权信息并 连接到对应的输出位权总线上,本为输出等于4模块按照图9(5)所述的方法及图1(8)所述 的加法表,编辑输出的位权信息并连接到对应的输出位权总线上,本为输出等于5模块按照 图9(6)所述的方法及图1(8)所述的加法表,编辑输出的位权信息并连接到对应的输出位权 总线上,本为输出等于6模块按照图9(7)所述的方法及图1(8)所述的加法表,编辑输出的位 权信息并连接到对应的输出位权总线上,本为输出等于7模块按照图9(8)所述的方法及图1 (8)所述的加法表,编辑输出的位权信息并连接到对应的输出位权总线上,本为输出等于8 模块按照图9(9)所述的方法及图1(8)所述的加法表,编辑输出的位权信息并连接到对应的 输出位权总线上。最后按照图9(10)的方法把本为输出等于0模块,本为输出等于1模块,本 为输出等于2模块,本为输出等于3模块,本为输出等于4模块,本为输出等于5模块,本为输 出等于6模块,本为输出等于7模块,本为输出等于8模块的输入输出总线按线号对应的连接 到一起做为加法器的位权输入、输出,此即为一位九进制输出编辑型位权加法器。 参照图10(1),10(2),10(3),10(4),10(5),10(6),10(7),10(8),10(9), 10(10), 10(11),用十个专利申请201711119713.x“量化逻辑之多进制算术运算器赋意分形集成单 元电路”中权利要求3所述的电路做为单元电路,并且用各MOS管的栅极做为一组位权输入, 各MOS管的漏极做为另一组位权输入,MOS管的栅极和漏极按照加法规则和分形二极管的本 位输出要求,依照图1(9)的加法表编辑并连接,因此组成输出本位相同的加法运算模块,本 位输出等于0模块,本为输出等于1模块,本为输出等于2模块,本为输出等于3模块,本为输 出等于4模块,本为输出等于5模块,本为输出等于6模块,本为输出等于7模块,本为输出等 于8模块,本为输出等于9模块。本为输出等于0模块按图10(1)所述的方法及图1(9)所述的 加法表,编辑输出的位权信息并连接到对应的输出位权总线上。本为输出等于1模块按照图 10(2)所述的方法及图1(9)所述的加法表,编辑输出的位权信息并连接到对应的输出位权 总线上。本为输出等于2模块按照图10(3)所述的方法及图1(9)所述的加法表,编辑输出的 位权信息并连接到对应的输出位权总线上,本为输出等于3模块按照图10(4)所述的方法及 图1(9)所述的加法表,编辑输出的位权信息并连接到对应的输出位权总线上,本为输出等 于4模块按照图10(5)所述的方法及图1(9)所述的加法表,编辑输出的位权信息并连接到对 应的输出位权总线上,本为输出等于 5模块按照图10(6)所述的方法及图1(9)所述的加法 表,编辑输出的位权信息并连接到对应的输出位权总线上,本为输出等于6模块按照图10 (7)所述的方法及图1(9)所述的加法表,编辑输出的位权信息并连接到对应的输出位权总 线上,本为输出等于7模块按照图10(8)所述的方法及图1(9)所述的加法表,编辑输出的位 权信息并连接到对应的输出位权总线上,本为输出等于8模块按照图10(9)所述的方法及图 1(9)所述的加法表,编辑输出的位权信息并连接到对应的输出位权总线上,本为输出等于9 模块按照图10(10)所述的方法及图1(9)所述的加法表,编辑输出的位权信息并连接到对应 的输出位权总线上。最后按照图10(11)的方法把本为输出等于0模块,本为输出等于1模块, 本为输出等于2 模块,本为输出等于3模块,本为输出等于4模块,本为输出等于5模块,本为 输出等于6 模块,本为输出等于7模块,本为输出等于8模块,本为输出等于8模块的输入输 出总线按线号对应的连接到一起做为加法器的位权输入、输出,此即为一位十进制输出编 14 CN 111610951 A 说 明 书 12/12 页 辑型位权加法器。 15 CN 111610951 A 说 明 书 附 图 1/20 页 图1 16 CN 111610951 A 说 明 书 附 图 2/20 页 图2 17 CN 111610951 A 说 明 书 附 图 3/20 页 图3 18 CN 111610951 A 说 明 书 附 图 4/20 页 图4 19 CN 111610951 A 说 明 书 附 图 5/20 页 图5 20 CN 111610951 A 说 明 书 附 图 6/20 页 图6 21 CN 111610951 A 说 明 书 附 图 7/20 页 22 CN 111610951 A 说 明 书 附 图 8/20 页 23 CN 111610951 A 说 明 书 附 图 9/20 页 图7 24 CN 111610951 A 说 明 书 附 图 10/20 页 25 CN 111610951 A 说 明 书 附 图 11/20 页 26 CN 111610951 A 说 明 书 附 图 12/20 页 图8 27 CN 111610951 A 说 明 书 附 图 13/20 页 28 CN 111610951 A 说 明 书 附 图 14/20 页 29 CN 111610951 A 说 明 书 附 图 15/20 页 30 CN 111610951 A 说 明 书 附 图 16/20 页 图9 31 CN 111610951 A 说 明 书 附 图 17/20 页 32 CN 111610951 A 说 明 书 附 图 18/20 页 33 CN 111610951 A 说 明 书 附 图 19/20 页 34 CN 111610951 A 说 明 书 附 图 20/20 页 图10 35