技术摘要:

本发明提供一种用于伪静态随机存取存储器的控制电路以及控制方法。控制电路基于外部时脉对数据的锁存次数进行计数以产生第一计数值,基于非同步行地址选通时脉对数据的写入次数进行计数以产生第二计数值,并且比较第一计数值与第二计数值。控制电路在非同步模式依据非 全部

背景技术:

近年来,随着半导体存储器元件的整合水准变得愈来愈高,而存在对更高速度的 需求,静态随机存取存储器(Static Random Access Memory,SRAM)及动态随机存取存储器 (Dynamic Random Access Memory,DRAM)做为高速存储器被使用。对于具有动态随机存取 存储器的优点的伪静态随机存取存储器(Pseudo Static Random Access Memory,pSRAM) 的需求持续增加,特别是运用在行动装置中。 伪静态随机存取存储器为具有动态随机存取存储器的单元结构及静态随机存取 存储器的周边电路的存储器元件。虽然伪静态随机存取存储器具有大容量及低成本的优 点。现有的伪静态随机存取存储器在写入操作的时脉周期较短的情况下,数据的写入可能 同步或不同步。为了避免错误发生,在写入操作中,数据的写入在不同步(即,写入操作的非 同步模式)的情况下建立一控制路径以提供对应的行地址选通(column address strobe, CAS)时脉,并且在同步(即,写入操作的同步模式)的情况下建立一控制路径以提供对应的 另一行地址选通时脉。如此一来,伪静态随机存取存储器能够通过不同的控制路径执行写 入操作的同步模式或非同步模式。 然而,在上述的方法中,由于时脉周期较短,伪静态随机存取存储器在由非同步模 式切换到同步模式时,可能会因为路径的变更而造成在控制路径变更后,来不及在路径变 更的第一个时脉产生行地址选通时脉,进而造成写入操作的错误。

技术实现要素:

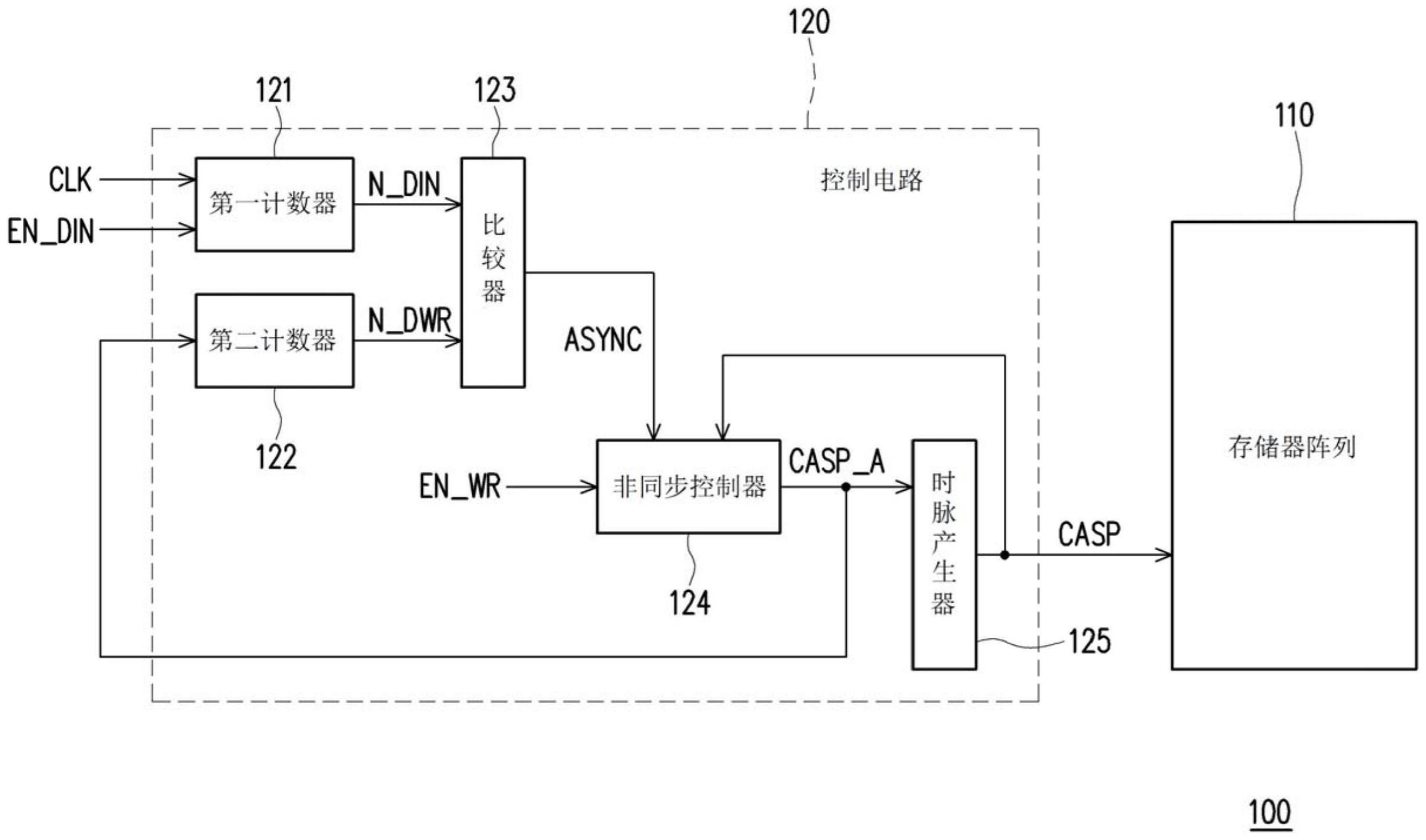

本发明提供一种用于伪静态随机存取存储器的控制电路以及控制方法,可以在写 入操作中不需通过多个控制路径来执行写入操作的同步模式以及非同步模式。 本发明的控制电路适用于伪静态随机存取存储器。控制电路包括第一计数器、第 二计数器、比较器、非同步控制器以及时脉产生器。第一计数器用以基于外部时脉对写入至 伪静态随机存取存储器的数据的锁存次数进行计数,以产生第一计数值。第二计数器用以 基于非同步行地址选通时脉对写入至伪静态随机存取存储器的数据的写入次数进行计数, 以产生第二计数值。非同步行地址选通时脉的初始周期小于外部时脉的周期。比较器耦接 于第一计数器以及第二计数器。比较器用以比较第一计数值与第二计数值。当第一计数值 等于第二计数值时,比较器提供第一逻辑电平的模式信号。非同步控制器耦接于比较器以 及第二计数器。非同步控制器用以在写入操作中接收模式信号以及行地址选通时脉,并且 在非同步模式依据行地址选通时脉提供非同步行地址选通时脉。当非同步控制器第一次接 收到第一逻辑电平的模式信号时,非同步控制器将写入操作由非同步模式进入同步模式, 以将非同步行地址选通时脉的周期调整为外部时脉的周期。时脉产生器耦接于非同步控制 5 CN 111599395 A 说 明 书 2/9 页 器。时脉产生器用以依据非同步行地址选通时脉提供行地址选通时脉。 在本发明的控制方法适用于伪静态随机存取存储器。控制方法包括:基于外部时 脉对写入至伪静态随机存取存储器的数据的锁存次数进行计数,以产生第一计数值;在非 同步模式依据行地址选通时脉提供非同步行地址选通时脉;基于非同步行地址选通时脉对 写入至伪静态随机存取存储器的数据的写入次数进行计数,以产生第二计数值,其中非同 步行地址选通时脉的初始周期小于外部时脉的周期;比较第一计数值与第二计数值,其中 当第一计数值等于第二计数值时提供第一逻辑电平的模式信号;当第一次接收到第一逻辑 电平的模式信号时,将写入操作由非同步模式进入同步模式以将非同步行地址选通时脉的 周期调整为外部时脉的周期;以及依据非同步行地址选通时脉提供行地址选通时脉。 基于上述,本发明的控制电路基于外部时脉对数据的锁存次数进行计数以产生第 一计数值,基于非同步行地址选通时脉对数据的写入次数进行计数以产生第二计数值,并 且比较第一计数值与第二计数值。控制电路在非同步模式依据行地址选通时脉提供非同步 行地址选通时脉以提供行地址选通时脉。当第一次发生第一计数值等于第二计数值时,控 制电路将写入操作由非同步模式进入同步模式以将非同步行地址选通时脉的周期调整为 外部时脉的周期以提供行地址选通时脉。如此一来,本发明能够在写入操作中不需通过多 个控制路径来执行写入操作的同步模式以及非同步模式。 为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详 细说明如下。 附图说明 图1是依据本发明的第一实施例所示出的伪静态随机存取存储器的电路示意图; 图2是依据第一实施例所示出的写入操作的时序图; 图3是依据第一实施例所示出的非同步控制器的电路示意图; 图4是依据第一实施例所示出的时脉产生器的电路示意图; 图5是依据第一实施例所示出的控制方法流程图; 图6是依据本发明的第二实施例所示出的控制电路的电路示意图; 图7是依据第二实施例所示出的写入操作的时序图; 图8是依据第二实施例所示出的同步控制器的电路示意图; 图9是依据第二实施例所示出的时脉产生器的电路示意图; 图10是依据第二实施例所示出的控制方法流程图。 附图标记说明 100:伪静态随机存取存储器 110:存储器阵列 120、620:控制电路 121、621:第一计数器 122、622:第二计数器 123、623:比较器 124、624:非同步控制器 1242、1254、1256、6254、6256、6258:时序调整器 6 CN 111599395 A 说 明 书 3/9 页 1244:非同步判断器 125、625:时脉产生器 1252、6252:正反器 626:同步写入指示器 627:同步控制器 ASYNC:模式信号 CASP:行地址选通时脉 CASP_A:非同步行地址选通时脉 CASP_S:同步行地址选通时脉 CLK:外部时脉 D1、D2、D3、D4:延迟器 DQ、D00~D13:数据 EN_DIN:输入指示信号 EN_WR:写入指示信号 N01、N02、N03、N04、N05、N06、N07、N08、N09、N10、N11:反相器 NAND1、NAND2、NAND3、NAND4、NAND5、NAND6:反及闸 N_DIN:第一计数值 N_DWR:第二计数值 Q:输出端 /R:重置输入端 /S:设定输入端 /S1:第一设定输入端 /S2:第二设定输入端 S510~S570:步骤 S1010~S1040:步骤 SYNCWR:同步写入指示信号 t1、t2、t3、t4、ti1、ti2:时间点