技术摘要:

一种硅块的品质判定方法,其判定从利用提拉法提拉的单晶硅中切出的多个硅块的品质,在该硅块的品质判定方法中执行:取得从多个硅块各自的端部切出的样品晶片的品质评价结果的步骤(S2);取得单晶硅的提拉实际数据的步骤(S3);根据各样品晶片的品质评价结果,设定各硅块 全部

背景技术:

以往,在制造硅晶片等半导体晶片时,例如在对利用提拉法提拉的单晶硅锭进行 外周磨削后,切掉不能作为产品而使用的顶部与尾部。之后,利用线锯等切断装置,将单晶 硅锭切成多个硅块。 此时,从硅块的端部切出样品晶片,通过评价电阻率、氧浓度、OSF(Oxidation Induced Stacking Fault ring,氧化诱导层错环)、Void缺陷、L/DL缺陷(Large Dislocation Loop,大位错环)等Grown-in(原生)缺陷等,进行硅块的品质评价。 另外,近年来,强烈地需求在晶片的整个表面中没有原生缺陷或只有极低密度的 原生缺陷的晶片,伴随于此,还强烈地需求没有原生缺陷或只有极低密度的原生缺陷的单 晶硅。 作为提拉这种单晶硅的方法,例如有改善提拉装置的炉内温度分布,一边调整提 拉速度,一边提拉单晶硅的方法。 然而,提拉速度的管理范围非常狭小,因此即使硅块端部的晶体品质合格,若在块中间 部提拉速度发生变动,则会有在硅块中产生原生缺陷的情况,因此存在下一个工序中发生 不良的问题。 在此,在不良中,将基于L/DL缺陷的检测结果的不良称为L/DL不良,将基于Void缺陷的 检测结果的不良称为Void不良。 专利文献1中公开有如下技术:沿着单晶硅锭的生长轴将提拉数据读取到计算机 中,当提拉数据与目标值之差成为规定值以上时,在成为规定位置以上的位置切断单晶硅 锭,获得没有原生缺陷的硅块。 现有技术文献 专利文献 专利文献1:日本特开2007-99556号公报

技术实现要素:

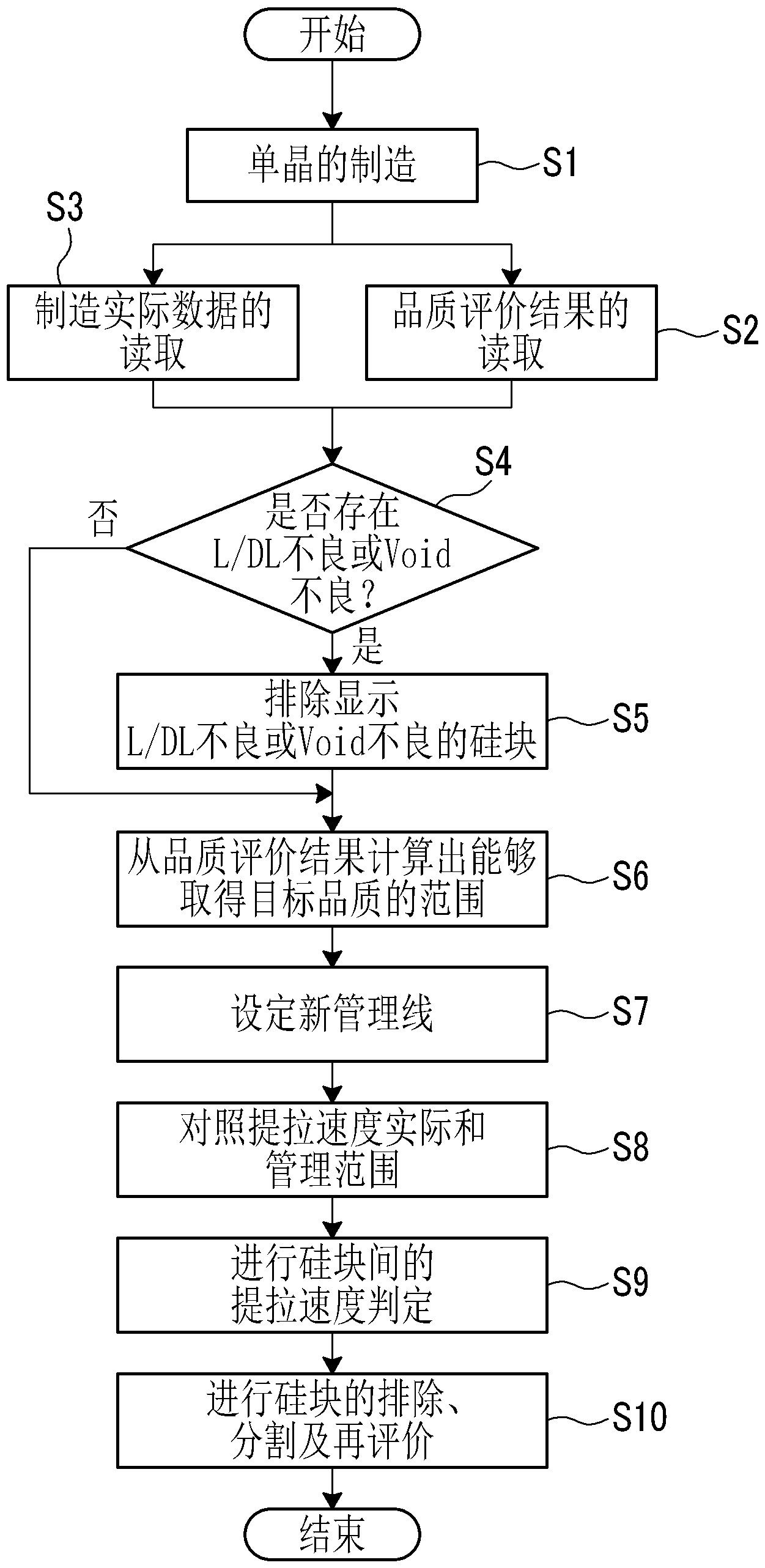

发明所要解决的技术问题 然而,专利文献1中公开的技术中,由于以使提拉数据与目标值之差成为规定值的 方式进行管理,因此不一定与实际的样品晶片的品质评价结果一致。因此,在下一个工序 中,排除被判定为不良品的硅块并切断硅块,并且再次进行品质评价的情况下,不知道在哪 一个部分发生了不良,因此存在导致品质确认频度增加的问题。 本发明的目的在于提供一种能够降低下一个工序中的品质确认频度的硅块的品 3 CN 111601916 A 说 明 书 2/8 页 质判定方法、硅块的品质判定程序及单晶硅的制造方法。 用于解决技术问题的方案 本发明的硅块的品质判定方法是判定从利用提拉法提拉的单晶硅中切出的多个 硅块的品质的硅块的品质判定方法,所述硅块的品质判定方法的特征在于执行:取得从多 个硅块各自的端部切出的样品晶片的品质评价结果的步骤;取得所述单晶硅的提拉实际数 据的步骤;根据各样品晶片的品质评价结果,设定各硅块的提拉管理范围的步骤;以及对照 所取得的所述提拉实际数据和所设定的提拉管理范围,判定各硅块的品质的步骤。 在此,样品晶片的品质评价是指在不存在原生缺陷的单晶硅的Pv区域、Pv区域及 Pi区域混合存在的区域以及Pi区域中的品质评价。 并且,提拉管理范围是指相对于提拉目标值能够允许的实际值的范围,其根据样品晶 片的品质评价结果来设定。 根据本发明,根据样品晶片的品质评价结果,设定各硅块的提拉管理范围,对照每个硅 块的提拉管理范围以及提拉实际数据。因此,能够高精度地判定超出提拉管理范围的提拉 实际数据,并能够降低下一个工序中的品质确认频度。 本发明中,优选在设定所述提拉管理范围的步骤之前,在所述样品晶片的品质评 价结果中,若取得显示L/DL(Large Dislocation Loop)不良的结果,则执行排除显示该结 果的硅块的步骤。 根据本发明,若样品晶片显示出L/DL不良,则切出该样品晶片的所有硅块都是L/DL不 良的可能性高,因此能够预先排除不良品来更加降低下一个工序中的品质确认频度。 本发明中,优选在设定所述提拉管理范围的步骤之前,在所述样品晶片的品质评 价结果中,若取得显示Void不良的结果,则执行排除显示该结果的硅块的步骤。 根据本发明,与L/DL不良的情况相同地,能够排除Void不良的硅块,而更加降低下一个 工序中的品质确认频度。 本发明的硅块的品质判定程序的特征在于,使计算机执行前述的硅块的品质判定 方法。 根据本发明,通过使计算机执行,能够促进自动化,因此能够减轻品质管理工序本身的 负担。 本发明的单晶硅的制造方法的特征在于,使计算机执行前述的硅块的品质判定程 序,计算出提拉单晶硅时的提拉管理范围,并根据计算出的提拉管理范围,控制所述单晶硅 的提拉。 根据本发明,根据对每个硅块设定的提拉管理范围,控制单晶硅的提拉,由此能够防止 产生品质不合格的硅块来减少不合格品的产生。 附图说明 图1是表示本发明的实施方式所涉及的单晶硅的提拉装置的示意图。 图2是表示所述实施方式的单晶硅的品质判定方法的流程图。 图3是用于说明所述实施方式的管理范围的示意图。 图4是用于说明所述实施方式的管理范围的示意图。 图5是表示实施例的品质判定结果的图表。 4 CN 111601916 A 说 明 书 3/8 页 图6是表示实施例的品质判定结果的图表。