技术摘要:

本发明提供一种半导体集成电路的制造方法。该半导体集成电路的制造方法包括以下工序:在n‑型的半导体层(12)的上部的一部分改变注入位置地多级注入p型杂质离子,形成第一离子注入区;在上部的其它的一部分改变注入位置地多级注入p型杂质离子,形成第二离子注入区;使第 全部

背景技术:

提出了一种输出级的纵向型MOSFET以及用于控制纵向型MOSFET的横向型MOSFET 被单片集成(混合搭载)到同一半导体芯片的功率IC(参照专利文献1~3)。在专利文献1~3 所记载的功率IC的制造方法中,在向半导体基板表面注入杂质离子之后,进行高温且长时 间的热处理,形成用于形成纵向型的输出级元件的体区。另外,在向半导体基板表面的规定 的位置注入杂质离子之后,进行高温且长时间的热处理,形成用于形成横向型的控制元件 的阱区。多次像这样进行高温且长时间的热处理,因此制造时间长。另外,多次的热处理导 致扩散层的杂质浓度产生偏差、器件特性产生偏差。 专利文献4~6中提出了一种不依赖于高温且长时间的热处理地形成与纵向型的 输出级元件及横向型的控制元件相关联的扩散层的技术。在专利文献4、5中公开了一种使 用高加速电压的离子注入装置来形成沟槽MOSFET的体区的技术。在专利文献6中公开了一 种与抑制热处理量、使杂质不过度地扩散这样的分离扩散层的形成方法相关的技术。 然而,在专利文献1~6中,对于提高将纵向型的输出级元件和横向型的控制元件 集成到同一半导体芯片的半导体集成电路的集成密度、缩短制造时间,没有进行公开。 现有技术文献 专利文献 专利文献1:日本特开2000-91344号公报 专利文献2:日本专利第5641131号公报 专利文献3:日本专利第6037085号公报 专利文献4:日本特开2006-80177号公报 专利文献5:日本特开2001-339063号公报 专利文献6:日本特开2012-80117号公报

技术实现要素:

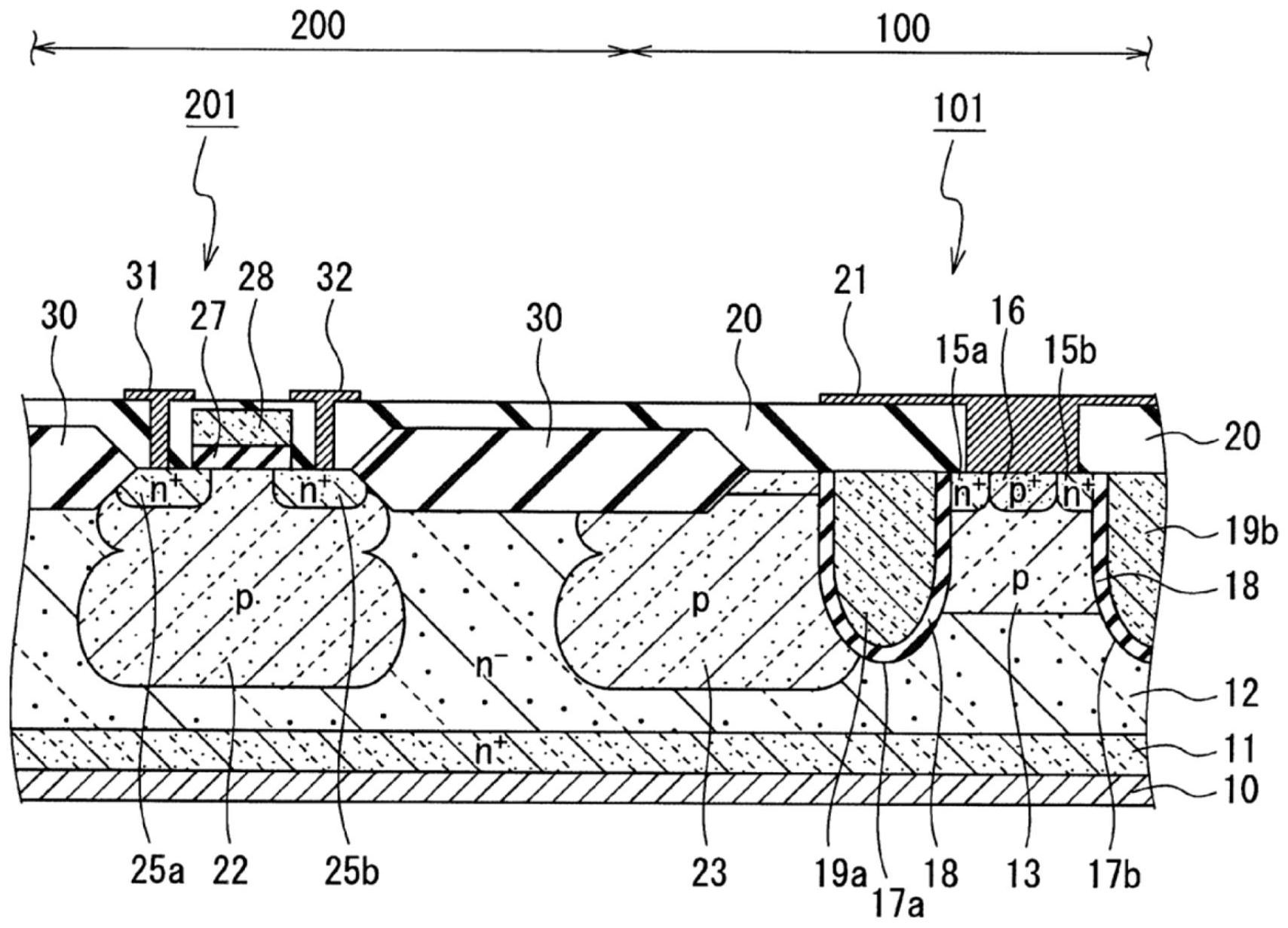

发明要解决的问题 鉴于上述问题,本发明的目的在于提供一种能够以短时间制造出改善电气特性、 面积利用效率高的高集成密度化构造的半导体集成电路的制造方法。 用于解决问题的方案 本发明的一个方式的宗旨在于一种半导体集成电路的制造方法,包括以下工序: (a)在第一导电型的半导体层的上部的一部分改变注入位置地多级注入呈第二导电型的杂 质离子,由此选择性地形成第一离子注入区;(b)在半导体层的上部的其它的一部分改变所 4 CN 111584429 A 说 明 书 2/16 页 述注入位置地多级注入呈第二导电型的杂质离子,由此选择性地形成第二离子注入区;(c) 使第一离子注入区的杂质离子活化来形成第二导电型的阱区,同时使第二离子注入区的杂 质离子活化来形成第二导电型的体区;(d)在阱区的上部形成具有彼此相向的第一导电型 的第一端子区和第二端子区的控制元件;以及(e)在体区的上部形成具有第一导电型的输 出端子区且由控制元件来控制的输出级元件。 发明的效果 根据本发明,能够提供一种能够以短时间制造出改善电气特性、面积利用效率高 的高集成密度化构造的半导体集成电路的制造方法。 附图说明 图1是表示本发明的实施方式所涉及的半导体集成电路的一例的主要部分截面 图。 图2是表示本发明的实施方式所涉及的半导体集成电路的一例的等效电路图。 图3是表示本发明的实施方式所涉及的半导体集成电路的制造方法的一例的工序 截面图。 图4是接着图3的表示本发明的实施方式所涉及的半导体集成电路的制造方法的 一例的工序截面图。 图5是接着图4的表示本发明的实施方式所涉及的半导体集成电路的制造方法的 一例的工序截面图。 图6是接着图5的表示本发明的实施方式所涉及的半导体集成电路的制造方法的 一例的工序截面图。 图7是接着图6的表示本发明的实施方式所涉及的半导体集成电路的制造方法的 一例的工序截面图。 图8是接着图7的表示本发明的实施方式所涉及的半导体集成电路的制造方法的 一例的工序截面图。 图9A是接着图8的表示本发明的实施方式所涉及的半导体集成电路的制造方法的 一例的工序截面图。 图9B是表示本发明的实施方式所涉及的构成控制元件的横向型半导体元件的从 表面起在深度方向上的杂质浓度分布的曲线图。 图10是接着图9A的表示本发明的实施方式所涉及的半导体集成电路的制造方法 的一例的工序截面图。 图11是接着图10的表示本发明的实施方式所涉及的半导体集成电路的制造方法 的一例的工序截面图。 图12是接着图11的表示本发明的实施方式所涉及的半导体集成电路的制造方法 的一例的工序截面图。 图13是接着图12的表示本发明的实施方式所涉及的半导体集成电路的制造方法 的一例的工序截面图。 图14是接着图13的表示本发明的实施方式所涉及的半导体集成电路的制造方法 的一例的工序截面图。 5 CN 111584429 A 说 明 书 3/16 页 图15是接着图14的表示本发明的实施方式所涉及的半导体集成电路的制造方法 的一例的工序截面图。 图16是接着图15的表示本发明的实施方式所涉及的半导体集成电路的制造方法 的一例的工序截面图。 图17是接着图16的表示本发明的实施方式所涉及的半导体集成电路的制造方法 的一例的工序截面图。 图18是表示比较例所涉及的半导体集成电路的主要部分截面图。 图19是表示比较例所涉及的半导体集成电路的制造方法的工序截面图。 图20是接着图19的表示比较例所涉及的半导体集成电路的制造方法的工序截面 图。 图21是接着图20的表示比较例所涉及的半导体集成电路的制造方法的工序截面 图。 图22是接着图21的表示比较例所涉及的半导体集成电路的制造方法的工序截面 图。 图23是接着图22的表示比较例所涉及的半导体集成电路的制造方法的工序截面 图。 图24是接着图23的表示比较例所涉及的半导体集成电路的制造方法的工序截面 图。 图25是接着图24的表示比较例所涉及的半导体集成电路的制造方法的工序截面 图。 图26是接着图25的表示比较例所涉及的半导体集成电路的制造方法的工序截面 图。 图27是表示本发明的实施方式的第一变形例所涉及的半导体集成电路的制造方 法的一例的工序截面图。 图28是接着图27的表示本发明的实施方式的第一变形例所涉及的半导体集成电 路的制造方法的一例的工序截面图。 图29是表示本发明的实施方式的第二变形例所涉及的半导体集成电路的制造方 法的一例的工序截面图。 图30是接着图29的表示本发明的实施方式的第二变形例所涉及的半导体集成电 路的制造方法的一例的工序截面图。 图31是接着图30的表示本发明的实施方式的第二变形例所涉及的半导体集成电 路的制造方法的一例的工序截面图。 图32是表示本发明的实施方式的第三变形例所涉及的半导体集成电路的制造方 法的一例的工序截面图。 图33是表示本发明的实施方式的第四变形例所涉及的半导体集成电路的制造方 法的一例的工序截面图。 图34是接着图33的表示本发明的实施方式的第四变形例所涉及的半导体集成电 路的制造方法的一例的工序截面图。 图35是接着图34的表示本发明的实施方式的第四变形例所涉及的半导体集成电 6 CN 111584429 A 说 明 书 4/16 页 路的制造方法的一例的工序截面图。 图36是接着图35的表示本发明的实施方式的第四变形例所涉及的半导体集成电 路的制造方法的一例的工序截面图。 图37是表示本发明的实施方式的第五变形例所涉及的半导体集成电路的制造方 法的一例的工序截面图。 图38是接着图37的表示本发明的实施方式的第五变形例所涉及的半导体集成电 路的制造方法的一例的工序截面图。 图39是接着图38的表示本发明的实施方式的第五变形例所涉及的半导体集成电 路的制造方法的一例的工序截面图。 图40是接着图39的表示本发明的实施方式的第五变形例所涉及的半导体集成电 路的制造方法的一例的工序截面图。 图41是接着图40的表示本发明的实施方式的第五变形例所涉及的半导体集成电 路的制造方法的一例的工序截面图。 附图标记说明 10:背面电极;11:背面接触层;12:半导体层;13、13x:体区;13a、13b:第二离子注 入区;15a、15b:主电极区;16:基极接触区;17a、17b:沟槽;17c、17d:元件分离槽;18、27:栅 极绝缘膜;18p、18q:元件分离绝缘膜;19a、19b、28:栅极电极;19p、19q:虚设电极;20:层间 绝缘膜;21:输出端子布线;22、22x:第一阱区;22a、22b、22c、22d、22e、23a、23b、23c:第一离 子注入区;23、23x:第二阱区;25a:第一端子区;25b:第二端子区;30:场氧化膜;31:第一电 路端子布线;32:第二电路端子布线;34、43、44、47、50、51、52、53、54、55、56、59、60:光致抗 蚀剂膜;41、48、57、58:蚀刻保护膜;42、42a、42b、49:耐氧化性膜(氮化硅膜);45、46:选择离 子注入用掩模;100:输出部;101:输出级元件;200:电路部;201:控制元件。