技术摘要:

本申请公开了FPGA单粒子翻转纠错方法及电路、电子设备、计算机可读存储介质,该方法包括:检测配置数据帧地址是否是不需要ECC校验的帧地址;若所述配置数据帧地址是不需要ECC校验的帧地址,则不对所述配置数据帧地址对应的配置数据帧进行ECC校验;若所述配置数据帧地址 全部

背景技术:

单粒子翻转(SEU,Single Event Upset)是由于空间粒子辐射而导致存储单元发 生位翻转(即内容由0变成1,或由1变成0)。SEU效应是瞬态的、非破坏性的,但是它可能会改 变微电子电路的RAM(Random Access Memory,随机访问存储器)构型,对可编程电子硬件所 执行的功能产生不利影响。 现代民机飞控、航电等系统高度复杂,其大量采用了基于RAM的复杂电子设备。例 如微处理器,现场可编程门阵列FPGA(Field Programmable Gate Arrays)等。目前在民机 机载设备的研制过程中,得到了广泛应用的芯片主要包括专用集成电路器件ASIC (Application Specific Integrated Circuit的简写)和FPGA。ASIC芯片能够实现高密度、 小体积和低功耗,但ASIC制片成本和风险较高,欠缺灵活性。ASIC虽然也对SEU敏感,但相对 来说具有较好的抗SEU特性。随着电子工业的飞速发展,FPGA由于兼顾高性能及灵活性,在 数字系统设计及ASIC原型前端设计中得到广泛的应用。 FPGA的主流技术有基于反熔丝、基于SRAM和基于FLASH三种。相对于反熔丝和基于 FLASH的FPGA,SRAM型FPGA抗辐射能力存在不足,但是其强大的性能优势和设计灵活性对飞 控和航电应用仍具有巨大吸引力。目前占据市场份额最大的FPGA厂商Xilinx和Altera的绝 大部分产品都是基于SRAM的,欧美等国家的航空航天机构也把SRAM型FPGA作为核心电子元 器件。 由于SRAM型FPGA对于SEU效应敏感,在民机系统和设备设计时,为将SEU带来的安 全性影响减缓到最小,可针对SEU效应敏感的器件,采用三模冗余(Triple Module Redundancy,TMR)、纠错码(Error Correction Code,ECC)和擦洗(Scrubbing)这几种常见 的SEU减缓措施。三模冗余技术纠错速度快,但缺点是附加硬件资源多,不适用与大规模 SRAM型FPGA SEU减缓加固。而擦洗本质上不能解决SEU效应带来的问题,仅提供一定程度的 减缓。 纠错码是一种针对SEU常见的减缓方法,可使用特定的编码和解码规则,检测和纠 正存储器中的故障。纠错码的基本原理是在信息编码序列上附加冗余编码,然后进行存储 和传输,这些冗余编码与信息编码之间存在某种确定的相互关联。接收方可以通过校验冗 余编码与信息编码之间的关联,发现是否受到SEU影响,继而实现故障隔离或者利用编码算 法将其纠正。FPGA的ECC编码目的,是为了在读取存储单元的内容时,能够发现差错并将其 纠正。一般采用既能检错又能纠错的编码方法,如循环冗余校验CRC、海明码(Hamming Code)等。目前FPGA厂商Xilinx和Altera在其绝大部分器件内实现了内嵌单粒子翻转纠错 电路,用于减缓SEU效应。不足是仍然存在一些问题,以Xilinx的纠错电路为例,在实行ECC 操作时,用户必须检查FPGA内的所有帧,不能配置回读帧数据的地址,这种设计方法增加了 5 CN 111597073 A 说 明 书 2/9 页 回读数据误报的风险,对于那些读操作容易受到用户逻辑影响的帧地址,进行ECC校验可能 会产生误报。

技术实现要素:

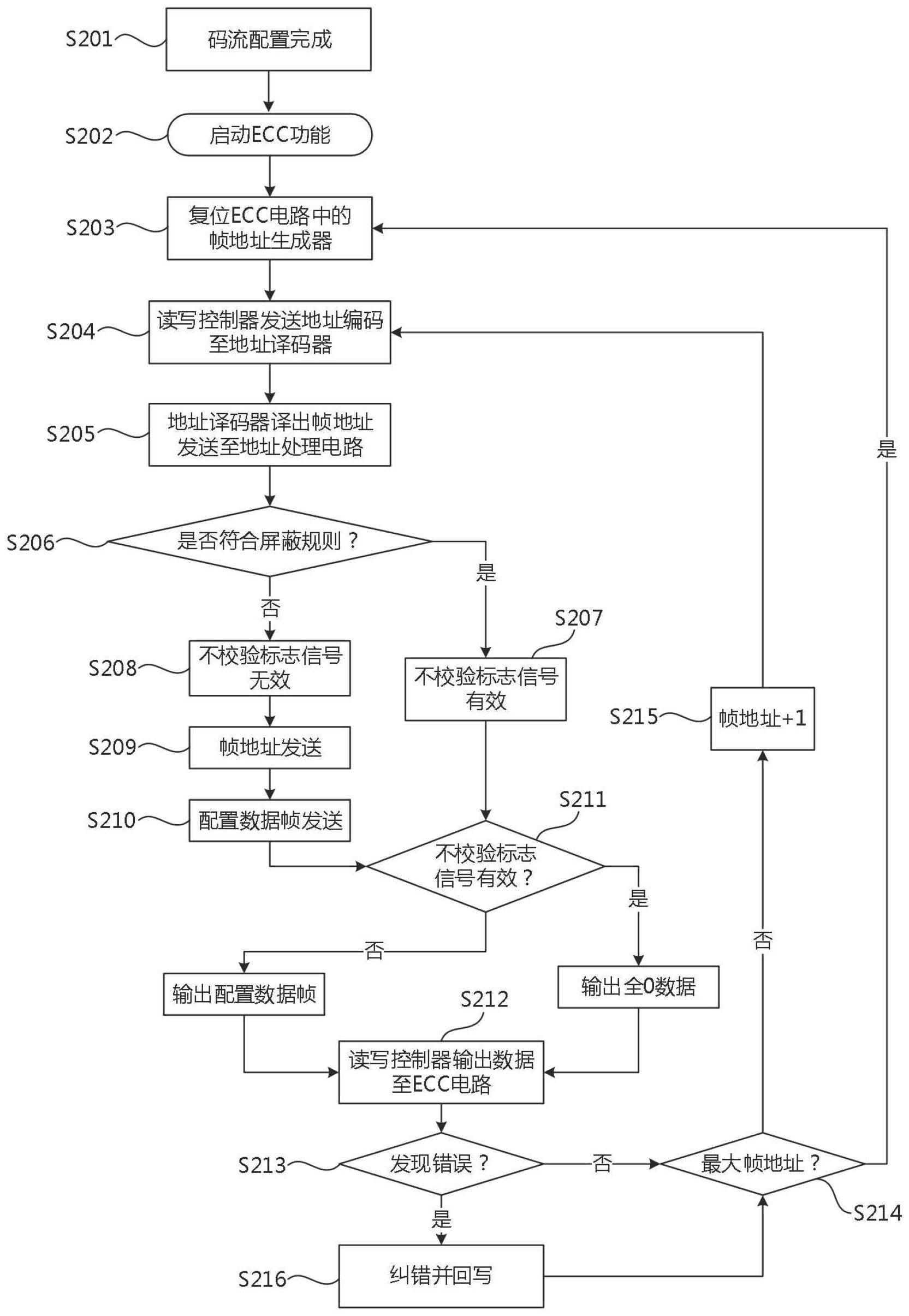

本申请的目的在于提供FPGA单粒子翻转纠错方法及电路、电子设备、计算机可读 存储介质,解决现有的纠错电路在实行ECC操作时,用户必须检查FPGA内的所有帧,不能配 置回读帧数据的地址,可能产生回读数据误报的问题。 本申请的目的采用以下技术方案实现: 第一方面,本申请提供了一种FPGA单粒子翻转纠错方法,所述方法包括:检测配置 数据帧地址是否是不需要ECC校验的帧地址;若所述配置数据帧地址是不需要ECC校验的帧 地址,则不对所述配置数据帧地址对应的配置数据帧进行ECC校验;若所述配置数据帧地址 不是不需要ECC校验的帧地址,则对所述配置数据帧地址对应的配置数据帧进行ECC校验。 该技术方案的有益效果在于,在SEU纠错过程中,用户可以配置不需要ECC校验的帧地址,例 如可以将容易产生误报的帧地址配置为不需要ECC校验,对于不需要校验的帧地址,将不进 行数据回读和ECC校验,增加了ECC校验的灵活性,避免因噪声可能导致的数据误报。 在一些可能的实现方式中,所述检测配置数据帧地址是否是不需要ECC校验的帧 地址,包括:检测所述配置数据帧地址是否符合屏蔽规则;若所述配置数据帧地址符合所述 屏蔽规则,则判断所述配置数据帧地址是不需要ECC校验的帧地址;若所述配置数据帧地址 不符合所述屏蔽规则,则判断所述配置数据帧地址是需要ECC校验的帧地址。该技术方案的 有益效果在于,通过配置数据帧地址是否符合屏蔽规则来检测不需要ECC校验的帧地址。 在一些可能的实现方式中,所述检测配置数据帧地址是否是不需要ECC校验的帧 地址,包括:检测所述配置数据帧地址是否符合屏蔽规则;所述若所述配置数据帧地址是不 需要ECC校验的帧地址,则不对所述配置数据帧地址对应的配置数据帧进行ECC校验,包括: 若所述配置数据帧地址符合所述屏蔽规则,则不对所述配置数据帧地址对应的配置数据帧 进行ECC校验;所述若所述配置数据帧地址不是不需要ECC校验的帧地址,则对所述配置数 据帧地址对应的配置数据帧进行ECC校验,包括:若所述配置数据帧地址不符合所述屏蔽规 则,则对所述配置数据帧地址对应的配置数据帧进行ECC校验。该技术方案的有益效果在 于,通过配置数据帧地址是否符合屏蔽规则来确定是否屏蔽对配置数据帧的ECC校验。 在一些可能的实现方式中,所述方法还包括:接收用户配置的屏蔽规则,所述屏蔽 规则包括屏蔽标识位,所述屏蔽标识位的位数是1位或多位。该技术方案的有益效果在于, 用户可自行设定1位或多位的屏蔽标识位,避免单一屏蔽标识位受到干扰失效,导致判定错 误情况的发生。其中,屏蔽标识位在物理位置上可以相邻、也可以隔开,隔开方案可以降低 屏蔽标识位同时多位出错的概率,提高可靠性。 在一些可能的实现方式中,所述若所述配置数据帧地址是不需要ECC校验的帧地 址,则不对所述配置数据帧地址对应的配置数据帧进行ECC校验,包括:若所述配置数据帧 地址是不需要ECC校验的帧地址,则产生不校验标志信号且使所述不校验标志信号处于第 一状态,不对所述配置数据帧地址对应的配置数据帧进行回读和ECC校验;所述若所述配置 数据帧地址不是不需要ECC校验的帧地址,则对所述配置数据帧地址对应的配置数据帧进 行ECC校验,包括:若所述配置数据帧地址不是不需要ECC校验的帧地址,则产生不校验标志 6 CN 111597073 A 说 明 书 3/9 页 信号且使所述不校验标志信号处于第二状态,回读所述配置数据帧地址对应的配置数据 帧,对回读的配置数据帧进行纠错。该技术方案的有益效果在于,通过产生不校验标志信 号,使其处于第一状态或第二状态,来确定是否对配置数据帧地址对应的配置数据帧进行 回读和ECC校验。 在一些可能的实现方式中,所述若所述配置数据帧地址是不需要ECC校验的帧地 址,则产生不校验标志信号且使所述不校验标志信号处于第一状态,不对所述配置数据帧 地址对应的配置数据帧进行回读和ECC校验,包括:若所述配置数据帧地址是不需要ECC校 验的帧地址,则产生不校验标志信号且使所述不校验标志信号处于第一状态,产生全0的回 读数据,对所述全0的回读数据进行纠错。该技术方案的有益效果在于,当配置数据帧地址 对应的配置数据帧不需要ECC校验时,产生全0的回读数据以执行对回读数据的纠错步骤, 简化纠错电路的运行逻辑,使纠错电路结构更紧凑,由于对全0的数据进行纠错所需处理时 间很少,不会影响纠错电路的工作效率。 第二方面,本申请提供了一种FPGA单粒子翻转纠错电路,所述FPGA单粒子翻转纠 错电路包括地址处理电路和纠错状态控制器;所述地址处理电路用于检测配置数据帧地址 是否是不需要ECC校验的帧地址;所述纠错状态控制器用于若所述配置数据帧地址是不需 要ECC校验的帧地址,则不对所述配置数据帧地址对应的配置数据帧进行ECC校验;若所述 配置数据帧地址不是不需要ECC校验的帧地址,则对所述配置数据帧地址对应的配置数据 帧进行ECC校验。 在一些可能的实现方式中,所述地址处理电路用于检测所述配置数据帧地址是否 符合屏蔽规则;所述纠错状态控制器用于若所述配置数据帧地址符合所述屏蔽规则,则不 对所述配置数据帧地址对应的配置数据帧进行ECC校验;若所述配置数据帧地址不符合所 述屏蔽规则,则对所述配置数据帧地址对应的配置数据帧进行ECC校验。 在一些可能的实现方式中,所述FPGA单粒子翻转纠错电路还包括配置存储单元、 读写控制器、ECC电路、回读数据发生器、地址译码器和数据选择器;所述配置存储单元用于 存储所述配置数据帧和所述屏蔽规则,以及向所述地址处理电路发送所述屏蔽规则;所述 读写控制器用于受所述纠错状态控制器控制,向所述地址译码器发送帧地址编码;所述地 址译码器用于获取所述帧地址编码对应的配置数据帧地址并发送至所述地址处理器;所述 地址处理电路用于检测所述配置数据帧地址是否符合所述屏蔽规则;若符合则产生不校验 标志信号且使所述不校验标志信号处于第一状态,并将第一状态的不校验标志信号发送至 所述数据选择器;若不符合则产生不校验标志信号且使所述不校验标志信号处于第二状 态,并将第二状态的不校验标志信号发送至所述数据选择器和所述地址译码器;所述地址 译码器还用于在接收到所述第二状态的不校验标志信号后将所述配置数据帧地址发送至 所述配置存储单元;所述配置存储单元还用于将所述配置数据帧地址对应的配置数据帧发 送至所述数据选择器;所述数据选择器用于在接收到所述第一状态的不校验标志信号后将 所述回读数据发生器产生的全0的回读数据发送至所述读写控制器,在接收到所述第二状 态的不校验标志信号后将所述配置数据帧发送至所述读写控制器;所述读写控制器还用于 将所述全0的回读数据和所述配置数据帧发送至所述ECC电路;所述ECC电路用于受所述纠 错状态控制器控制,对所述全0的回读数据和所述配置数据帧地址对应的配置数据帧进行 纠错。 7 CN 111597073 A 说 明 书 4/9 页 在一些可能的实现方式中,所述屏蔽规则包括屏蔽标识位及其位置信息,所述屏 蔽标识位的位置信息用于指示所述屏蔽标识位在所述配置数据帧地址中的位置,所述屏蔽 标识位的位数是1位或多位。该技术方案的有益效果在于,用户可以根据实际应用中的需求 灵活地配置屏蔽标识位及其位置信息,避免单一屏蔽标识位受到干扰失效,导致判定错误 的情况发生。 第三方面,本申请提供了一种电子设备,包括存储器和处理器,所述存储器存储有 计算机程序,所述处理器执行所述计算机程序时实现上述任一项方法的步骤。 第四方面,本申请提供了一种计算机可读存储介质,存储有计算机程序,所述计算 机程序被处理器执行时实现上述任一项方法的步骤。 与现有技术相比,本申请的有益效果包括: 本申请公开了FPGA单粒子翻转纠错方法及电路、电子设备、计算机可读存储介质, 在SEU纠错过程中,用户可以配置不需要ECC校验的帧地址,例如可以将容易产生误报的帧 地址配置为不需要ECC校验,对于不需要校验的帧地址,将不进行数据回读和ECC校验,增加 了ECC校验的灵活性,避免因噪声可能导致的数据误报。 附图说明 下面结合附图和实施例对本申请进一步说明。 图1是本申请实施例提供的一种FPGA单粒子翻转纠错方法的流程示意图; 图2是本申请实施例提供的一种FPGA单粒子翻转纠错方法的流程示意图; 图3是本申请实施例提供的一种FPGA单粒子翻转纠错方法的流程示意图; 图4是本申请实施例提供的一种FPGA单粒子翻转纠错电路的结构示意图; 图5是本申请实施例提供的一种配置数据帧的结构示意图; 图6是本申请实施例提供的一种FPGA单粒子翻转纠错方法的流程示意图; 图7是本申请实施例提供的一种电子设备的结构示意图。