技术摘要:

本申请提供一种滤波电路、信号处理设备和制造方法。其中,滤波电路包括:多个谐振器,所述多个谐振器中的部分谐振器设置于第一晶圆上,所述多个谐振器中的剩余部分谐振器设置于第二晶圆上,所述第一晶圆与所述第二晶圆之间设置有连接部件。通过将多个谐振器中的部分谐 全部

背景技术:

近年来,随着市场的迅猛发展,无线通讯终端和设备不断朝着小型化、多模-多频 段的方向发展,无线通讯终端和设备不断朝着小型化,多模-多频段的方向发展,无线通信 终端中的用于FDD(频分复用双工)的双工器的数量也随之增加。五模十三频,甚至五模十七 频逐渐成为主流手机的标准要求,特别是随着5G商用的临近,对高性能、小尺寸的滤波器和 双工器的需求量也越来越大。 现有技术中为达到缩小尺寸的目的,是在一片晶圆上实现制造宽带滤波器,所有 谐振器都只能用同一种压电层材料实现,这样串、并联位置谐振器的机电耦合系数基本相 当,不会相差太多(如0.5%以上)。如果从保证滤波器带宽和插入损耗的方向考虑,需要尽 量加大谐振器的机电耦合系数;而如果为了保证该滤波器与低频侧共存频段的相互抑制考 虑,则需要减少并联谐振的机电耦合系数。并且现有技术中为了改善滚降,在并联谐振器上 添加质量负载来实现并联谐振器的fp远低于串联谐振器的fs,但是当质量负载加的较大 时,谐振器的Q值势必会有恶化趋势。 因此,如何在达到更好的滚降特性的同时,将滤波器尺寸做小,成为滤波器设计工 程师亟待解决的问题。

技术实现要素:

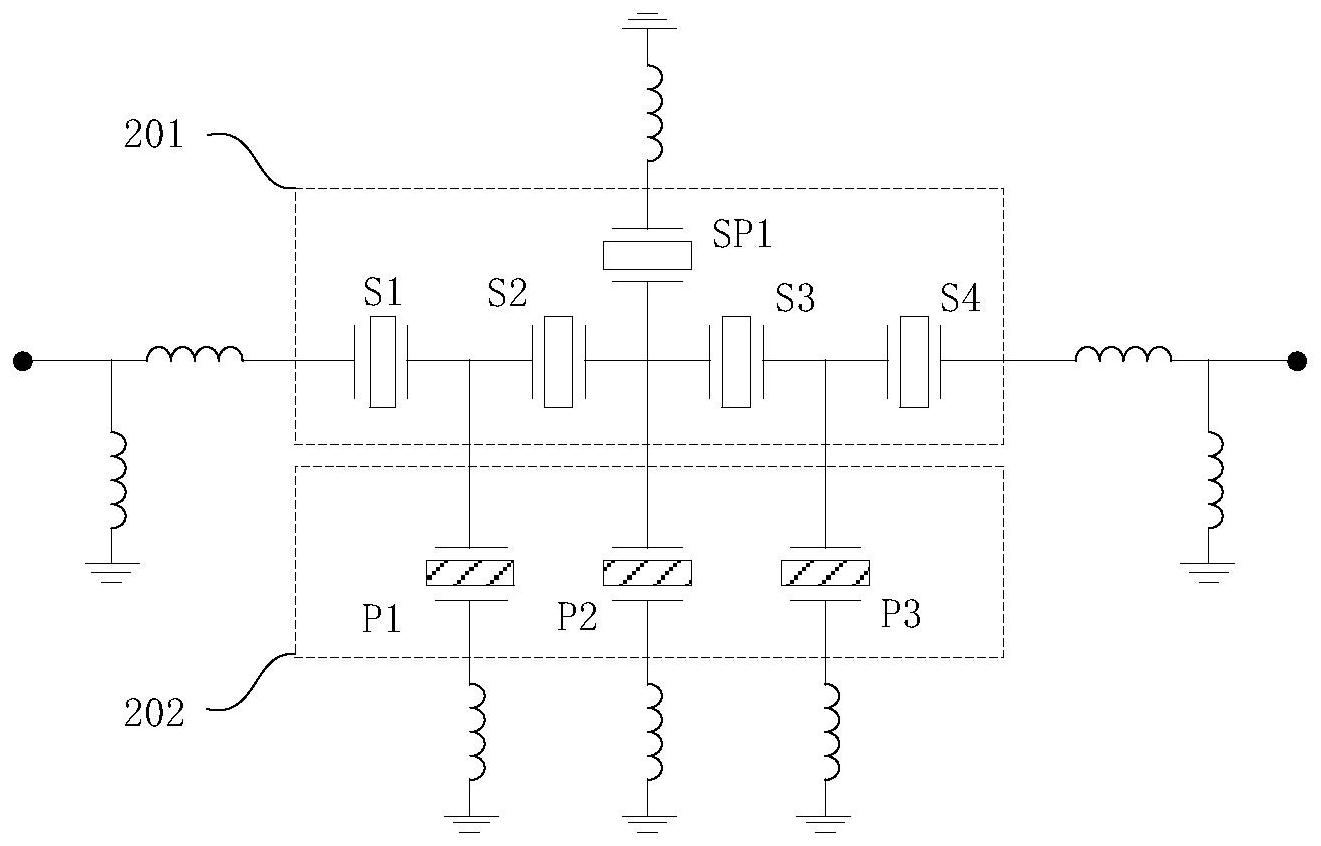

有鉴于此,本申请提供一种滤波电路、信号处理设备及制造所述滤波电路的方法。 具体地,本申请是通过如下技术方案实现的: 第一方面,本申请实施例中提供了一种滤波电路,包括:多个谐振器,所述多个谐 振器中的部分谐振器设置于第一晶圆上,所述多个谐振器中的剩余部分谐振器设置于第二 晶圆上,所述第一晶圆与所述第二晶圆之间设置有连接部件。 可选地,所述多个谐振器包括:第一数量的串联连接的第一谐振器、第二数量的第 二谐振器和带宽调节器件,每一个所述第二谐振器都连接在一个所述第一谐振器的一端和 接地点之间;所述多个第一谐振器和所述宽带调节器件设置于第一晶圆上,所述多个第二 谐振器设置于第二晶圆上。 可选地,所述带宽调节器件包括:至少一个第三谐振器和与所述第三谐振器数量 相等的电感,所述第三谐振器连接在任意两个所述第一谐振器之间的节点和所述电感的一 端,所述电感的另一端连接接地点,所述多个第一谐振器和所述第三谐振器设置于第一晶 圆上。 可选地,所述带宽调节器件包括:两个第三谐振器和一个电感,所述两个第三谐振 器的输出端均与所述电感的输入端相连接,所述两个第三谐振器的输入端分别连接至两个 4 CN 111600565 A 说 明 书 2/7 页 第一谐振器连接点上,所述电感的输出端连接接地点,所述多个第一谐振器和所述第三谐 振器设置于所述第一晶圆上。 可选地,所述带宽调节器件包括:一个电感,所述电感的输出端连接接地点,所述 电感的输入端通过导线连接至任意两个第一谐振器连接点,所述多个第一谐振器和所述导 线设置于所述第一晶圆上。 可选地,所述连接部件包括:设置于所述第一晶圆与所述第二晶圆之间的若干个 键合区。 第二方面,本申请实施例中提供了一种信号处理设备,包括:信号输入电路、信号 输出电路和如第一方面所述的滤波电路;所述信号输入电路与所述滤波电路相连接,所述 滤波电路与所述信号输出电路相连接。 第三方面,本申请实施例中提供了一种滤波电路制造的方法,所述滤波电路,包 括:多个谐振器,所述方法包括: 设置所述多个谐振器中的部分谐振器于第一晶圆上,设置所述多个谐振器中的剩 余部分谐振器设于第二晶圆上,在所述第一晶圆与所述第二晶圆之间设置连接部件。 可选地,所述多个谐振器包括:第一数量的串联连接的第一谐振器、第二数量的第 二谐振器和带宽调节器件,每一个所述第二谐振器都连接在一个所述第一谐振器的一端和 接地点之间; 所述设置所述多个谐振器中的部分谐振器于第一晶圆上,设置所述多个谐振器中 的剩余部分谐振器设于第二晶圆上,包括: 设置所述多个第一谐振器和所述宽带调节器件于第一晶圆上,设置所述多个第二 谐振器于第二晶圆上。 可选地,所述带宽调节器件包括:至少一个第三谐振器和与所述第三谐振器数量 相等的电感,所述第三谐振器连接在任意两个所述第一谐振器之间的节点和所述电感的一 端,所述电感的另一端连接接地点;所述设置多个第一谐振器和所述宽带调节器件于第一 晶圆上,包括: 设置所述多个第一谐振器和所述第三谐振器于第一晶圆上。 可选地,所述带宽调节器件包括:两个第三谐振器和一个电感,所述两个第三谐振 器的输出端均与所述电感的输入端相连接,所述两个第三谐振器的输入端分别连接至两个 第一谐振器连接点上,所述电感的输出端连接接地点; 所述设置多个第一谐振器和所述宽带调节器件于第一晶圆上,包括: 设置所述多个第一谐振器和所述第三谐振器于所述第一晶圆上。 可选地,所述带宽调节器件包括:一个电感,所述电感的输出端连接接地点,所述 电感的输入端通过导线连接至任意两个第一谐振器连接点; 所述设置多个第一谐振器和所述宽带调节器件于第一晶圆上,包括: 设置所述多个第一谐振器和所述导线于所述第一晶圆上。 可选地,所述在所述第一晶圆与所述第二晶圆之间设置连接部件,包括: 在所述第一晶圆与所述第二晶圆之间设置若干个键合区。 本申请实施例所提供的一种滤波电路、信号处理设备及滤波电路制造的方法,通 过将多个谐振器中的部分谐振器设置于第一晶圆上,将剩余部分谐振器设置于第二晶圆 5 CN 111600565 A 说 明 书 3/7 页 上,具有以下积极效果:缩小了芯片尺寸,实现小型化;能够允许把并联位置的谐振器kt做 小,实现左侧更好的滚降特性,保证了谐振器的性能。 附图说明 图1是现有技术中的一种滤波电路的结构示意图。 图2是上述图1所示的滤波电路的侧视图; 图3是现有技术中的上述图1所示的滤波电路的阻抗示意图; 图4是本申请的一个实施例中提供的滤波电路的结构示意图; 图5是上图4所示的滤波电路的侧视图; 图6是上图4所示的滤波电路的两个晶圆的仰视图; 图7a是上图4所示的滤波电路的幅频特性曲线示意图; 图7b是图4所示的滤波电路的通带曲线示意图; 图8为本申请一实施例中提供的滤波电路的结构示意图; 图9为本申请又一实施例提供的一种滤波电路的结构示意图; 图10为本申请又一实施例提供的一种滤波电路的结构示意图。 图11(a)和图11(b)为BAW的电学符号及等效电学模型图; 图12为谐振器阻抗与fs、fp的关系示意图。