技术摘要:

本发明提供一种芯片验证方法、装置及存储介质。上位机根据测量配置请求下发对待检测芯片的测试指令,待检测芯片根据测试指令对多个测试模块进行测试,并将多个测试模块对应的输出信号发送至通用验证平台,通用验证平台对多个输出信号进行信号分析得到待检测芯片的多个 全部

背景技术:

SoC(System-on-a-Chip)芯片是一种集成电路的芯片,可以有效地降低电子或信 息系统产品的开发成本,缩短开发周期,提高产品的竞争力,是未来工业界将采用的最主要 的产品开发方式。SoC芯片在生产过程中需要对SoC芯片进行测试,随着SoC芯片的规模越来 越大以及外设接口的复杂性,SoC芯片的验证也越来越复杂和耗时。 目前的SoC芯片软件验证方法通常是由C、C 等软件语言编码后经过编译器编译 链接生成可执行程序,手动操作通过下载接口将可执行程序存放到SoC芯片的程序存储器 中,SoC芯片复位后中央处理器从程序存储器中读取指令并执行,外设则需要配合外部的信 号激励和信号分析,最终以完成对芯片所设计功能的验证。 随着SoC芯片功能越来越复杂以及外设的多样性,软件测试代码生成的可执行程 序的执行空间需求会增大,在不增加SoC芯片程序存储器空间的情况下,需要将可执行程序 拆分成多个分别下载执行;同时芯片外设如USB、SPI、UART等IP测试请求会增多,通常的做 法是用信号发生器去做激励,用示波器去做信号分析,很多地方都需要人为去操作。传统的 软件验证方法在这两者的基础上需要的验证时间将大大增加。

技术实现要素:

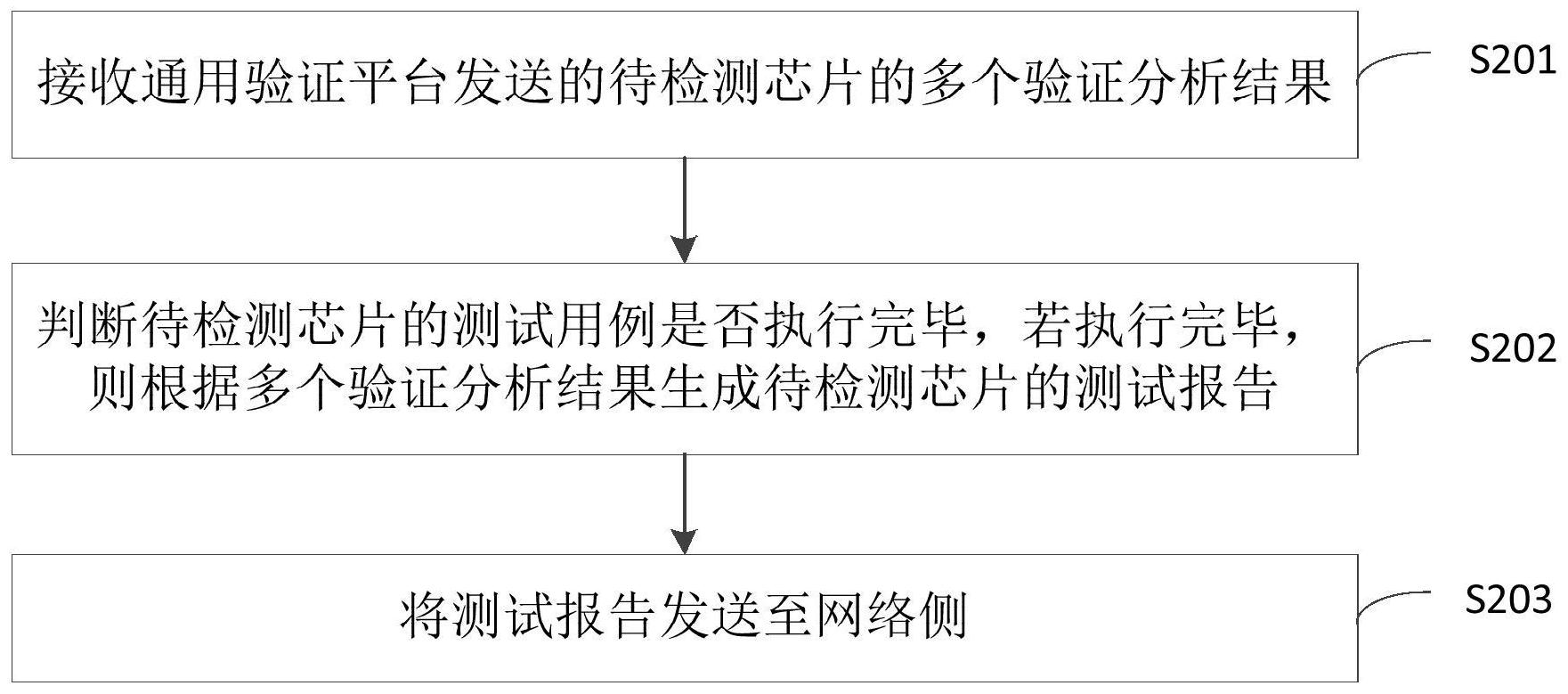

本发明实施例提供一种芯片验证方法、装置及存储介质,以提高芯片的验证效率。 为达到上述目的,本发明提供如下技术方案: 本发明的第一方面提供一种芯片验证方法,包括: 接收通用验证平台发送的待检测芯片的多个验证分析结果; 判断所述待检测芯片的测试用例是否执行完毕,若执行完毕,则根据所述多个验 证分析结果生成所述待检测芯片的测试报告; 将所述测试报告发送至网络侧。 在一种可能的实现方式中,所述接收通用验证平台发送的待检测芯片的多个验证 分析结果之前,所述方法还包括: 获取所述待检测芯片的测试配置请求,所述测试配置请求包括所述待检测芯片的 型号、测试模块以及测试用例序列号; 根据所述测试配置请求向所述待检测芯片发送多个测试指令。 在一种可能的实现方式中,所述获取所述待检测芯片的测试配置请求之后,所述 方法还包括: 根据测量配置请求向所述通用验证平台发送所述待检测芯片对应的验证分析指 令。 4 CN 111579959 A 说 明 书 2/12 页 在一种可能的实现方式中,所述测试模块包括内部模块和/或外设模块;所述测试 指令用于指示对所述内部模块和/或所述外设模块进行测试。 在一种可能的实现方式中,若所述待检测芯片的数量为多个,所述测试配置请求 还包括多个待检测芯片的测试的执行顺序。 本发明的第二方面提供一种芯片验证方法,包括: 接收待检测芯片发送的多个输出信号;所述多个输出信号通过多线程通道并行输 出; 根据所述多个输出信号生成所述待检测芯片的多个验证分析结果,将所述多个验 证分析结果发送至上位机。 在一种可能的实现方式中,所述接收待检测芯片发送的多个输出信号之前,所述 方法还包括: 获取所述上位机发送的所述待检测芯片对应的验证分析指令; 所述根据所述多个输出信号生成所述待检测芯片的多个验证分析结果,将所述多 个验证分析结果发送至上位机,包括: 根据所述多个输出信号和所述验证分析指令生成所述待检测芯片的多个验证分 析结果,将所述多个验证分析结果发送至所述上位机。 在一种可能的实现方式中,所述待检测芯片的测试模块包括内部模块和/或外设 模块;若对所述待检测芯片的测试包括对所述外设模块的测试,所述方法还包括; 向所述待检测芯片的所述外设模块发送激励信号。 本发明的第三方面提供一种上位机,包括: 接收模块,用于接收通用验证平台发送的待检测芯片的多个验证分析结果; 判断模块,用于判断所述待检测芯片的测试用例是否执行完毕,若执行完毕,则生 成模块,用于根据所述多个验证分析结果生成所述待检测芯片的测试报告; 发送模块,用于将所述测试报告发送至网络侧。 本发明的第四方面提供一种通用验证平台,包括: 接收模块,用于接收待检测芯片发送的多个输出信号;所述多个输出信号通过多 线程通道并行输出; 生成模块,用于根据所述多个输出信号生成所述待检测芯片的多个验证分析结 果,发送模块,用于将所述多个验证分析结果发送至上位机。 本发明的第五方面提供一种上位机,包括: 存储器; 处理器;以及 计算机程序; 其中,所述计算机程序存储在所述存储器中,并被配置为由所述处理器执行以实 现如本发明第一方面任一项所述的芯片验证方法。 本发明的第六方面提供一种通用验证平台,包括: 存储器; 处理器;以及 计算机程序; 5 CN 111579959 A 说 明 书 3/12 页 其中,所述计算机程序存储在所述存储器中,并被配置为由所述处理器执行以实 现如本发明第二方面任一项所述的芯片验证方法。 本发明的第七方面提供一种计算机可读存储介质,其上存储有计算机程序,所述 计算机程序被处理器执行以实现如本发明第一方面任一项或本发明第二方面任一项所述 的芯片验证方法。 本发明实施例提供一种芯片验证方法、装置及存储介质。上位机根据测量配置请 求下发对待检测芯片的测试指令,待检测芯片根据测试指令对多个测试模块进行测试,并 将多个测试模块对应的输出信号发送至通用验证平台,通用验证平台对多个输出信号进行 信号分析得到待检测芯片的多个验证分析结果,上位机根据多个验证分析结果自动生成待 检测芯片的测试报告,最终将测试报告发送至网络侧。本实施例提供的方法实现对待检测 芯片的测试结果的自动化统计以及网络共享,同时,提高了芯片的验证效率。 附图说明 为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现 有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是示 例性的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以 根据这些附图获得其他的附图。 图1为本发明一实施例提供的芯片验证系统的连接示意图; 图2为本发明一实施例提供的芯片验证方法的流程示意图; 图3为本发明另一实施例提供的芯片验证方法的流程示意图; 图4为本发明又一实施例提供的芯片验证方法的流程示意图; 图5为本发明再一实施例提供的芯片验证方法的流程示意图; 图6为本发明一实施例提供的芯片验证方法的交互示意图; 图7为本发明实施例提供的上位机的结构示意图一; 图8为本发明实施例提供的上位机的结构示意图二; 图9为本发明实施例提供的通用验证平台的结构示意图一; 图10为本发明实施例提供的通用验证平台的结构示意图二; 图11为本发明实施例提供的芯片的结构示意图; 图12为本发明实施例提供的上位机的硬件结构示意图; 图13为本发明实施例提供的通用验证平台的硬件结构示意图; 图14为本发明实施例提供的芯片的硬件结构示意图。