技术摘要:

基于交替变换脉冲的CMOS图像数据的改进训练方法,涉及CMOS图像数据的训练方法,解决现有CMOS图像数据的训练方法存在随环境温度的变化出现串并转换过程中每次截取的串行数据相对位置不同,进而存在字校正阶段不成功或字校正阶段成功但通道校正不成功等问题,本发明提出 全部

背景技术:

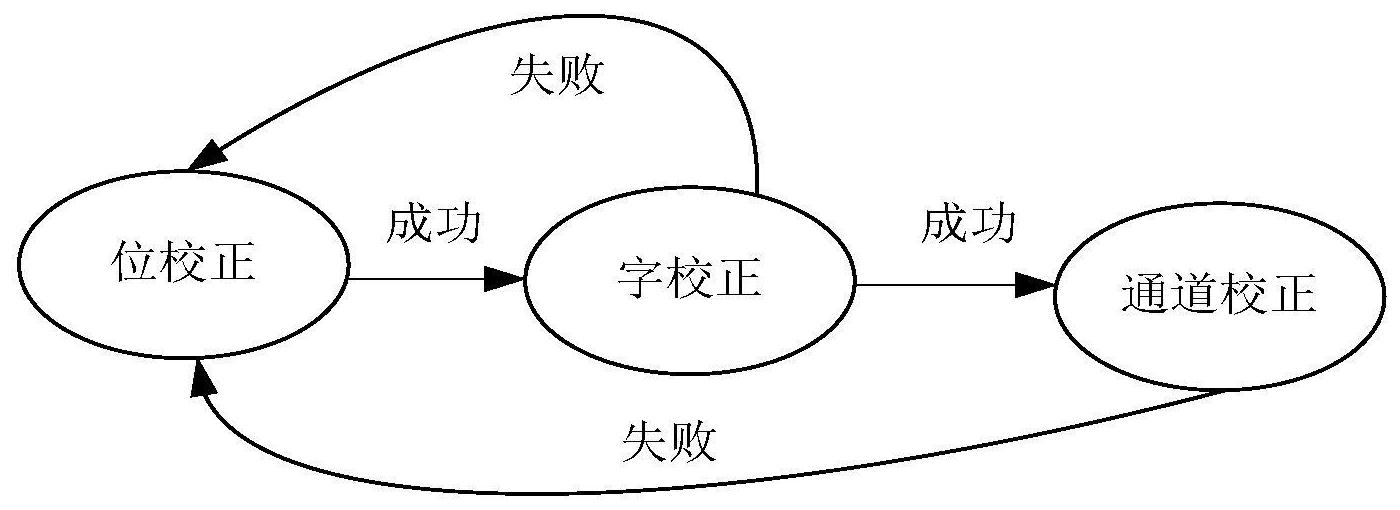

现今高分辨率(不低于10k×10k)高帧频(不低于20fps)的CMOS图像传感器,通常 采用多路(不低于80通道)高速串行通道进行图像数据的传输,各数据传输通道之间在每次 上电无确定的相位关系,给数据的串并转换带来很大的困难。直接采用如virtex 6等内部 集成的ISERDES1模块,也不能满足高位宽应用要求,需要进行进一步的串并转换;可能在字 校正过程中出现错误的数据位置组合得到正确的训练字,而在通道训练过程中无法得到正 确的训练字。例如正确的训练字为AB,经过ISERDES1后得到的并行数据A和B,在进一步的串 并转换后在字校正过程中可能出现的数据组合方式是ABABABABABAB… .,也可能是 BABABABABABA,在此两种组合过程中都包含有正确的训练字AB;而在通道训练过程中对应 单个训练脉冲,前一种组合方式得到的并行数据为…00,00,AB,00,00…,也包含有正确的 训练字AB;而后一种组合方式得到的并行数据为…0,00,0B,A0,00,0…,未包含有正确的训 练字AB,通道训练总会失败。已授权专利名称为一种基于交替变换脉冲的CMOS图像数据的 训练方法,可以解决上述问题,但该技术不能解决随环境温度的变化可能出现串并转换过 程中每次截取的串行数据相对位置不同,出现字校正阶段不成功,或字校正阶段成功但通 道校正不成功等问题。 图1为传统训练算法,通过反复训练反复检测,直到通道训练成功。位校正成功后 进入字校正,如图2,传统训练方法在字校正阶段考虑的组合状态通常仅考虑并行数据位宽 数的并行数据组合状态,并未考虑随温度变化出现的截断位置发生变化的状态,与实际可 能出现的组合状态相差很大,字校正后进入通道校正;若字校正或通道校正失败,重新进入 位校正。若探测器自身的温度变化范围大,在多次的尝试中可能找到正确的组合状态而训 练成功;若探测器的热控措施做得好,而恰好处于非预期的状态,则永远都训练不成功。

技术实现要素:

本发明为解决现有CMOS图像数据的训练方法存在随环境温度的变化出现串并转 换过程中每次截取的串行数据相对位置不同,进而存在字校正阶段不成功或字校正阶段成 功但通道校正不成功等问题,提供一种基于交替变换脉冲的高分辨率高帧频CMOS图像数据 的改进训练方法。 基于交替变换脉冲的高分辨率高帧频CMOS图像数据的改进训练方法,包括位校 正、字校正和通道校正;所述字校正的具体步骤为: 步骤一、对iserdes1输出的p/2位的并行数据data_in首先经过可控的延迟器,当 控制信号bitslip_swap为低电平时输出无延迟,当控制信号bitslip_swap为高电平时输出 有延迟;输出并行数据data_t1相对输入并行数据data_in延迟1/2个像素时钟周期,即:宽 4 CN 111586325 A 说 明 书 2/4 页 度为 p为并行数据的位宽,fclk_io为串行图像数据的DDR伴随时钟频率; 步骤二、位宽为p/2的并行数据data_t1经过1:4的串并转换器转换为位宽为2p的 并行数据data_out_bbuf; 位宽为2p的并行数据data_out_bbuf经过复选器MUX实现p位并行数据data_out的 选择输出,所述选择输出的过程由控制信号bitslip_turn控制;所述控制信号bitslip_ turn的值从1~6循环,对应不同的取值,并行数据data_out选择并行数据data_out_bbuf的 不同位组合输出;具体方式如下: 当控制信号bitslip_turn为1时,选择并行数据data_out_bbuf的p:1位输出;当控 制信号bitslip_turn为2时,选择并行数据data_out_bbuf的3p/2:(p/2 1)位输出;当控制 信号bitslip_turn为3时,选择并行数据data_out_bbuf的2p:(p 1)位输出;当控制信号 bitslip_turn为4时,选择并行数据data_out_bbuf的1:p位输出;当控制信号bitslip_turn 为5时,选择并行数据data_out_bbuf的(p/2 1):3p/2位输出;当控制信号bitslip_turn为6 时,选择并行数据data_out_bbuf的(p 1):2p位输出; 步骤三、设定p个脉冲信号bitslip_pulse为一个循环周期,字校正持续ip次脉冲 信号bitslip_pulse则训练成功,i的范围为:0≤i≤6; 所述脉冲信号bitslip_pulse每经过p/2次,则控制信号bitslip_turn加1,当递增 到6后变为1;每次当脉冲信号bitslip_pulse出现,控制信号bitslip_turn的取值为6时,则 控制信号bitslip_swap取反。 本发明的有益效果: 1、本发明所述的改进训练方法,划分时钟域控制,降低区域时钟的负载,可使系统 工作在更高的频率。 2、本发明所述的改进训练方法中iodelay1的inc管脚恒使能的高电平,减少跨时 钟域的控制信号个数,节约资源。 3、本发明所述的改进训练方法中控制异步FIFO仅在数据训练阶段读写操作有效, 节约能耗。 4、本发明所述的改进训练方法在字校正阶段基于交替变换的训练脉冲,仅选择连 续的地址组合下获得正确的训练字,避免了错误的字组合而导致通道训练失败。 5、本发明所述的改进训练方法通过在并行p/2位的并行数据前加入可选择的移位 寄存器,实现可控的1/2像素时钟周期的延迟,可克服环境温度的变化可能出现串并转换过 程中每次截取的串行数据相对位置不同而出现的训练错误。 附图说明 图1为现有训练方法进行训练的原理图; 图2为传统训练方法在字校正阶段的效果图; 图3为本发明所述的基于交替变换脉冲的高分辨率高帧频CMOS图像数据的改进训 练系统的框图; 图4为本发明所述的基于交替变换脉冲的高分辨率高帧频CMOS图像数据的改进训 练方法中数据校正流程图; 5 CN 111586325 A 说 明 书 3/4 页 图5为本发明所述的基于交替变换脉冲的高分辨率高帧频CMOS图像数据的改进训 练方法中字校正过程的原理图。