技术摘要:

本发明提出一种阵列基板及其制造方法,涉及显示面板领域,阵列基板制造方法包括:S1:在基板上形成栅金属层、覆盖栅金属层的栅极绝缘层以及位于栅极绝缘层上的半导体层;S2:形成位于半导体层上的信号电极层,信号电极层覆盖在部分半导体层上,半导体层具有暴露于信号 全部

背景技术:

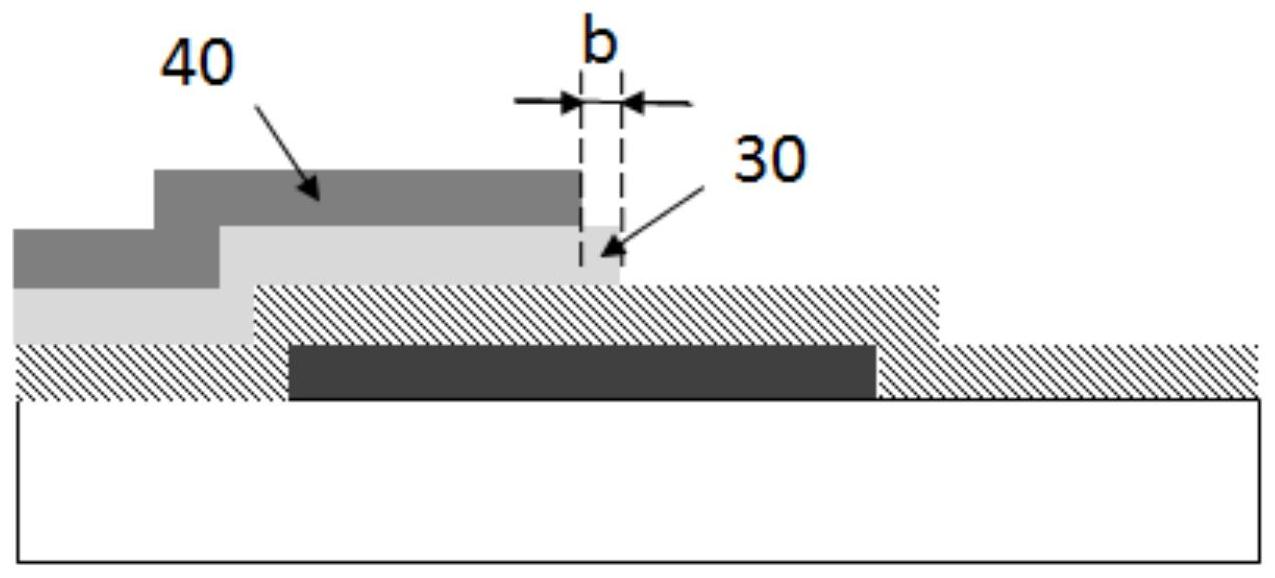

本发明提供一种阵列基板及其制造方法,通过设计并刻蚀掉信号电极层下层露出 的半导体层的边缘部分以消除栅极绝缘层过刻的影响。 本发明的技术方案如下: 本发明公开了一种阵列基板的制造方法,包括以下步骤: S1:在基板上形成栅金属层、覆盖栅金属层的栅极绝缘层以及位于栅极绝缘层上 的半导体层; S2:形成位于半导体层上的信号电极层,信号电极层覆盖在部分半导体层上,半导 体层具有暴露于信号电极层外的边缘部分; S3:在步骤S2的基础上依序沉积无机绝缘层和光阻,通过曝光刻蚀形成位于栅金 属层上的第一开孔以及与第一开孔连通的第二开孔,第二开孔暴露出半导体层的边缘部 分; S4:刻蚀掉暴露出的信号电极层下层露出的半导体层的边缘部分; S5:剥离光阻,形成位于第一开孔和第二开孔内的透明电极层。 优选地,步骤S2形成的所述边缘部分的宽度至少为0.5微米。 优选地,步骤S3中,在刻蚀形成第一开孔时,栅极绝缘层在半导体层的下方形成过 刻区域。4、根据权利要求3所述的阵列基板的制造方法,其特征在于,边缘部分的宽度不小 于过刻区域的宽度。 优选地,部分半导体层层叠在栅金属层上方。 优选地,步骤S4是采用草酸对所述边缘部分进行刻蚀。 优选地,所述半导体层的制作材料为IGZO。 本发明还公开了一种阵列基板,由上述的阵列基板的制造方法制造,包括:基板以 及位于基板上的栅金属层;栅极绝缘层,覆盖栅金属层;设置在栅金属层上的第一开孔;半 导体层,位于栅极绝缘层上且与栅金属层部分重叠;信号电极层,位于半导体层上且与栅金 属层部分重叠;无机绝缘层,覆盖部分信号电极层和栅极绝缘层,所述无机绝缘层在第一开 孔上方以及信号电极层上方设有第二开孔;透明电极层,位于第一开孔和第二开孔内且覆 3 CN 111613575 A 说 明 书 2/4 页 盖部分信号电极层和部分无机绝缘层。 优选地,所述信号电极层通过位于第二开孔内的像素电极与栅金属层接触。 优选地,所述半导体层为IGZO。 本发明能够带来以下至少一项有益效果: 本发明通过在栅金属层和信号电极层之间叠设一层半导体层,并将信号电极层的 图形边缘设计的相比半导体层的图形边缘往里缩至少0.5微米,对半导体层的边缘部分进 行刻蚀以消除栅极绝缘层过刻的影响,也可以防止后续透明电极层桥接时出现电极层的断 裂,减少搭接之处的面积并相应地降低搭接电阻。 附图说明 下面将以明确易懂的方式,结合附图说明优选实施方式,对本发明予以进一步说 明。 图1是本发明阵列基板的制造方法中步骤S1的示意图; 图2是本发明阵列基板的制造方法中步骤S1的部分俯视图; 图3是本发明阵列基板的制造方法中步骤S2的示意图; 图4是本发明阵列基板的制造方法中步骤S2的部分俯视图; 图5是本发明阵列基板的制造方法中步骤S3的示意图; 图6是本发明阵列基板的制造方法中步骤S3完成后的部分俯视图; 图7是本发明阵列基板的制造方法中步骤S4的示意图; 图8是本发明阵列基板的制造方法中步骤S5的示意图; 图9是本发明阵列基板的制造方法中步骤S5完成后的部分俯视图。

技术实现要素:

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对照附图说明 本发明的