技术摘要:

本发明提供了一种抑制dv/dt,di/dt噪音的高压SiC IGBT结构,该改进型半导体结构包括:与阳极欧姆电极接触的P型注入层,与P型注入层上表面接触的N缓冲层,与N缓冲层上表面接触的N‑漂移层,与N‑漂移层上表面接触的电流扩展层;其中,N‑漂移层掺杂浓度目前为目前高压碳 全部

背景技术:

绝缘栅双极型晶体管(Insulated Gate Bipolar Transistor—IGBT),是一种由 功率MOSFET和双极性晶体管组成的双极性器件,其结合了利于简化驱动的MOS栅极结构、并 且具有导通损耗低、开关速度快的优异性能,在传统硅(Si)材料领域已发展较为成熟。碳化 硅(Silicon Carbide,SiC)作为第三代宽禁带半导体材料,相比于硅材料,其具有10倍的击 穿电场、3.3倍的热导率、2倍的饱和载流子漂移速度,被认为是制备高温、高频、高压器件的 理想材料。近年来,高压SiC IGBT的研发成为电力电子器件领域的热点,其有望成为智能电 网、高压直流输电、柔性交流输电等应用领域最具保障性的技术之一。 SiC IGBT简化图如图1所示,一方面由于碳化硅材料中杂质较高的离化能,P 注入 层的不完全离化进一步降低了本征双极性晶体管的电流增益,从而造成关断过程抽取电流 较高、N-漂移层中额外载流子抽取速度较快,使得开关瞬态过程加速;另一方面,由于碳化 硅材料N-漂移层浓度较传统硅材料的高,其漂移区浓度为目前碳化硅高压器件的典型值 1.2~2.2e14cm-2,但是关断过程中漂移层中补充的载流子数量与N-漂移层掺杂浓度相对较 低,从而造成其在关断瞬态过程被较快耗尽而出现穿通效应,使得耗尽层边界从低浓度的 漂移层进入高掺杂浓度的N缓冲层后,其较高的载流子抽取速率会进一步地造成较高的电 压、电流变化速率,即产生严重的dv/dt,di/dt噪声。电路中较高的dv/dt,di/dt噪声不仅造 成电路的过压、过流冲击,还会增加系统额外损耗、降低电能利用效率,使器件开关特性与 系统整体可靠性变差,严重危及电力电子系统长期工作稳定性,大大降低系统运行性能。 中国发明专利,公开号:CN109950302A,公开日:2019.06.28,公开了一种高压SiC IGBT的软穿通结构,属于基本电气元件领域。该结构通过外延生长两个区域或两个以上区 域的缓冲层,并且其浓度从P 注入层至N-漂移层方向呈现递减趋势,但是其漂移区浓度为 目前碳化硅高压器件的典型值~2e14 cm-2,其浓度决定的漂移层电压仍然较低,在关断瞬 态过程还会产生强烈的穿通效应,因而这种结构对dv/dt,di/dt噪声的抑制效果极为有限, 并且由于缓冲层厚度的增大,从而额外增加了正向压降而增大了功率损耗,因此,进一步限 制了该结构的实际应用场合。 三、

技术实现要素:

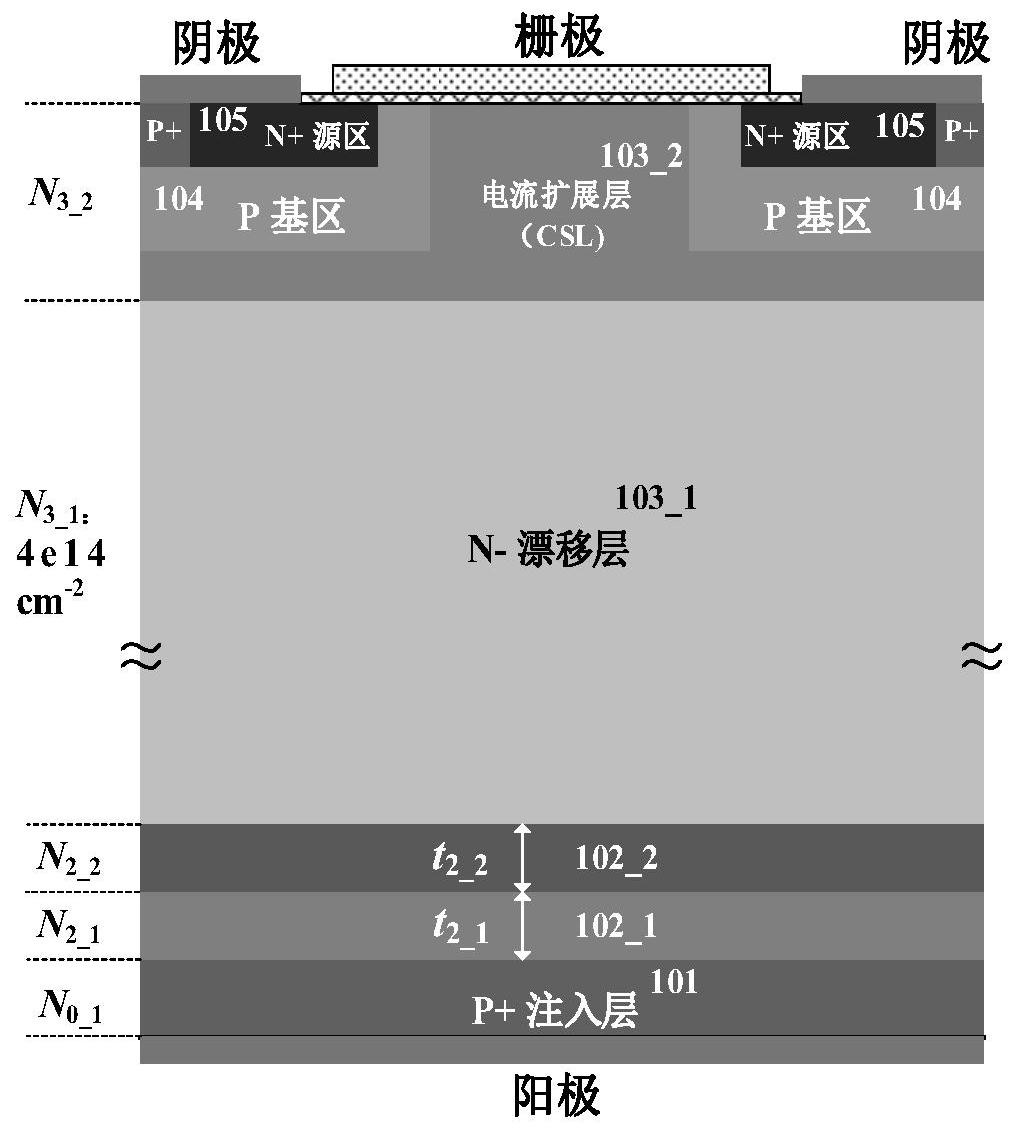

针对现有技术中的缺陷,本发明提供了抑制dv/dt,di/dt噪音产生的高压SiC IGBT的结构,本发明提供的半导体结构能够大幅度抑制漂移层穿通效应的影响,从而大幅 度降低dv/dt,di/dt噪音的产生,同时稳定器件的功率损耗在合适的范围之内。 为解决上述技术问题,本发明提供以下技术方案: 一种抑制dv/dt,di/dt噪音产生的高压SiC IGBT的结构,其原胞结构纵向方向由 3 CN 111599858 A 说 明 书 2/6 页 下至上依次设置:与阳极电极上表面相接触的第一掺杂类型的P 注入层,第二掺杂类型的N 缓冲层,第二掺杂类型的N-漂移层以及第二掺杂类型的电流扩展层(CSL),与CSL上表面相 接触的栅极氧化层;横向方向上,第二掺杂类型的电流扩展层(CSL)两侧设置有第一掺杂类 型的P基区,P基区上表面形成反型层沟道,以及与阴极电极相接触的第二掺杂类型的N 源 区。 优选地,所述第一掺杂类型为P型,第二掺杂类型为N型。 优选地,所述高压SiC IGBT结构为n沟道类型半导体器件。 优选地,所述N-漂移层的掺杂浓度设置为目前高压碳化硅半导体器件典型浓度的 1.2至4倍。 优选地,所述N-漂移层的掺杂浓度所对应的耗尽电压数值接近或等于或高于SiC IGBT器件的工作电压水平。 优选地,所述N缓冲层包含两个或两个以上掺杂浓度不等的区域。 优选地,所述多个区域N缓冲层的掺杂浓度设置为从P 注入层至N-漂移层方向逐 渐增大。 优选地,所述多个区域N缓冲层的掺杂浓度均不低于N-漂移层掺杂浓度的20倍,但 不高于P 注入层的掺杂浓度。 相比现有技术,本发明提供的有益效果: 1)N-漂移层的掺杂浓度设置为目前高压碳化硅半导体器件的1.2至4倍,一方面, 可以增大漂移层完全耗尽所需要的电压数值,从而将耗尽层边界最大程度地限制在低载流 子抽取率的漂移层内,从而大幅度抑制耗尽层边界的扩展速度,最大程度上抑制开关瞬态 所产生的dv/dt,di/dt噪音,另一方面,可以有效降低N-漂移层电阻率,从而降低IGBT的正 向导通压降、导通损耗,进一步提高电能转换效率。 2)N缓冲层包含两个或两个以上掺杂浓度不等的区域,可通过增大高掺杂浓度层 的厚度,控制载流子由P 注入层至N-漂移层的注入效率,避免关断瞬态由过多的额外载流 子抽取而的引起的瞬态时间的延长,从而将功率损耗限制在合适范围内。 3)多个区域N缓冲层的掺杂浓度设置为从P 注入层至N-漂移层方向逐渐增大,进 一步将N-漂移层的额外载流子的注入和运输作用控制在合理的程度,一方面可降低电流拖 尾时间,另一方面有效控制瞬态过程的时间,两方面作用使得功率损耗不会过于明显增加, 从而保证电能转换效率的提升。 附图说明 为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现 有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本发明 的一部分实施例,而不是全部的实施例。对于本领域普通技术人员受其启示,在不脱离本创 造宗旨的情况下,不经创造性的设计出与该技术方案相似的结构方式及实施例,均应属于 本专利的保护范围。 图1是本发明实施例一提供的SiC n沟道IGBT结构的一种结构示意图。 图2是本发明实施例一提供的SiC n沟道IGBT结构的另一种结构示意图。 图3是本发明实施例一所形成SiC n沟道IGBT结构的一种各层掺杂浓度分布趋势 4 CN 111599858 A 说 明 书 3/6 页 与传统高压SiC IGBT对比结果示意图。 图4是本发明实施例一提供的SiC n沟道IGBT结构的dv/dt特性与传统高压SiC IGBT对比结果示意图。 图5是本发明实施例一提供的SiC n沟道IGBT结构di/dt特性与传统高压SiC IGBT 对比结果示意图。 图6是本发明实施例一提供的SiC n沟道IGBT结构正向压降—功率损耗折中特性 与传统高压SiC IGBT对比结果示意图。