技术摘要:

公开了一种半导体器件,包括衬底、位于衬底上的漂移区、位于漂移区上的阱区、位于阱区中的源端掺杂区、位于漂移区上与源端掺杂区相对的漏端掺杂区,以及位于源端和漏端之间的位于阱区位置的栅结构,栅结构在阱区中形成沟道区,源端掺杂区包括掺杂类型相反的第一掺杂区 全部

背景技术:

功率LDMOS(laterally-diffused metal-oxide semiconductor,横向扩散金属氧 化物半导体)通常应用在大电流,大电压的情况下。N型LDMOS器件体内通常包括N 掺杂漏 区、N型漂移区、P阱区、N 掺杂源区和P 掺杂体接触区,其中N 掺杂源区和P 掺杂体接触区 位于P阱区中,在N型LDMOS器件处于反向耐压状态时,由于碰撞电离会产生大量的电子空穴 对,进而产生相应的空穴电流,当该空穴电流由P阱区(p_body)流经至p 体接触区时,P阱区 上的压降会被抬起,由此会可能导致寄生的NPN(N 源端—P阱区—N型漂移区)误开启,器件 出现功能失效。当器件碰撞电离产生空穴越多,寄生的NPN越容易被误开启,所以,对器件的 自防护能力要求越高。

技术实现要素:

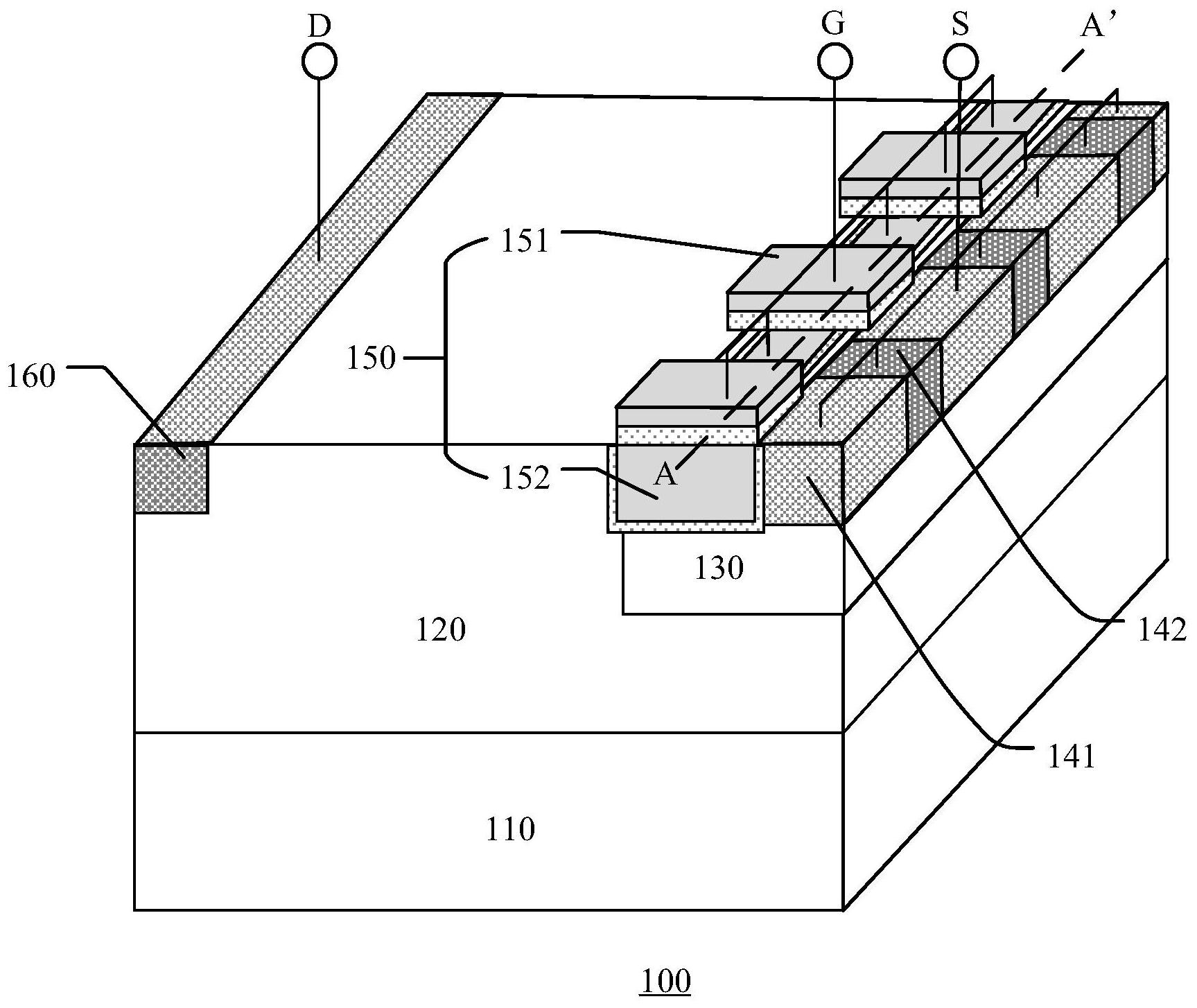

鉴于上述问题,本发明的目的在于提供一种半导体器件,从而提升器件的自防护 能力。 根据本发明的一方面,提供一种半导体器件,其特征在于,包括: 衬底; 漂移区,位于所述衬底上; 漏端掺杂区,位于所述漂移区上表面第一方向的一端; 阱区,位于所述漂移区上表面第一方向与所述漏端掺杂区相反的一端; 源端掺杂区,位于所述阱区中; 栅结构,位于所述阱区位置,在所述阱区至所述漂移区的位置形成沟道区,所述沟 道区的沟道方向为所述漂移区的第一方向,所述沟道区位于所述源端掺杂区与所述漏端掺 杂区之间,且与所述源端掺杂区接触连接;其中, 所述源端掺杂区包括掺杂类型相反的第一掺杂区和第二掺杂区,所述漂移区的掺 杂类型与所述漏端掺杂区的掺杂类型相同,所述第一掺杂区的掺杂类型与所述漏端掺杂区 的掺杂类型相同,所述第一掺杂区与所述第二掺杂区按在所述漂移区上表面与所述第一方 向垂直的第二方向线性分布且交错连接,所述第一掺杂区与所述沟道区对应。 可选地,所述第一掺杂区和所述第二掺杂区的数量均为至少一个。 可选地,所述第一掺杂区的数量至少为两个。 可选地,所述沟道区的沟道宽度与所述第一掺杂区的尺寸相匹配。 可选地,所述栅结构包括: 槽型栅,位于所述阱区中,数量与所述第二掺杂区的数量相匹配。 可选地,所述栅结构还包括: 平面栅,数量与源端第一掺杂区数量匹配,覆盖在所述沟道区上。 3 CN 111584635 A 说 明 书 2/4 页 可选地,还包括: 在所述栅结构与所述源端掺杂区的接触面上,所述槽型栅的图案延伸至所述第一 掺杂区的图案内。 可选地,在所述栅结构与所述源端掺杂区的接触面上,所述第二掺杂区的图案位 于所述槽型栅的图案内,所述第一掺杂区的图案与所述第二掺杂区的图案接触连接。 可选地,所述第一掺杂区为N型掺杂,所述第二掺杂区为P型掺杂。 本发明提供的半导体器件包括衬底、位于衬底上的漂移区、位于漂移区上的阱区、 位于阱区中的源端掺杂区、位于漂移区上与源端掺杂区相对的漏端掺杂区,以及位于源端 和漏端之间的位于阱区位置的栅结构,栅结构在阱区中形成沟道区,源端掺杂区包括掺杂 类型相反的第一掺杂区和第二掺杂区,第一掺杂区的掺杂类型与漏端掺杂区的掺杂类型相 同,沟道区连接第一掺杂区和漂移区。其中,源端的第一掺杂区和第二掺杂区等同靠近栅结 构,降低了第二掺杂区至漂移区与阱区构成的pn结结面的距离,在本发明提供的半导体器 件处于反向耐压状态时,降低了空穴电流在阱区中的从阱区与漂移区形成的pn结结面至源 端第二掺杂区的流通路径,有效缓解了阱区压降的提升,防止第二掺杂区—阱区—漂移区 构成的寄生三极管的误开启,有效地提升了半导体器件的自防护能力。 设置多个沟道区,可以有效地提升电流至漂移区的均匀性,降低漂移区电阻,从而 降低了器件导通压降,提升了器件的电流能力。 槽型栅靠近源端的侧壁完全覆盖源端第二掺杂区侧壁,并与第一掺杂区相接触, 保障沟道区与源端掺杂区的连接。 附图说明 通过以下参照附图对本发明实施例的描述,本发明的上述以及其他目的、特征和 优点将更为清楚,在附图中: 图1示出了根据本发明实施例的半导体器件的整体结构示意图; 图2示出了根据本发明实施例的半导体器件的部分结构示意图; 图3示出了根据图1所示的半导体器件的沿AA’的纵向剖面结构示意图。