技术摘要:

本发明提供一种锁存比较器、与其有关的时钟发生电路和半导体装置。锁存比较器包括第一放大电路、第二放大电路和锁存电路。当半导体装置的操作速度相对较慢时,第一放大电路基于第一输入信号和第二输入信号来改变第一输出节点和第二输出节点的电压电平。当半导体装置的 全部

背景技术:

电子设备包括许多电子元件,并且计算机系统包括很多半导体装置,每个半导体 装置包括半导体。构成计算机系统的半导体装置可以通过接收和发送时钟信号和数据来彼 此通信。半导体装置可以同步于时钟信号来操作。通常,诸如处理器和控制器的主设备可以 通过诸如锁相环电路的时钟发生电路来产生系统时钟信号。诸如存储器件的从设备可以通 过时钟总线接收系统时钟信号,该系统时钟信号通过主设备产生。从设备可以接收系统时 钟信号,并且可以从系统时钟信号产生内部时钟信号。例如,存储器件可以包括内部时钟发 生电路,并且可以从系统时钟信号产生具有各种相位的内部时钟信号。

技术实现要素:

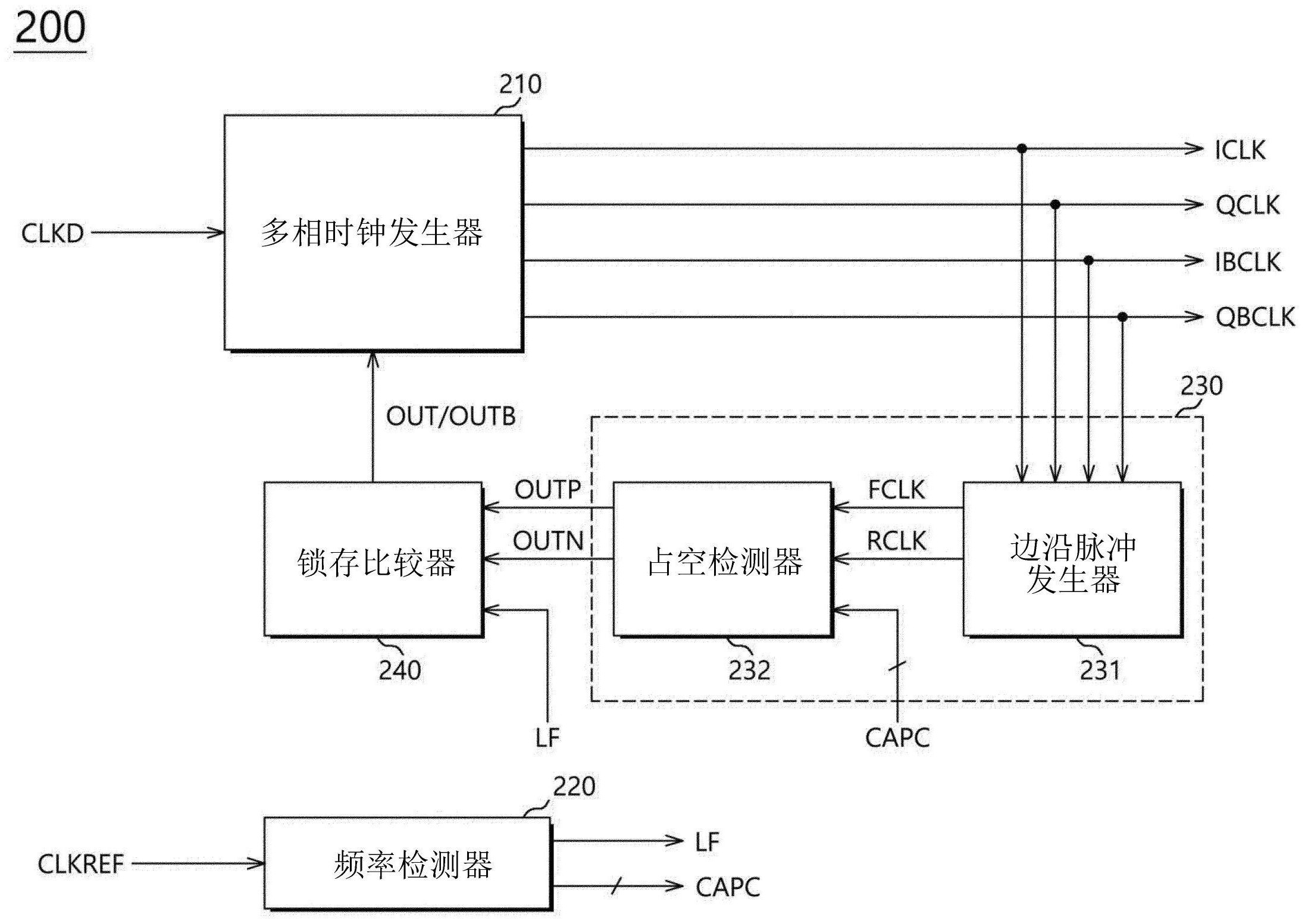

在一个实施例中,一种锁存比较器可以包括第一放大电路、第二放大电路和锁存 电路。第一放大电路可以被配置为基于频率检测信号,通过放大第一输入信号和第二输入 信号将第一输出节点的电压电平和第二输出节点的电压电平之中的一个改变为第一电压 电平。第二放大电路可以被配置为基于所述频率检测信号,通过放大所述第一输入信号和 所述第二输入信号将第三输出节点的电压电平和第四输出节点的电压电平之中的一个改 变为第二电压电平。第二电压电平可以低于第一电压电平。锁存电路可以被配置为基于所 述频率检测信号和第二使能信号,基于第一输出节点的电压电平和第二输出节点的电压电 平来产生第一锁存信号和第二锁存信号,或者基于第三输出节点的电压电平和第四输出节 点的电压电平来产生所述第一锁存信号和第二锁存信号。 在一个实施例中,一种锁存比较器可以包括放大电路和锁存电路。放大电路可以 被配置为:当第一输入信号的电压电平和第二输入信号的电压电平在第一范围内时,基于 所述第一输入信号和所述第二输入信号将第一输出节点的电压电平和第二输出节点的电 压电平之中的一个改变为第一电压电平,以及当所述第一输入信号的电压电平和所述第二 输入信号的电压电平在高于第一范围的第二范围内时,基于所述第一输入信号和所述第二 输入信号将第三输出节点的电压电平和第四输出节点的电压电平之中的一个改变为第二 电压电平。第二电压电平可以低于第一电压电平。锁存电路可以被配置为:当所述第一输入 信号的电压电平和所述第二输入信号的电压电平在第一范围内时,基于第一输出节点的电 压电平和第二输出节点的电压电平来产生第一锁存信号和第二锁存信号,以及当所述第一 7 CN 111585549 A 说 明 书 2/14 页 输入信号的电压电平和所述第二输入信号的电压电平在第二范围内时,基于第三输出节点 的电压电平和第四输出节点的电压电平来产生所述第一锁存信号和第二锁存信号。 在一个实施例中,一种半导体装置可以包括频率检测器、占空检测器、第一放大电 路、第二放大电路和锁存电路。频率检测器可以被配置为通过检测时钟信号的频率来产生 频率检测信号。占空检测器可以被配置为基于至少两个内部时钟信号来产生第一检测信号 和第二检测信号,所述第一检测信号和第二检测信号具有在第一范围和第二范围之中的一 个范围内的电压电平。第一放大电路可以被配置为基于所述频率检测信号,通过放大具有 在第一范围内的电压电平的所述第一检测信号和第二检测信号,来改变第一输出节点的电 压电平和第二输出节点的电压电平。第二放大电路可以被配置为基于所述频率检测信号, 通过放大具有在第二范围内的电压电平的所述第一检测信号和第二检测信号,来改变第三 输出节点的电压电平和第四输出节点的电压电平。锁存电路可以被配置为基于所述频率检 测信号,基于第一输出节点的电压电平和第二输出节点的电压电平来产生第一锁存信号和 第二锁存信号,或者基于第三输出节点的电压电平和第四输出节点的电压电平来产生所述 第一锁存信号和第二锁存信号。 附图说明 图1是示出根据实施例的半导体系统的配置的图。 图2是示出根据实施例的半导体装置内的内部时钟发生电路的配置的图。 图3是示出图2中所示的边沿脉冲发生器的操作的图。 图4是示出图2中所示的占空检测器的配置的图。 图5是示出图4中所示的占空检测器的操作的图。 图6A是示出根据半导体装置的操作速度的第一边沿脉冲信号和第二边沿脉冲信 号的波形的图。 图6B是示出根据图6A中所示的第一边沿脉冲信号和第二边沿脉冲信号的第一检 测信号的电压电平和第二检测信号的电压电平的图。 图7是示出根据实施例的锁存比较器的配置的图。 图8是示出根据实施例的锁存比较器的配置的图。