技术摘要:

提供了一种三维(3D)存储器件,其包括衬底、交替堆叠层和沟道结构。交替堆叠层设置在衬底上,并且,交替堆叠层包括交替堆叠的多个导电层和多个气隙层。沟道结构设置在衬底上,并且垂直延伸穿过导电层和气隙层。交替堆叠层更一步地包括在气隙层和沟道结构之间的多个刻蚀 全部

背景技术:

1、发明领域 本发明涉及三维(3D)存储器件及其制作方法。 2、现有技术描述 通过改进工艺技术,电路设计,编程算法以及制造工艺,可以将平面存储单元缩减 小到更小的尺寸。然而,随着存储单元的特征尺寸接近下限,平面工艺和制造技术变得具有 挑战性并且成本高昂。因此,平面存储单元的存储密度接近上限。 3D存储器结架构可以解决平面存储单元中的密度限制。3D存储架构包括存储器阵 列和用于控制进出存储器阵列的信号的外部器件。如本领域中已知,3D NAND是一种闪存技 术,其垂直地堆叠存储单元以增加容量,从而获得更高的存储密度和更低的每千兆字节成 本。随着3D NAND技术向着高密度和大容量发展,存储单元的数量需要增加,尤其是对从64 层到128层的方案来说。为了更好地刻蚀沟道孔,并且控制工艺成本,应当减小每一个存储 单元的厚度。然而,随着每个存储单元的厚度的不断变薄,相邻存储单元的控制栅之间的耦 合会更严重,从而导致存储器件中更大的RC延迟及编程操作期间存储单元之间的干扰。

技术实现要素:

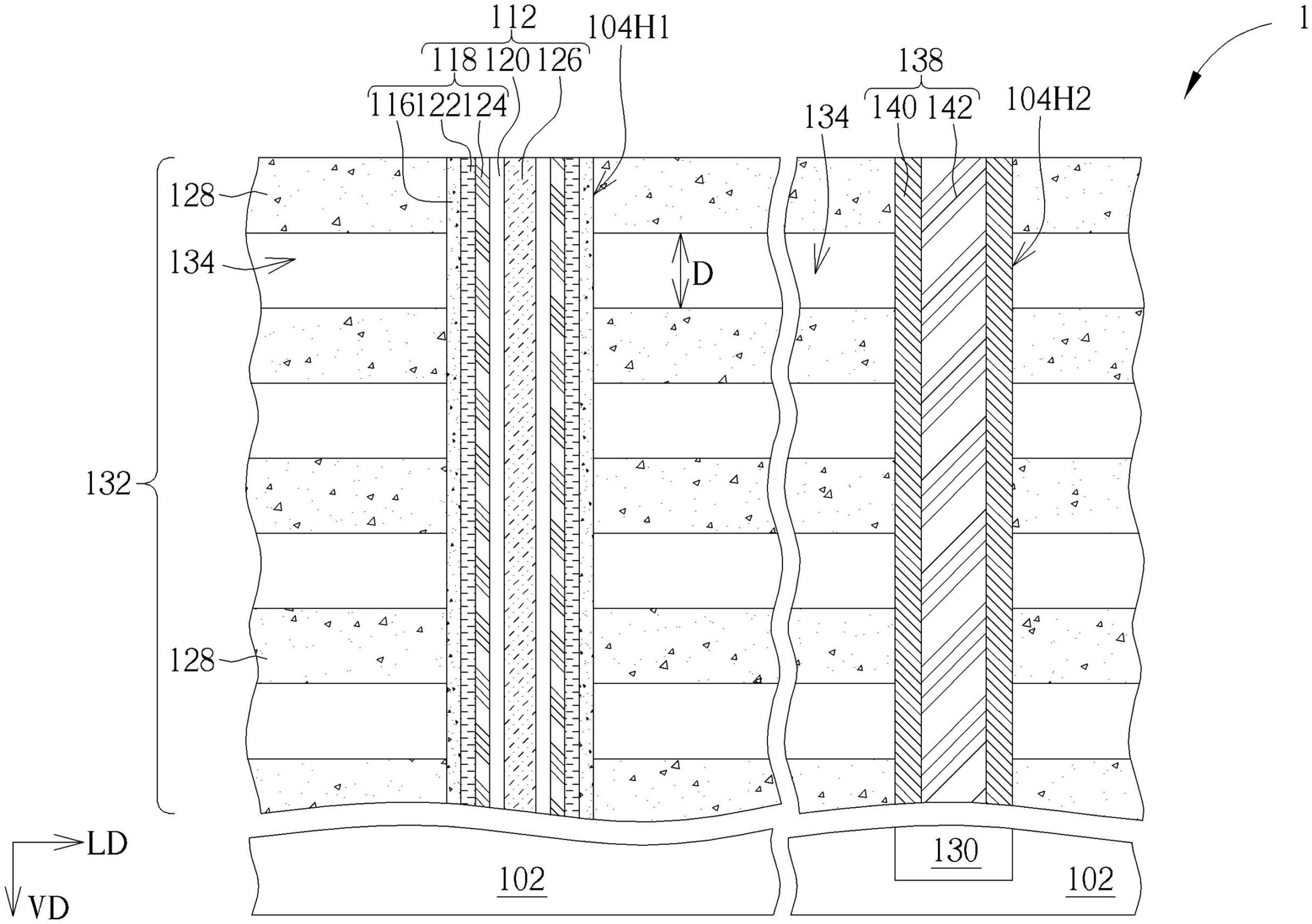

因此,本文公开了三维(3D)存储器件架构及其制作方法的实施例。所公开的结构 和方法提供了许多益处,包括但不限于,容易地控制工艺,减小控制栅之间的耦合电容,以 及,降低编程操作过程中3D存储器件的RC延迟。 在一些实施例中,公开了3D存储器件。该3D存储器件包括衬底,交替堆叠层和沟道 结构。该交替堆叠层设置在衬底上,交替堆叠层包括交替堆叠的多个导电层和多个气隙层。 该沟道结构设置在衬底上,并且垂直延伸穿过导电层和气隙层。该交替堆叠层进一步地包 括在气隙层和沟道结构之间的多个刻蚀停止块。 在一些实施例中,交替堆叠层包括垂直延伸穿过交替堆叠层的沟道孔,并且,沟道 结构包括依次设置在沟道孔侧壁上的阻挡层、存储层、隧穿层和沟道层。 在一些实施例中,沟道结构进一步包括设置在沟道孔中的填充层。 在一些实施例中,刻蚀停止块和阻挡层包含不同的材料。在一些实施例中,阻挡层 直接接触刻蚀停止块。在一些实施例中,刻蚀停止块包括多晶硅。 在一些实施例中,3D存储器件进一步包括垂直延伸穿过交替堆叠层的狭缝结构, 其中,沟道结构,导电层和狭缝结构将气隙层密封。狭缝结构包括绝缘层和触点,并且绝缘 层设置在触点和交替堆叠层之间。 在一些实施例中,公开了3D存储器件的制造方法。首先,在衬底上形成交替电介质 堆叠层,其中,交替电介质堆叠层包括交替堆叠在衬底上的多个第一电介质层和多个第二 电介质层,并且多个第一电介质层和多个第二电介质层包含不同材料。接着,形成垂直穿过 交替电介质堆叠层的沟道孔,并且在沟道孔的侧壁上横向形成多个凹槽。最后,在凹槽内形 成多个刻蚀停止块,然后,在沟道孔中形成沟道结构,并垂直穿过交替电介质堆叠层。然后, 4 CN 111557048 A 说 明 书 2/8 页 将第二电介质层替换为多个导电层。随后,形成多个气隙层,从而,形成交替堆叠层,其中, 交替堆叠层包括交替堆叠的导电层和气隙层,并且,通过至少去除第一电介质层的每一层 的一部分来形成气隙层。 在一些实施例中,刻蚀停止块包含与第一电介质层和第二电介质层不同的材料。 在一些实施例中,刻蚀停止块包括多晶硅。 在一些实施例中,形成刻蚀停止块包括,在凹槽中形成刻蚀停止层,其中,刻蚀停 止层在第二电介质层的每一层的侧壁上延伸;并且,氧化凹槽外部的刻蚀停止层以形成阻 挡层,其中,刻蚀停止层的剩余部分形成刻蚀停止块。 在一些实施例中,形成沟道结构包括在阻挡层上依次形成存储层、遂穿层以及沟 道层。 在一些实施例中,刻蚀停止层和导电层包含不同的材料。 在一些实施例中,形成气隙层包括去除第一电介质层。形成气隙层进一步地包括 去除刻蚀停止层。 在一些实施例中,该方法进一步地包括形成垂直穿过交替电介质堆叠层的狭缝, 其中,用穿过狭缝的导电层替代第二电介质层。 在一些实施例中,该方法进一步地包括在狭缝中形成绝缘层以密封气隙层。该方 法进一步地包括在狭缝中形成触点,其中,绝缘层设置在狭缝与交替堆叠层之间。 在一些实施例中,该方法进一步地包括在形成狭缝猴在衬底上形成一个掺杂区。 在阅读了以下对各附图中示出的优选实施例的详细说明后,本发明的这些和其他 目的无疑地将对本领域的普通技术人员变得显而可见。 附图的简要说明 图1示意性地示出了根据本发明一个实施例的三维(3D)存储器件制造方法的流程 图; 图2-9示意性地示出了根据本发明一个实施例的在图1所示方法中不同步骤处的 示例性结构的截面图; 图10示意性地示出了根据本发明一些实施例的示例性3D存储器件的截面图; 图11示意性地示出了根据本发明一些实施例的示例性3D存储器件的截面图。