技术摘要:

本发明公开了一种基于级联数字控制方法的干扰对消装置及方法,该装置包括数字射频存储分系统、数字控制模拟对消分系统及数字控制数字对消分系统;所述数字射频存储分系统的输入端接收共址干扰信号,对共址干扰信号进行数字化处理,并估计系统延迟匹配误差,进行延迟匹 全部

背景技术:

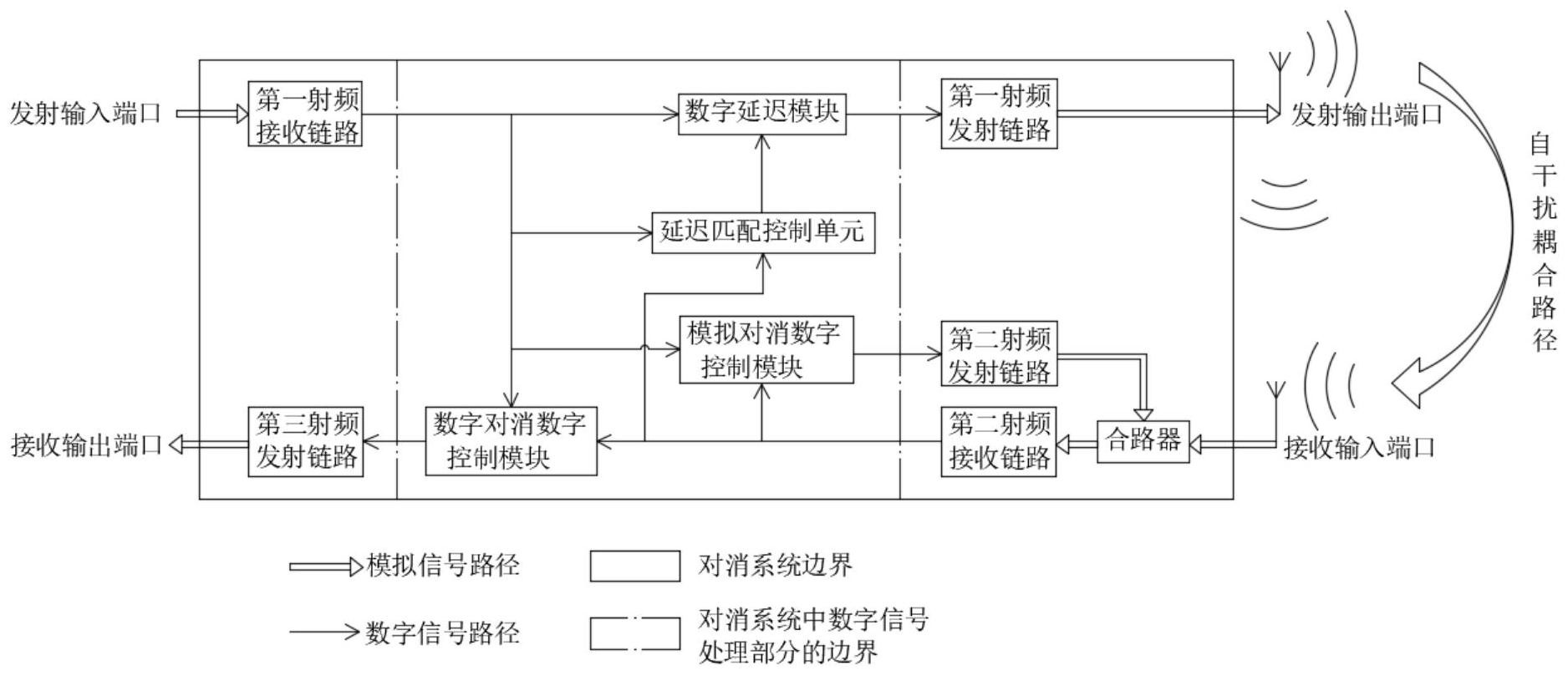

目前,如舰船、飞机、卫星和车辆等现代军用平台上通常密集的部署着多个、多类 射频收发信机;这种射频收发信机通常为通信电台、数据链、雷达、导航与定位系统、电子战 装备、敌我识别系统和侦测设备等。 其中射频收发信机中的射频发信机发出的电磁能往往会通过辐射和传导等方式 耦合到同一平台内的射频收信机上,形成对射频收信机的干扰,这称为共址干扰或自干扰, 共址干扰使射频收信机性能下降甚至失效。 抑制军用平台共址干扰、实现射频收发信机之间的电磁兼容具有迫切的军事需求 及重要的军事意义。 现有技术中,自适应干扰对消技术是抑制共址干扰、实现军用平台射频收发信机 之间电磁兼容的一种有效技术手段;其基本思想为:构建一个与共址干扰信号幅度相同、相 位相反的信号,与干扰信号叠加,从而对干扰信号形成抵消效果。 随着军用平台信息化深入发展,利用自适应干扰对消技术实现军用平台射频收发 信机之间电磁兼容面临新挑战,现有自适应干扰对消技术暴露出以下不足之处:第一,现有 干扰对消系统通常无法介入收发信机的数字基带部分,只能通过射频线缆与收发信机外部 接口进行信号交互;第二,战场电磁环境复杂多变,共址干扰的干扰源和传播特性常常具有 快速变化的特性,现有干扰对消系统快速收敛和快速跟踪的能力不足;第三,军用收发信机 呈现宽带化的现状和趋势,干扰对消系统应对宽带干扰信号的能力不足。第四,高灵敏度接 收机面临大功率干扰源,干扰对消系统难以提供足够的干扰抑制能力,将干扰抑制到接收 机底噪附近;第五,利用耦合器对干扰信号取样,通常伴随插入损耗,降低射频发射机的有 效工作范围。 为解决上述问题,申请号为CN201811155774.6的专利申请提出了一种数字域干扰 重构的射频对消装置及其方法,该装置包括数字延时、干扰重构模型、系数辨识算法、数模 转换器、对消链路和合路器等模块,其中数字延时、干扰重构模型和系数辨识算法运行在数 字信号处理器件上;对消方法包括以下步骤:根据发射链路、无线信道和对消链路特性建立 干扰重构模型;根据收发数字信号实现数字延时来使收发数字信号进行对齐;利用数字延 时数据和接收数据实现模型系数的静态系数辨识;该技术解决了宽带干扰信号对消能力的 问题,但存在的技术问题是需要介入射频收发信机的数字基带部分。 另外,申请号为CN201010538860 .2的专利提出了一种共址耦合干扰跟踪对消装 置,由定向耦合器、电调陷波器和锁相环电路构成;所述的定向耦合器输入端与接收天线相 联接,定向耦合器输出端与电调陷波器输入端相联接,定向耦合器耦合端与锁相环电路输 入端相联接;所述的电调陷波器输出端与接收机相联接,电调陷波器控制端与锁相环电路 5 CN 111585594 A 说 明 书 2/9 页 输出端相联接;该技术无需介入射频收发信机的数字基带部分,但存在的问题是难以适用 于宽带干扰,收敛速度较慢等。 另有申请号为CN201320001505.0的专利提出了一种自适应宽带干扰对消装置,该 装置包括第一耦合器、时延器和自适应对消系统,其中自适应对消系统包括:移相器、可调 衰减器、相关器、耦合器和合成器;自适应对消系统的可调衰减器分为第一、第二可调衰减 器;相关器分为第一、第二相关器;耦合器分为第二、第三耦合器;该技术解决了宽带干扰信 号对消的问题,但存在的问题是干扰信号取样伴随插入损耗,对消比和收敛速度有限。 由上述分析可知,现有技术并不能满足军用平台收发信机电磁兼容的苛刻要求, 因此,亟需一种基于级联数字控制方法的干扰对消装置及方法来解决现有的技术问题。

技术实现要素:

针对上述现有技术的不足,本发明的目的是提供一种基于级联数字控制方法的干 扰对消装置及方法,将数字射频存储技术引入干扰对消系统,对干扰源信号(即参考信号) 进行了数字化,解决了干扰对消系统受制于无法介入发信机数字基带部分的问题;采用数 字控制模拟对消分系统和数字控制数字对消分系统对共址干扰进行两级级联对消处理,实 现对宽带共址干扰快速、深度对消。 本发明是通过以下技术方案予以实现的。 一种基于级联数字控制方法的干扰对消装置,包括数字射频存储分系统、数字控 制模拟对消分系统及数字控制数字对消分系统;所述数字射频存储分系统的输入端接收干 扰源信号,对干扰源信号进行数字化处理,并估计系统延迟匹配误差,进行延迟匹配处理; 所述数字控制模拟对消分系统及数字控制数字对消分系统形成对共址干扰信号的两级级 联对消处理模式,对共址干扰信号实现抑制。 进一步的,所述数字射频存储分系统包括:第一射频接收链路、第一射频发射链 路、数字延迟模块和延迟匹配控制单元; 所述第一射频接收链路接收干扰源信号并将干扰源信号转换成数字信号以形成 数字基带信号,将第一射频接收链路生成的数字基带分别输送至数字延迟模块和延迟匹配 控制单元; 所述延迟匹配控制单元根据两个输入信号之间的互相关函数估计系统延迟匹配 误差,而后将上述系统延迟匹配误差输送至数字延迟模块; 所述数字延迟模块根据延迟匹配控制单元输入的系统延迟匹配误差对干扰源信 号进行延迟处理,将处理后的信号输送至第一射频发射链路; 所述第一射频发射链路的输出端设置有发射输出端口,所述发射输出端口的输出 端设置有发射天线,经过延时匹配处理的干扰源信号被所述第一射频发射链路转换为模拟 信号并通过发射输出端口及发射天线发射出去。 进一步的,所述数字控制模拟对消分系统在数字信号域对共址干扰信号实现控制 及在模拟信号域对共址干扰信号实现抑制,其包括第二射频接收链路、第二射频发射链路、 模拟对消数字控制模块和合路器; 所述第二射频接收链路将从合路器输出的模拟射频信号转化为数字基带信号,并 输送至模拟对消数字控制模块及所述延迟匹配控制单元; 6 CN 111585594 A 说 明 书 3/9 页 所述模拟对消数字控制模块为一个有限长单位冲激响应自适应滤波器; 所述模拟对消数字控制模块接收第一射频接收链路生成的数字基带信号及第二 射频接收链路的输出的数字基带信号,运算后形成第一级干扰对消信号的数字基带信号, 并将第一级干扰对消信号的数字基带信号输送至第二射频发射链路; 第二射频发射链路将第一级干扰对消信号的数字基带信号转化为第一级干扰对 消信号的模拟射频信号,并输送至合路器; 所述合路器通过接收输入端口及接收天线接收所述发射天线引起的共址干扰信 号; 合路器将第一级干扰对消信号的模拟射频信号与共址干扰信号进行叠加,从而抵 消一部分共址干扰信号; 所述第二射频接收链路、第二射频发射链路、模拟对消数字控制模块和合路器形 成闭环运算系统,对共址干扰信号进行不断的迭代抵消。 进一步的,所述数字控制数字对消分系统在数字信号域对共址干扰信号实现控制 和抑制;其包括第三射频发射链路和数字控制数字对消模块; 所述数字对消数字控制模块由线性滤波器、无记忆非线性滤波器及线性滤波器按 照先后顺序级联构成; 数字对消数字控制模块的一输入端接收第二射频接收链路输出的数字基带信号; 数字对消数字控制模块的另一输入端接收第一射频接收链路输出的数字基带信 号; 数字对消数字控制模块对两个输入信号运算后,完成第二级干扰对消,产生干扰 对消后的数字基带信号; 第三射频发射链路的输入端与数字对消数字控制模块的输出端连接,将数字对消 数字控制模块输出的第二级干扰对消后的数字基带信号转化为模拟射频信号; 所述第三射频发射链路的输出端设置有接收输出端口,所述模拟射频信号通过接 收端口被输出。 基于级联数字控制方法的干扰对消装置的对消方法,包括以下步骤: 步骤S1,系统初始化;令数字控制模拟对消分系统的输出信号为零,此时第二射频 发射链路的输出信号也近似为零,数字控制模拟对消分系统暂时不发挥抑制共址干扰的作 用; 步骤S2,数字射频存储分系统中的延迟匹配控制单元估计系统延迟匹配误差,并 进行延迟匹配处理; 步骤S3,利用数字控制模拟对消分系统进行第一级干扰对消处理; 步骤S4,利用数字控制数字对消分系统进行第二级干扰对消处理; 步骤S5,第三射频发射链路将对消信号的数字基带信号转化为模拟射频信号,并 通过接收输出端口输出。 进一步的,步骤S1中,初始化数字射频存储分系统中数字延迟模块的延迟时间 τDRFM为τ0: τ0=τRX1 τDA τTX3 其中,τRX1为第一射频接收链路模块的延迟,τDA为模拟对消数字控制模块的延迟, 7 CN 111585594 A 说 明 书 4/9 页 τTX3为第二射频发射链路模块的延迟。 进一步的,步骤S2中,系统延迟匹配误差是干扰源信号到达合路器两个输入端口 的时间差Δτ: Δτ=τ0-τ1 其中τ1=τRX1 τDRFM τTX1 τ耦合;τTX1为第一射频发射链路的延迟,τ耦合为干扰从发射天 线耦合到接收天线的传输延迟; 更进一步的,通过计算第一射频接收链路输出信号和第二射频接收链路输出信号 的互相关函数得到上述两个信号的时间差Λτ,因为Λτ=τRX1-(τRX1 τDRFM τTX1 τ耦合 τ合路器 τRX2),所以Δτ=Λτ τDA τTX3-τ合路器-τRX2;其中,τ合路器为合路器的延迟;τRX2为第二射频接收链 路的延迟;上式中,τDA,τTX3,τ合路器,τRX2是本发明装置已知的常数值,因此得到Λτ的估计值即 可得到Δτ的估计值;得到系统延迟匹配误差Δτ的估计值后,调整数字延迟模块的延迟时 间τDRFM使Δτ为零。 进 一 步 的 ,步 骤 S 3 中 ,模 拟 对 消 数 字 控 制 模 块 的 输 出 信 号 为 其中,n表示数字信号的采样次序;d(n)为第二射频接收链路 输出信号,作为自适应滤波器的期望信号;u(n)为第一射频接收链路输出信号,作为自适应 滤波器的多抽头输入; 为n-1时刻自适应滤波器的系数。 进一步的,步骤S4中,所述数字对消数字控制模块由线性滤波器l(.)、无记忆非线 性滤波器c(.)及线性滤波器g(.)按照先后顺序级联构成;令e(n)为数字控制数字对消分系 统的输出信号,v1(n) ,v2(n)分别为非线性滤波器c(.)的输入和输出,那么, e(n)=d(n)-y(n) 其中,ψ(n)为数字控制数字对消系统的输入信号;v1(n)为线性滤波器l(.)的输出 信号,亦即非线性滤波器c(.)的输入信号;l(i) ,i=0,...,Ml-1为线性滤波器l(.)的系数; Ml为线性滤波器l(.)的长度;v2(n)为非线性滤波器c(.)的输出信号,亦即线性滤波器g(.) 的输入信号;c(p) ,p=0,...,P为线性滤波器c(.)的系数;P为非线性滤波器c(.)的最大阶 数;y(n)为线性滤波器g(.)的输出信号;g(i) ,i=0,...,Mg-1为线性滤波器g(.)的系数;Mg 为线性滤波器g(.)的长度。 与现有技术相比,本发明的有益效果在于: 1)本发明首次将数字射频存储技术引入干扰对消系统,对干扰源信号(即参考信 号)进行了数字化处理,解决了干扰对消系统受制于无法介入发信机数字基带部分的问题, 使数字控制模拟对消技术应用到共址干扰抑制具备了现实可行性; 2)本发明利用数字射频存储技术中数字延迟模块及延迟匹配控制技术,对干扰源 8 CN 111585594 A 说 明 书 5/9 页 信号进行了数字延迟,解决了数字控制模拟对消技术在抑制共址干扰的应用中无法实现延 迟匹配的问题,因而使数字控制模拟对消技术应用到共址干扰抑制具备了现实可行性; 3)本发明利用数字射频存储技术,实现了无插损的参考取样,解决了基于耦合器 的传统参考取样过程损失发信机发射功率、因而降低发信机最大工作距离的问题; 4)本发明采用两级级联干扰对消的策略和数字控制的方式,干扰对消算法灵活性 非常强,有利于提高干扰对消比、干扰对消收敛速度和跟踪速度及干扰对消带宽等,适用于 在大功率宽带干扰中恢复微弱有用信号。 附图说明 图1为本发明的原理框图; 图2为本发明第一发射链路的组成结构图; 图3为本发明第一射频接收链路的组成结构图; 图4为本发明使用方法示意图;