技术摘要:

本发明提供一种解决STT‑RAM缓存写失败的方法,在纠错码的纠错能力与存储代价之间取得平衡。本发明包括如下步骤:S1、发起写数据操作时,确定将写的目标缓存块后,读出目标缓存块的旧数据按位与新数据按位比较后,计算统计当前数据位对应的STT‑RAM单元将发生0到1的切换 全部

背景技术:

相比于传统的SRAM存储器,Spin Transfer Torque RAM(STT-RAM)作为一种新型 存储器具有静态能耗低、存储密度高、读速度快以及与CMOS技术兼容性好等优点,因此STT- RAM有望成为计算机的下一代片上缓存。但STT-RAM也存在明显的劣势,其中包括写失败。 STT-RAM存储单元主要是磁隧道结(MTJ),其中主要包括参照层和自由层。参照层的磁化方 向水平固定,而自由层的磁化方向要么与参照层同向,要么反向。参照层与自由层的磁化方 向反向或者同向时,磁隧道结呈现低或高两种电阻态,分别表示逻辑值0或1。因此,向STT- RAM单元写入数据,本质上改变自由层的磁化方向。 写数据时,如果新数据与STT-RAM存储单元原来的数据相异,则需要改变自由层的 磁化方向。主要是向STT-RAM单元注入写电流Iwrite,并保持twrite时间来改变自由层的磁化 方向,但磁化方向有可能不改变,即写操作存在一定的失败可能性,这种现象称为写失败。 单个STT-RAM单元写失败的概率很小,但写入缓存块的数据与旧数据相异的数据位数较多 时,则可能发生写失败的数据位数也会较多。另外,STT-RAM存储单元从逻辑值0到1的写失 败发生概率要比从1到0的写失败大100倍。因此,缓存块的写失败数据位数与新旧数据之间 从逻辑值0到1的切换的数据位数成正比。 写失败的传统解决方式是采用纠错码。只要缓存块中写失败的错误数据位数不超 过纠错码的纠错能力,则写操作成功;如果要写入的新旧数据之间相异的数据位数很多,则 缓存块中出现的写失败错误位数过多,纠错码无法纠正错误数据,影响程序的正常运行。导 致上述问题的主要原因是缓存块的纠错码数据位数固定,纠错能力恒定;而缓存块的新旧 数据相异位数存在明显差异。不同的缓存块,不同的写更新状态,需要设置纠错能力不同的 纠错码。如果都采用强纠错能力的纠错码,则存储代价过大;如果都采用默认纠错能力的纠 错码,则纠错能力不足。

技术实现要素:

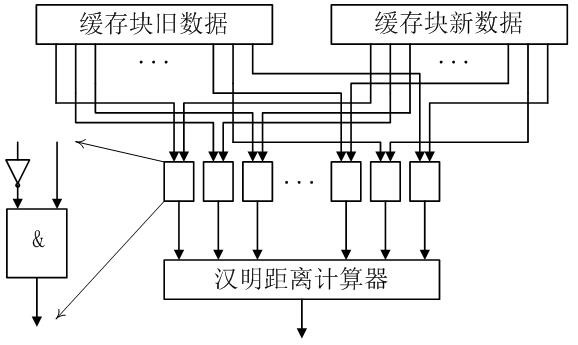

本发明的目的在于克服现有技术中存在的上述不足,而提供一种解决STT-RAM缓 存写失败的方法,在纠错码的纠错能力与存储代价之间取得平衡。 本发明解决上述问题所采用的技术方案是:一种解决STT-RAM缓存写失败的方法, 其特征在于:包括如下步骤: S1、发起写数据操作时,确定将写的目标缓存块后,读出目标缓存块的旧数据按位 与新数据按位比较后,计算统计当前数据位对应的STT-RAM单元将发生0到1的切换的总数 据位数n; S2、比较n与阀值Kth,如果n大于Kth,则采用扩展纠错码进行纠错,如果n小于等于 Kth,则采用默认纠错码进行纠错; 4 CN 111580750 A 说 明 书 2/4 页 S3、写缓存块时,设置目标缓存块标签的标志位,标识目标缓存块的纠错码类型; S4、读取缓存块数据时,同时读取缓存块标签的标志位,根据标志位确定所采用的 纠错码类型,将缓存块发往对应的纠错码解码器纠错。 本发明计算统计当前数据位对应的STT-RAM单元发生0到1的切换的总数据位数n 的步骤为:读取目标缓存块中的旧数据,取反该旧数据,再与对应的新数据按位进行与运 算,如果输出值为1,表示当前数据位对应的STT-RAM单元发生0到1的切换,每一位的输出再 作为汉明距离计算器的输入,汉明距离计算器的输出就是当前数据位对应的STT-RAM单元 发生0到1的切换的总数据位数n。整个计算电路是组合电路,所以不引入额外延时。 本发明阀值Kth的计算步骤为:计算阀值Kth时,系统允许缓存块写失败发生的概率 上限为e,缓存块纠错码的纠错能力为k个数据位,缓存块出现写失败数据位数为m,m大于k 时,当前的写操作失败,因此写操作的失败概率为P(m≥(k 1)),要满足: P(m≥(k 1))