技术摘要:

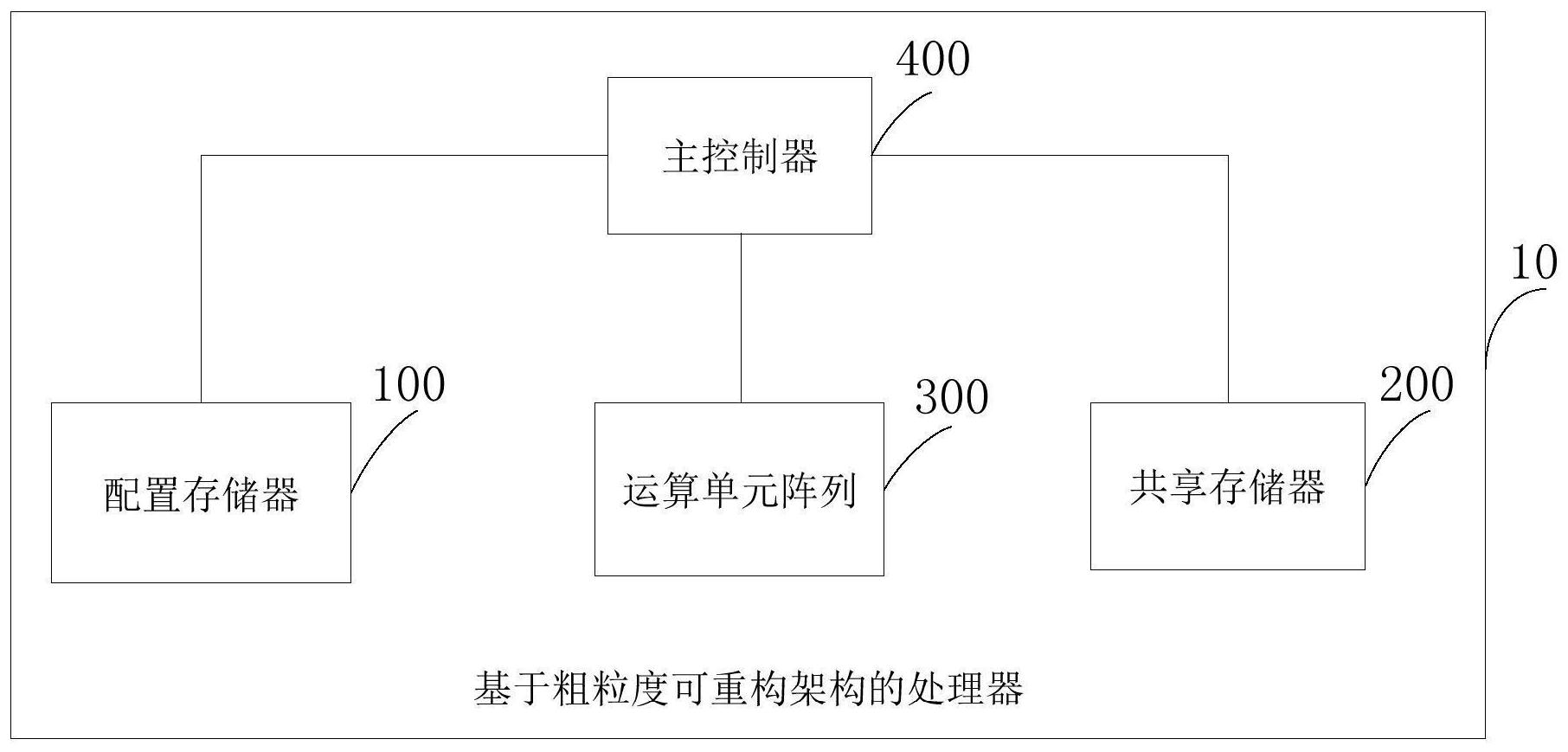

本发明公开了一种基于粗粒度可重构架构的处理器,用于数字信号处理,处理器包括:配置存储器,用于存储配置信息;运算单元阵列,包括8行8列的64个运算单元,运算单元用于实现数字信号处理的计算任务;共享存储器,用于缓存运算单元计算的中间数据与计算结果;主控制器 全部

背景技术:

随着集成电路,计算机技术和软件技术的飞速发展,数字信号应用的实现正在迅 速变化,这一变化对系统的信号处理能力提出更高要求,在保持高性能的同时,系统还必须 考虑不同需求的信号处理功能,这意味着系统应该同时具有较好的灵活性。 在实现数字信号处理应用程序时,可以考虑的硬件解决方案通常是GPP(General- Purpose Processor,通用处理器),DSP(Digital Signal Processor,数字信号处理器), ASIC(Application Specific Integrated Circuit,专用集成电路)和FPGA(Field Programmable Gate Array,现场可编程门阵列)。GPP在服务器和台式计算机系统中很常 见,它具有很高的灵活性,编程后可用于多种应用,非常通用,相应的NRE(Non-Recurring Engineering,一次性工程费用)成本很低,但其多功能性也意味着硬件并未针对特定算法 进行优化,因此其性能通常很差。DSP是专用的数字信号处理器,具有丰富的可编程性,硬件 优化了数字信号处理过程,因此在执行数字信号处理时,DSP的性能比GPP稍好。ASIC是用于 特定应用的电路,电路的内部结构根据应用的特性和要求进行了优化,因此性能通常是最 好的。然而,在完成ASIC电路掩模之后不能改变电路的结构,灵活性受到限制,并且ASIC昂 贵且不灵活,并且很少在系统中使用。并且,其NRE成本非常高,这对于数字信号处理系统而 言非常昂贵。FPGA是一种具有丰富逻辑资源的半定制电路。它可以通过编程来完成某个应 用程序来更改逻辑资源之间的互连。由于其丰富的硬件资源可以支持高度并行计算,因此 其性能更好。由于性能不佳,GPP难以满足数字信号处理应用程序的高性能要求。因此,较常 见的解决方案是DSP和FPGA。 然而,随着应用需求的增加,DSP和FPGA的性能变得越来越难以满足需求,对高性 能、灵活性和低成本硬件实施解决方案的需求越来越迫切。

技术实现要素:

本发明旨在至少在一定程度上解决相关技术中的技术问题之一。 为达到上述目的,本发明提出了一种基于粗粒度可重构架构的处理器,用于数字 信号处理,所述处理器包括:CM(ContextMemory,配置存储器),用于存储配置信息;PEA (Processing Element Array,运算单元阵列),包括排列为8行8列的64个PE(Processing Element,运算单元),所述运算单元用于实现所述数字信号处理的计算任务;SM(Shared Memory,共享存储器),用于缓存所述运算单元计算的中间数据与计算结果;主控制器,用于 启动所述处理器,将所述配置信息传输至所述运算单元阵列,以完成对所述运算单元阵列 的功能配置,并根据所述配置信息将所述运算单元阵列配置为两种不同的BU (ButterflyUnit,蝶形运算单元),以使所述蝶形运算单元实现蝶形运算。 3 CN 111581148 A 说 明 书 2/5 页 上述提出的基于粗粒度可重构架构的处理器实现数字信号处理,利用运算单元阵 列的计算并行性,增强了数字信号处理中算法实现的性能,简单易实现。 可选地,当上述计算任务为基4时分1024点的FFT(Fast Fourier Transform,快速 傅里叶变换算法)时,所述计算任务共分为5级,所述运算单元阵列进一步用于每级取4个点 进行一次蝶形运算其中,第一级依次取第0 i、第256 i、第512 i和第768 i点的数据进行蝶 形运算;第二级依次取0 j、第64 j、128 j和第192 j点的数据进行蝶形运算,第三级依次取 0 m、第16 m、32 m和第48 j点的数据进行蝶形运算,第四级依次取0 n、第4 n、8 n和第12 n 点的数据进行蝶形运算,第五级依次取0 p、第1 p、2 p和第3 p点的数据进行蝶形运算,其 中,i=0~255,j=0~63,m=0~15,n=0~7,p=0~3,且i,j,m,n,p为整数。 可选地,上述两种不同的蝶形运算单元为第一蝶形运算单元与第二蝶形运算单 元,其中,所述第一蝶形运算单元包括排列为4行2列的8个所述运算单元,排列为4行2列的8 个所述运算单元在相同时钟节拍输入数据以及在不同时钟节拍输出数据;所述第二蝶形运 算单元包括排列为2行4列的8个所述运算单元,排列为2行4列的8个所述运算单元在不同时 钟节拍输入数据以及在相同时钟节拍输出数据。 可选地,上述共享存储器划分为多个共享子存储器子区间,所述共享子存储器子 区间包括一组独立的读写端口,所述共享存储器子区间用于存储所述运算单元计算的中间 数据与计算结果。 本发明附加的方面和优点将在下面的描述中部分给出,部分将从下面的描述中变 得明显,或通过本发明的实践了解到。 附图说明 本发明上述的和/或附加的方面和优点从下面结合附图对实施例的描述中将变得 明显和容易理解,其中: 图1为本发明一实施例的基于粗粒度可重构架构的处理器结构示意图; 图2为本发明一实施例的基4时分1024点的快速傅里叶变换算法数据依赖关系示 意图; 图3为本发明一实施例的通过运算单元阵列中的8个运算单元实现基4时分1024点 的快速傅里叶变换算法示意图; 图4为本发明一实施例的在配置后的运算单元阵列上实现基4时分1024点的快速 傅里叶变换算法示意图; 图5为本发明一实施例的第一蝶形运算单元结构示意图; 图6为本发明一实施例的第二蝶形运算单元结构示意图; 图7为本发明一实施例的D0~D15的数据端口在64个周期内访问共享存储器子区 间的关系示意图。