技术摘要:

本发明公开一种平坦化方法,涉及半导体制造技术领域,以解决在平坦化过程中,由于研磨垫与多孔膜质之间的摩擦,在多孔膜质表面形成裂纹,降低产品良率的问题。该平坦化方法包括:提供一具有折叠部的基底,基底的表面具有位于折叠部的多孔膜质;去除多孔膜质,获得形成 全部

背景技术:

在动态随机存储器(Dynamic Random Access Memory,缩写为DRAM)的制作过程 中,因单元区域(Cell)形成有电容,使得单元区域(Cell)与核心区域(Peri)之间具有较高 的段差。为了后续的图案化工艺,需要在单元区域(Cell)和核心区域(Peri)沉积氧化物 (Oxide),以形成介质层,并采用化学机械研磨工艺(Chemical Mechanical Polishing,缩 写为CMP)对介质层进行平坦化。 然而,在单元区域(Cell)和核心区域(Peri)沉积氧化物(Oxide)后,由于单元区域 (Cell)与核心区域(Peri)之间存在较高的段差,且存在阶梯覆盖差异问题,因此,在对应单 元区域(Cell)和核心区域(Peri)的交界区域,氧化物层容易出现多孔膜质。在此基础上,采 用化学机械研磨(CMP)工艺对介质层进行平坦化的过程中,由于研磨垫与多孔膜质之间的 摩擦,会在多孔膜质的表面产生裂纹,降低产品良率。即使在研磨头与多孔膜质的研磨面加 入研磨液,效果也并不理想。

技术实现要素:

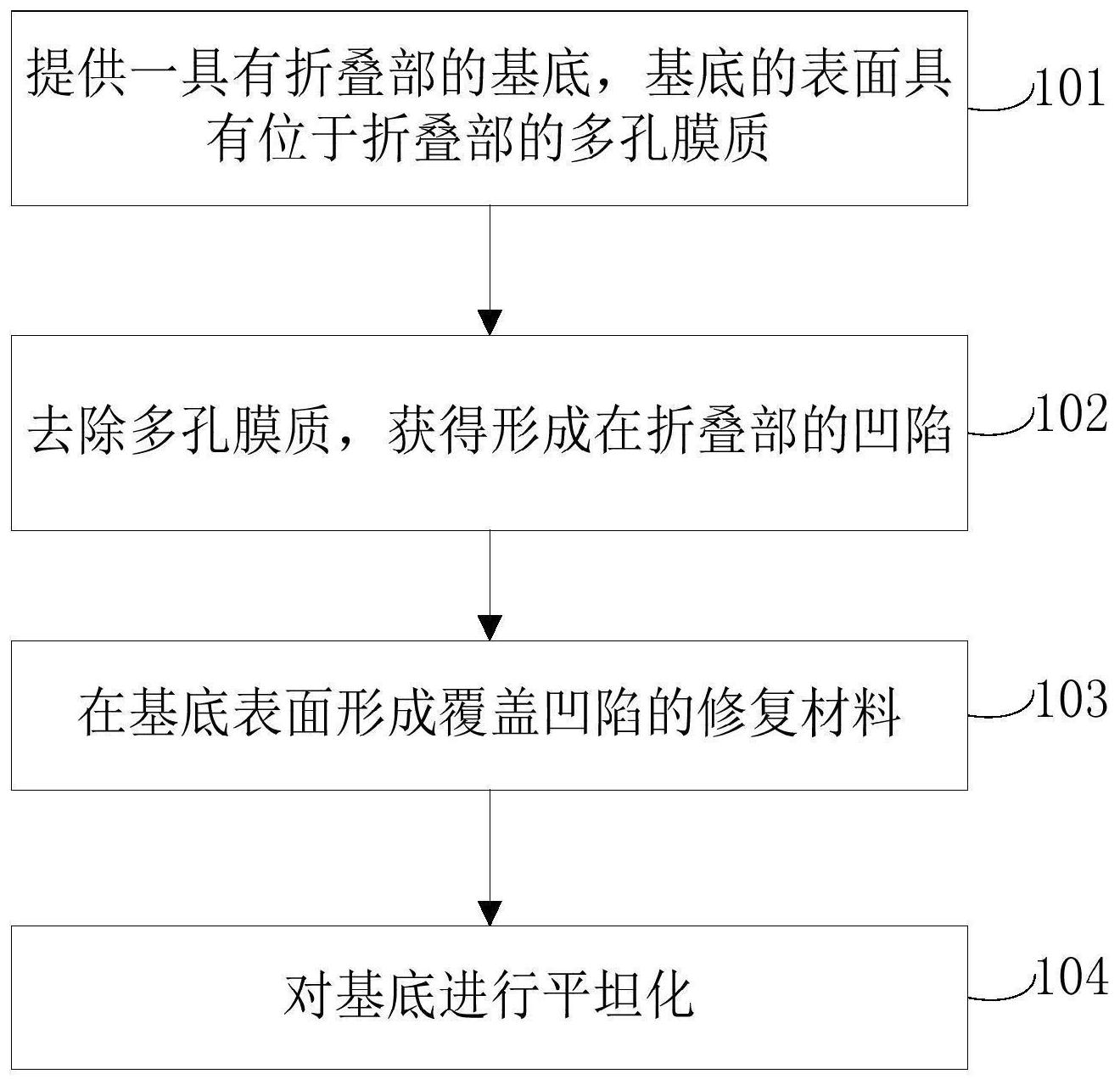

本发明的目的在于提供一种平坦化方法,以降低平坦化后介质层产生裂纹的可能 性。 为了实现上述目的,本发明提供一种平坦化方法。该平坦化方法包括:提供一具有 折叠部的基底,基底的表面具有位于折叠部的多孔膜质;去除多孔膜质,获得形成在折叠部 的凹陷;在基底表面形成覆盖凹陷的修复材料;对基底进行平坦化。 优选地,去除多孔膜质,包括:采用刻蚀方式去除多孔膜质。 优选地,刻蚀方式包括:干法刻蚀和/或湿法刻蚀。 优选地,修复材料的致密性大于多孔膜质的致密性。 优选地,提供一具有折叠部的基底,包括:提供一表面具有裂纹的衬底;在衬底的 非裂纹位置的表面形成介质层。 优选地,介质层位于衬底裂纹的一侧。 优选地,介质层的厚度为 优选地,基底具有台阶状表面,台阶状表面包括高台阶部和低台阶部,折叠部位于 低台阶部靠近高台阶部的位置。 优选地,高台阶部和低台阶部的高度差为 优选地,基底具有与高台阶部相应的单元区域以及与低台阶部相应的核心区域。 与现有技术相比,本发明提供的平坦化方法,由于基底的表面具有位于折叠部的 多孔膜质,去除多孔膜质后,可在原来折叠部具有多孔膜质的位置形成凹陷。此时,相比于 原来的折叠部的折叠程度,凹陷可以使得折叠部的折叠程度变得比较缓和,提升折叠部的 3 CN 111554576 A 说 明 书 2/5 页 阶梯覆盖特性。在此基础上,在基底表面形成修复材料,可以确保修复材料形成的膜层致密 性有所增加,使得后续平坦化基底时,降低基底表面形成裂纹的可能性。例如:当基底含有 介质层时,该介质层具有折叠部,采用本发明提供的平坦化方法对介质层进行处理,可以有 效降低介质层平坦化后产生裂纹的可能性。 附图说明 此处所说明的附图用来提供对本发明的进一步理解,构成本发明的一部分,本发 明的示意性实施例及其说明用于解释本发明,并不构成对本发明的不当限定。在附图中: 图1为现有技术中由于高段差引起的在介质层折叠部形成多孔膜质的示意图; 图2为现有技术中在多孔膜质表面经过平坦化形成裂纹的示意图; 图3为现有技术中在多孔膜质表面经过平坦化形成裂纹的实物图; 图4为本发明实施例提供的平坦化方法的流程图; 图5为本发明实施例提供的具有自带的台阶状表面的基底; 图6为本发明实施例提供的在裂纹一侧形成介质层的基底; 图7为本发明实施例提供的多孔膜质示意图; 图8为本发明实施例提供的在衬底上形成介质层的基底示意图; 图9为本发明实施例提供的去除多孔膜质后的基底示意图; 图10为本发明实施例提供的在基底表面形成修复材料后的基底示意图; 图11为本发明实施例提供的平坦化后的基底示意图。 其中,图1-图2中:1.电容,2.介质层,21.高台阶部,22,低台阶部; 图5-图10中:1.电容,2.介质层,10.基底,110.高台阶部,120低台阶部,100.衬底, 20.修复材料。