技术摘要:

本发明提供了一种三维存储器的制作方法。该制作方法包括以下步骤:提供具有存储器阵列的第一衬底,第一衬底的具有存储器阵列的一侧形成有绝缘介质层以及位于绝缘介质层中的刻蚀停止层;在绝缘介质层中形成贯穿至刻蚀停止层的第一通孔;去除刻蚀停止层,并在第一通孔和 全部

背景技术:

随着对集成度和存储容量的需求不断提高,3D NAND存储器应运而生。3D NAND存 储器大大节省了硅片面积,降低制造成本,增加了存储容量。 在3D NAND存储器结构中,采用垂直堆叠多层数据存储单元的方式,实现堆叠式的 3D NAND存储器结构,然而,其他的电路例如解码器(decoder)、页缓冲(page buffer)和锁 存器(latch)等,这些外围电路都是CMOS器件形成的,CMOS器件的工艺无法与3D NAND器件 集成在一起。目前工艺中,分别采用不同的工艺形成具有3D NAND存储器阵列的晶圆以及具 有外围电路的晶圆,然后通过键合技术将两者键合在一起,键合后通过TSC技术实现硅晶圆 背面绕线,TSC技术是一种完全穿过硅晶圆的垂直电连接,通过直接形成贯穿硅晶圆的接触 点(通常称为贯穿硅触点),使其通过导电通道与键合CMOS器件的接触点电连接,从而通过 显著降低芯片复杂度和总体尺寸的内部布线来提供垂直对准器件的互连,与传统封装技术 相比,TSC技术能够提供更高的器件互连密度以及更短器件互连长度。 实际工艺中,形成的上述贯穿硅触点的端部需要完全包裹与CMOS器件连接的导电 通道端部,且贯穿硅触点外侧还需要形成一定厚度的隔离层,通过将贯穿硅触点与衬底隔 离以防止漏电(leakage),上述情况导致了贯穿硅触点端部的截面尺寸需要大于上述导电 通道端部的截面尺寸。然而,为了形成上述贯穿硅触点,需要先在衬底中形成贯穿的接触 孔,在该步骤后通常还有一道刻蚀后处理(PET)的工序,为了保证导电通道蚀刻过程中硅衬 底的损失,这道工艺对硅的选择比很高,这可能会导致上述导电通道端部的截面尺寸扩大 30~50nm,从而导致在后续通过TSC技术实现硅晶圆背面绕线的工艺中,需要对贯穿硅触点 端部的截面尺寸进行调整,使得工艺难度增大。

技术实现要素:

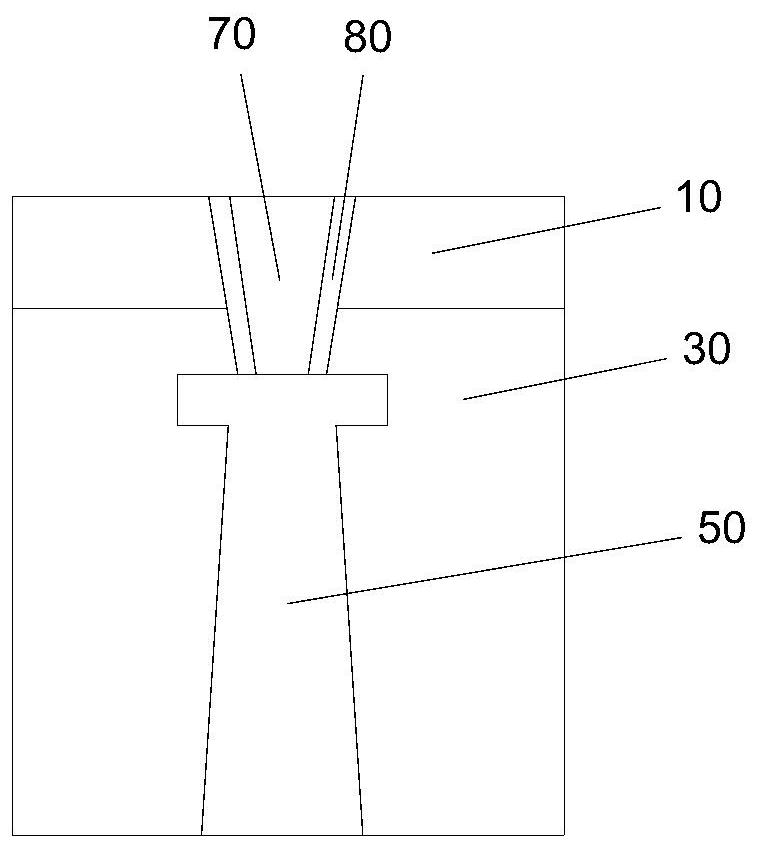

本发明的主要目的在于提供一种三维存储器的制作方法,以解决现有技术中硅晶 圆背面绕线的工艺中需要对贯穿硅触点端部的截面尺寸进行调整而导致工艺难度增大的 问题。 为了实现上述目的,根据本发明的一个方面,提供了一种三维存储器的制作方法, 包括以下步骤:提供具有存储器阵列的第一衬底,第一衬底的具有存储器阵列的一侧形成 有绝缘介质层以及位于绝缘介质层中的刻蚀停止层;在绝缘介质层中形成贯穿至刻蚀停止 层的第一通孔;去除刻蚀停止层,并在第一通孔和去除刻蚀停止层的区域中形成第一导电 通道;提供具有CMOS电路的第二衬底,将CMOS电路与第一衬底的存储器阵列键合;自远离存 储器阵列的一侧形成贯穿第一衬底并与第一导电通道连接的贯穿触点。 进一步地,在第一衬底上沉积绝缘材料,以形成绝缘介质层,在沉积绝缘材料的过 程中形成刻蚀停止层。 4 CN 111599817 A 说 明 书 2/6 页 进一步地,存储器阵列包括核心存储区和台阶区,台阶区具有与核心存储区连接 的台阶结构,在台阶结构远离核心存储区一侧的形成刻蚀停止层。 进一步地,形成绝缘介质层和刻蚀停止层的步骤包括:在第一衬底上形成堆叠结 构,堆叠结构包括栅极结构和栅极间介质层,栅极结构和栅极间介质层沿远离第一衬底的 方向交替层叠设置;刻蚀栅极结构和栅极间介质层,以将堆叠结构的一端形成台阶结构;在 第一衬底上沉积绝缘材料,以形成绝缘介质层,在沉积绝缘材料的过程中形成刻蚀停止层。 进一步地,第一通孔在刻蚀停止层上的投影面积小于刻蚀停止层的横截面积。 进一步地,形成第一通孔的步骤包括:在第一衬底上形成覆盖绝缘介质层的第一 接触层;顺序刻蚀第一接触层和绝缘介质层,以在第一接触层中形成第一接触孔,并在绝缘 介质层中形成贯穿至刻蚀停止层的第一通孔,第一通孔与第一接触孔连通。 进一步地,在去除刻蚀停止层的步骤之后,在第一通孔和去除刻蚀停止层的区域 中形成第一导电通道,并在第一接触孔中形成与第一导电通道连接的第一接触点。 进一步地,在刻蚀第一接触层和绝缘介质层的步骤中,在第一接触层中形成第二 接触孔,并在绝缘介质层中形成贯穿至台阶结构的第二通孔,以使第二通孔与第二接触孔 连通,在将CMOS电路与存储器阵列键合的步骤之前,制作方法还包括:在第二通孔中形成第 二导电通道,并在第二接触孔中形成与第二导电通道连接的第二接触点。 进一步地,将CMOS电路与存储器阵列键合的步骤包括:在第二衬底上形成覆盖 CMOS电路的第二接触层;在第二接触层中形成贯穿至CMOS电路的互连接触孔;在互连接触 孔中形成互连接触点,以使互连接触点与CMOS电路连接;将互连接触点分别与第一接触点 和第二接触点键合。 进一步地,形成贯穿触点的步骤包括:形成贯穿第一衬底并与第一导电通道连接 的第三接触孔;形成覆盖第三接触孔侧壁的隔离层;在第三接触孔中形成贯穿触点,以使隔 离层包裹贯穿触点。 进一步地,第一导电通道具有与贯穿触点接触的导电面,贯穿触点在导电面上的 投影面积小于导电面的面积。 进一步地,刻蚀停止层的材料包括氮化硅。 应用本发明的技术方案,提供了一种三维存储器的制作方法,该制作方法在形成 存储器阵列的过程中同时形成一层刻蚀停止层,然后在刻蚀停止层上覆盖绝缘介质层,并 在绝缘介质层中形成贯穿至刻蚀停止层的第一通孔,去除刻蚀停止层后在第一通孔和去除 刻蚀停止层的区域中形成第一导电通道,在将CMOS电路与存储器阵列键合后,形成与第一 导电通道连接的贯穿触点,从而通过先形成刻蚀停止层,再将上述刻蚀停止层去除并在其 中形成导电通道的端部,使得导电通道端部与衬底之间能够通过部分绝缘介质层实现隔 离,进而在背面绕线的工艺中无需通过调整贯穿触点的尺寸来实现贯穿触点对导电通道端 部完全包裹,就能够有效防止导电通道与衬底之间的漏电,降低了工艺难度。 附图说明 构成本发明的一部分的说明书附图用来提供对本发明的进一步理解,本发明的示 意性实施例及其说明用于解释本发明,并不构成对本发明的不当限定。在附图中: 图1示出了在本申请实施方式所提供的三维存储器的制作方法中,在第一衬底的 5 CN 111599817 A 说 明 书 3/6 页 具有台阶区和核心存储区的表面上覆盖绝缘介质层后的基体剖面结构示意图; 图2示出了在图1中所示的绝缘介质层中形成贯穿至刻蚀停止层的第一通孔后的 基体剖面结构示意图; 图3示出了去除图2中所示的刻蚀停止层后的基体剖面结构示意图; 图4示出了在图3中所示的第一通孔和去除刻蚀停止层的区域中形成第一导电通 道后的基体剖面结构示意图; 图5示出了将图4中所示的基体翻转后的基体剖面结构示意图; 图6示出了形成贯穿图5中所示的第一衬底并与第一导电通道连接的第三接触孔 后的基体剖面结构示意图; 图7示出了在图6中所示的第一接触孔中形成贯穿触点后的基体剖面结构示意图。 其中,上述附图包括以下附图标记: 10、第一衬底;20、刻蚀停止层;30、绝缘介质层;40、第一通孔;50、第一导电通道; 60、第三接触孔;70、贯穿触点;80、隔离层。